# Reconfigurable Down Sampling Channelizer for SDR Receiver Using FPGA

# Majid S. Naghmash, Hazim Salah Abdulsatar, Tahseen Flaih Hasan

Abstract—This paper presents, the design and implementation of reconfigurable down sampling the IF band frequency to baseband in Software Defined Radio (SDR) receiver. To enhance both the integration and adaptation of multiple communication standards like GSM, CDMA and WCDM systems, the selection of channel in SDR technology require to achieve relaxing on chip at baseband. The wireless and mobile systems classically utilize a channelizer to extract the desired band for more processing in baseband. Down conversion in frequency domain requires less computation and complexity to provide the idea of minimum power consumption as current user demand. In the low power design and efficient FPGA area implementation, the cascaded digital filter structure is required to convene multi standards specifications in wide and narrow band systems. Many type of digital filter has been decomposition to implement this filter as well as a lot of software from Mathworks and Xilinx is used. A number of experiments and investigation are given to estimate the results of FPGA design for filter structure. The nonappearance of error in the design steps shows an important improvements in the filter implementation results to enhance the conventional design.

Index Terms— Reconfigurable filter, Down Sampling, SDR Receiver, FPGA.

### I. INTRODUCTION

The technology of Software Defined Radio (SDR) offer software manage for diversity of modulation techniques in wide or narrowband process [1]. In addition, SDR is provide flexibility and permit to multiple communication protocols to animatedly perform on the same hardware, thus dropping the cost. The filtering, demodulation and decoding processes in the receivers could be reconfigured adaptively at run time which will reduce the cost and power consumption for end user [2]. The analogue to digital converter (A/D) in SDR receivers is moved as closed as possible to antenna and all functions are realized by digital signal processing (DSP) to offer small size device as well as low power. The narrow and wide band architectures in wireless communications systems are always suffer from interfere phenomena due to nearest channel. The narrowband systems practically support only a single carrier channel while wideband will support multiple channel. Hence, the reconfiguration idea in the IF band required to be efficient in term of selectivity and adaptively to overcome the interference [3]. In the cellular handset and

#### Manuscript published on 30 January 2014.

\*Correspondence Author(s)

Dr. Majid S. Naghmash, power engineering department, Electrical and Electronic College, Foundation of Technical Education, Baghdad, Iraq.

Hazim Salah Abdulsatar, Electronic techniques department, Institute of Technology, Foundation of Technical Education, Baghdad, Iraq.

Tahseen Flaih Hasan, Electronic techniques department, Institute of Technology, Foundation of Technical Education, Baghdad, Iraq.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license http://creativecommons.org/licenses/by-nc-nd/4.0/

communications systems, the tactical narrowband architectures is presents and the interference rejection inherently founded [4].

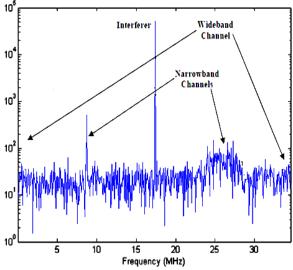

Thus, the interference in the adjacent band rejection is required to overcome and process carefully as illustrated in Figure 1.

Figure 1: Channel interferer in Narrowband and wideband frequency.

Therefore, at any time, many simultaneous carrier channel might be activated in wideband architectures like satellite communications and cellular base station making big problems and this phenomena required to break in and process properly. Hence, the channelization in wideband receiver systems is a key elements which is used to isolate the independent communication channel restricted in the wideband signals [5]. The theory of decimation or down sampling process is to reduce the sample rate of incoming signal after D/A converter. The down sampling theory could be expressed as:

$$y(n) = x(Mn), \qquad n = \pm \infty$$

$$(1)$$

$$Y(e^{j\omega}) = \frac{1}{M} \sum_{k=0}^{M-1} X(e^{j(\omega - 2\pi k)/M})$$

$$(2)$$

Where x(n) is the decimator input signals, M is decimation factor, y(n) is the decimator output signal

In frequency domain after the signal is moved from time domain by A/D converter, the process could be expressed as:  $\cos(\omega_c t) = \frac{1}{2} X X(\omega - \omega_c) + \frac{1}{2} X X(\omega + \omega_c)$

$$\cos(\omega_c t) = \frac{1}{2} X X(\omega - \omega_c) + \frac{1}{2} X X(\omega + \omega_c)$$

(3)

$$\sin(\omega_c t) = \frac{1}{2} X X(\omega - \omega_c) + \frac{1}{2} X X(\omega + \omega_c)$$

(4)

Then the decimator output has kept all the data in the desired frequency band with down convert to baseband to permit the sample frequency to be reduced. The advantage of this process is to simplify the additional processing and FPGA functioning due to lowest clock frequency , therefore allowing more processing to be fitted into hardware implementation. Additionally, the low clock frequency could reduce the power required in FPGA.

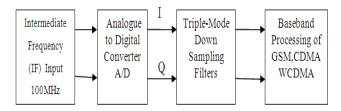

Numerous researchers are investigate in this field which propose efficient implementation of multi-stage digital filter bank [6-9]. An independent channel filter approach is proposed by [10] which complexity is directly proportional with number of received channels. Consequently, this approach is efficient if the number of channels is small. Capable implementation of channelized filter by using discrete Fourier transform filter bank is projected in [11-12]. Based on combination of polyphase filter design modules, a hybrid filter bank has been targeted by [13] with less computation corresponding to conventional associated by some limitations. Efficient sample rate converter with two stages filter bank and multi-mode channelizer has been proposed by [14]. In this paper, a novel reconfigurable channelization techniques utilize in wideband design are examine and investigated to produce software channel filter capable to isolate triple channel in most popular protocols systems. The triple - mode channel receiver shown in Figure 2 is investigated properly.

Figure 2: Programmable IF channelize receiver

# II. FILTER ARCHITECTURE

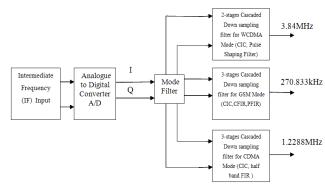

To describe and realize the software radio receiver, a capable concept of triple mode down sampling filter for IF band is proposed as illustrated in Figure 3. The filtering process in IF band is the more important stage in signal processing due to size occupied and power consumption spent in the multiplication process. A digital filter like finite impulse response (FIR) required to implement in more than one stage to decrease the circuit complexity and multiplication. Hence, the triple mode down sampling filter could be design to provide the GSM, WCDMA, and CDMA system requirements in the passband, stopband and adjacent band rejection. Consequently, these modes contribute to a common IF front end and could be switched to each other by software design. The bandwidth of 5MHz centered at 100MHz IF signal which contain WCDMA, GSM and CDMA channels. The sample rates selected to be 30.72MHz for three mode. The specifications of three mode is illustrated in Table 1.

Table 1: GSM, CDMA2000 and WCDMA requirements

| Parameters      | WCDMA    | GSM          | CDMA       |

|-----------------|----------|--------------|------------|

| Bit Rate        | 3.84Mcps | 270.833Kbps  | 1.2288Mbps |

| Carrier Spacing | 5MHz     | 200kHz       | 3.75MHz    |

| Chip Rate       | 4.096MHz | 2.5MHz       | 3.6864MHz  |

| IF Frequency    | 61.44MHz | 69.333284MHz | 64.44MHz   |

Figure 3: Proposed Filter architecture

Subsequently, the preferred channels will be removed from 5MHz wideband signal by filter realization. The reconfigure ability of channelizer have to talented the same filter hardware for new communication standard with less reconfiguration overhead instead of employing separate filter for each standard. In the conventional filter, the reconfigure ability is achieved by switching between three filters which is not an proficient advance. The reconfigure ability in the filter have to achieved by reconfiguring the same prototype filter to process the signal of new communication standard with less possible overhead.

#### A. GSM Mode

For GSM processing, the channel bandwidth of 200kHz could be extracted from 5MHz received signal and down samples to the original sample rate of 270.833 Kbps by using decomposition of three stages filter. The first stage in this decomposition is the Cascaded Integrated Comb (CIC) filter with down sampled factor of 64 to introduce 270.833kHz. The GSM requirement will satisfy by adding further filtering stage such as Compensating Finite Impulse Response (CFIR) to attenuate the block signal at 200kHz. Finely, an Programmable Finite Impulse Response (PFIR) in order to shape the GSM mask frequency. The filter structure shown in Figure 4 represent the GSM mode down sampling realization. The GSM spectrum requirement is achieved as illustrated in Figure 5.

Figure 4: GSM mode down sampling filter

Figure 5: GSM spectrum produce by proposed filter

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.

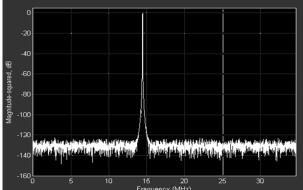

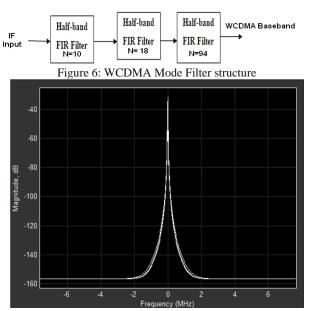

#### B. WCDMA Mode

In WCDMA mode, the filter structure consist of three half band FIR filter is used to decrease the data rate from 4.096MHz down sampled to 3.84Mcps. The WCDMA requirements could be satisfy by using Equiripple half band FIR filter with 10, 18 and 94 filter order for first, second and third stage respectively as shown in Figure 6. The WCDMA spectrum requirement is achieved as illustrated in Figure 7.

Figure 7: WCDMA spectrum produce by proposed filter

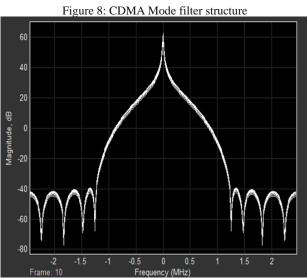

#### c. CDMA Mode

To extract the 1.25 MHz from 5MHz bandwidth which represents the baseband of CDMA system, an CIC decimator with filter order of 5 and down sampling rate of 25 is used as first stage in the filter structure. The second stage is a half band filter with 25 filter order is used to shape the system requirements and further down sampled filtering using MAC FIR filter decomposition. The filter structure is illustrated in Figure 8 while the filter response which satisfy the CDMA system is shown in Figure 9.

Figure 9: CDMA Mode spectrum response of proposed filter

#### III. HARDEWARE IMPLEMENTATION

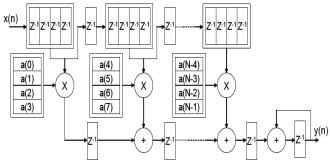

#### A. Multi-MAC Decomposition

The multi-MAC (Multiply-Accumulate) decomposition based FIR utilizing has been used to introduce the computational efficient implementation of proposed filter as shown in Figure 16. The implementation of single multi-MAC is extensible to achieve higher performance, more channels and high sample rate.

Figure 16: Multi –MAC Implementation decomposition Design The required multipliers to implement a proposed decimation filter will be determined y calculating the number of necessary multiplies to execute the computation which divided by the number of clocks obtainable to process any input sample. The in hand clock cycle value is forever rounded down and the multiplications numbers rounded up to the nearest integer. However there is non-zero remained, thus, some of the MAC engines calculate fewer coefficients than others. By using multi-MAC decompositions, the core will generate an implementation that meet the defined performance required based on the systems clock rate. In this case, the core will insert one or more multipliers to meet the overall throughput requirements. The FIR compliers consist two MAC architectures to implement the systolic and transpose filter structure.

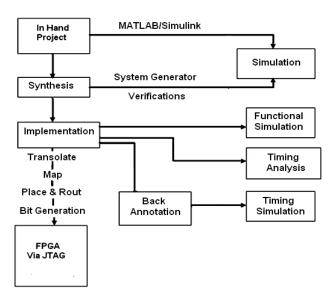

### B. FPGA Design flow

The design flow of proposed decimation filter is illustrated in Figure 17. The signal is down sampled before filtering which reduce the filter coefficients number necessary to implements the preferred filter resulting in speed improvement and power consumption. The whole decimator design is synthesized to create the Verilog Netlist using the output options under System Generator token GUI interface and the results of the performance of map, place and route task done, by using the project navigator tool to implement the design in real time. After the HDL code generation of the Netlist module, the Integrated Software Environment (ISE) software used its own Xilinx Software Technology (XST) environment to convert the HDL code into FPGA based optimized Netlist Electronic Design Interchange Format File (EDIF) and User Constraint File (UCF), and this process called synthesis. In the translate step, the EDIF file will merged with UCF to produce Native Generic Database File (NGD). The logic defined by NGD file will mapped into FPGA elements by so called NCD file (Native Circuit Description). Finally, the NCD file has place and route to FPGA with time constraint to generate PAR report (Place and Rout Report) from ISE project navigator and produce the Bit

stream into FPGA via JTAG programs.

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.

Figure 17: FPGA Design Flow

#### C. Fixed Point Design

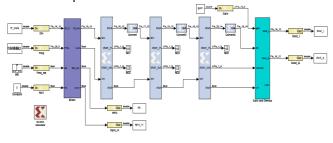

Before FPGA designs steps, the fixed point values of proposed module has been designed and simulated using system generator block set from Xilinx and this module should verify with MATLAB simulation for accuracy as shown in Figure 18. The input and output gate way in system generator is used to change the floating point arithmetic values for all parameter to fixed point arithmetic values. Therefore, a low quantization errors will happen nevertheless it's still acceptable.

Figure 18: Filter implementation using System Generator

In the Netlist directory specified in system generator token GUI, the ISE project report file is generated along with the design timing constraints. The HDL code has been developed and synthesis on Xilinx Vertix-4 using Integrated software environments (ISE). The maximum frequency of the proposed filter is 100MHz. The project status of ISE software generates the decimation utilizing summary as shown in Table 3. The table lists the total number of slices and look-up tables (LUTs) used in this design. In each slice they are two LUTs and two FFs, during the PAR, the ISE software put all necessary LUTs close to each other for minimum propagation of data, for that some LUT inside slice not used and in some slice only FFs is used without LUT so, the number of LUTs cannot be calculated manually, therefore the LUTs could be less or more than Slices depend on software optimization. The device utilization summary generated by ISE software represents the available logic elements in FPGA and logic elements used by the in hand project been designed. The used logic elements to the available logic elements could be determined by below formula.

utilization% =  $\frac{\text{used logic elements}}{\text{available logic elements}} X 100$ (5)

Then, the utilization number of slices flip flop, 4-input LUTs and bonded IOBs could be calculated and compared with other designs and conventional model as illustrated in Table 3

Utilized number of Slice Flip Flop = (2451/30720) x 100 = 8% (6)

Utilized number 4-input LUTs =

$$(921/30720) \times 100 = 4\%$$

(7)

Utilized number of occupied Slices = (600/15360) x 100 = 4% (8)

Utilized number of bonded IOBs =

$$(30/448) \times 100 = 6\%$$

(9)

Comparing with conventional design, the proposed filter appear more efficient and less FPGA area and this will reduce the power consumption. Consequently, reduce the computation and complexity of the circuit to offer more flexibility in the user demand. The memory size of the filter is increase as the complexity decrease. An comparison of slices and LUTs is illustrated in Table 4.

Table 3: decimation project device utilization summary

| Device Utilization Summary                     |         |           |             |         |  |  |

|------------------------------------------------|---------|-----------|-------------|---------|--|--|

| Logic Utilization                              | Used    | Available | Utilization | Note(s) |  |  |

| Number of Slice Flip Flops                     | 2451    | 30,720    | 8%          |         |  |  |

| Number of 4 input LUTs                         | 921     | 30,720    | 4%          |         |  |  |

| Logic Distribution                             |         |           |             |         |  |  |

| Number of occupied Slices                      | 600     | 15,360    | 4%          |         |  |  |

| Number of Slices containing only related logic | 600     | 661       | 100%        |         |  |  |

| Number of Slices containing unrelated logic    | 0       | 661       | 0%          |         |  |  |

| Total Number of 4 input LUTs                   | 755     | 30,720    | 2%          |         |  |  |

| Number used as logic                           | 430     |           |             |         |  |  |

| Number used as a route-thru                    | 8       |           |             |         |  |  |

| Number used as Shift registers                 | 218     |           |             |         |  |  |

| Number of bonded IOBs                          | 30      | 448       | 6%          |         |  |  |

| Number of BUFG/BUFGCTRLs                       | 2       | 32        | 3%          |         |  |  |

| Number used as BUFGs                           | 2       |           |             |         |  |  |

| Number used as BUFGCTRLs                       | 0       |           |             |         |  |  |

| Number of FIFO16/RAMB16s                       | 2       | 192       | 1%          |         |  |  |

| Number used as FIFO16s                         | 0       |           |             |         |  |  |

| Number used as RAMB16s                         | 2       |           |             |         |  |  |

| Number of DSP48s                               | 2       | 192       | 1%          |         |  |  |

| Total equivalent gate count for design         | 158,984 |           |             |         |  |  |

| Additional JTAG gate count for IOBs            | 1,488   |           |             |         |  |  |

Table 4: FPGA Slices and LUTs comparison

| Resource | Utilization %                      | Utilization%              | Utilization%            |  |

|----------|------------------------------------|---------------------------|-------------------------|--|

|          | Santhosh Y. N., et al<br>IEEE 2010 | Rajesh & Pattnaik<br>2013 | Proposed Filter<br>2013 |  |

| Slices   | 30                                 | 11                        | 8                       |  |

|          |                                    |                           |                         |  |

| LUTs     | 20                                 | 7                         | 4                       |  |

|          |                                    |                           |                         |  |

## IV. CONCLUSION

The hardware proficient techniques has been used to implement the reconfigurable down sampling filter for wireless systems based SDR knowledge is presented in this paper. The Equiriple FIR digital filter algorithms and multistage half band FIR filter decomposition is proposed for less filter length and enhanced computational complexity to improved the filter rate.

w.ijitee.org

The Multiply-Accumulate (MAC) decomposition based FIR architecture is used in hardware implementation to optimize the speed and area together which resulting in power consumption reduction. The FPGA vertix-4 and DSP48E blocks from Xilinx are used which contains multiplierless MAC filter. The proposed down sampling filter could be used at maximum frequency of 100MHz with minimum power and FPGA area efficient. Consequently, the implementation of down ampling filter on specific target FPGA Vertix-4 resulting in cost effective solution for SDR technology which is capable to maintain the current and future generation of wireless and mobile systems.

#### REFERENCES

- Rajesh and Pattnaik, "Reconfigurable Design of GSM Digital down Converter for Enhanced Resource Utilization", International Journal of Computer Applications (0975 – 8887) Volume 57 – No.11, November 2013

- Santhosh Y. N., et al., "Design and VLSI Implementation of interpolators/decimators for DUC/DDC", Third International Conference on Emerging Trends in Engineering and Technology, IEEE, 978-0-7695-4246-1/10, 2010

- Rajesh Mehra, Swapna Devi' "Efficient Hardware Co-Simulation of Down Convertor for Wireless Communication Systems" International Journal of VLSI Design & Communication Systems (VLSICS), pp. 13-21, Vol.1, No.2, June 2010.

- Majid Salal Naghmash and Mohd Fadzil Ain "Design of minimum error digital down-converter (DDC) for GSM mask requirements", Journal of Engineering and Technology Research Vol.1 (5), pp.091-101, August, 2009.

- Kyung-ho Hwang and Dong-ho Cho, "Software Defined Radio Technology," Telecommunications Review, vol. 10, no. 1, pp. 130-143, Jan/Feb. 2000,

- Rajesh Mehra, Dr. Swapna Devi, "FPGA Based Design of an Optimized Digital Down Converter for Software Radio Wireless Applications" Innovative Conference on Embedded Systems, Mobile Communication and Computing, pp. 43-51, ICEMC2-2010.

- Young-bum Chang, "A Block FIR Filtering Architecture for IF Digital Down Converter," Journal of IEEK, vol. 37, no. 9, , pp. 465-473. Sept. 2000

- LIN Fei-yu1, QIAO Wei-ming, WANG Yan-yu, LIU Tai-lian1, FAN Jin, HANG Jian-chuan, "Efficient WCDMA Digital Down Converter Design Using System Generator". Proceeding of International Conference on Space Science and Communication, pp.89-92, IEEE-2009.

- S. Im, W. Lee, C. Kim, Y. Shin, S.H. Lee, and J. Chung, "Implement of SDR-Based Digital IF Channelizer / De channelizer for Multiple CDMA Signals," IEICE Trans. Communications, vol. 83, no. 6, pp. 1282-1289. June 2000

- Alan Y. Kwentus, "Application of Filter Sharpenning to Cascaded Integrator-Comb Decimation Filters," IEEE, vol. 45, no. 2, pp. 457-467. Feb. 1997

- Emad S Malik, Khaled A. Shehata, Ahmad H. Madian, "Design of Triple Mode Digital Down Coverter for WCDMA, CDMA 2000 and GSM of Software Defined Radios" International Conference on Microelectronics, pp. 272-275, IEEE-2009.

- Hyuk J. Oh, Sunbin Kim, and Ginkyu Choi, "On the Use of Interpolated Second-Order Polynomials for Efficient Filter Design in Programmable Downconversion," IEEE J. Select. Areas Commun., vol. 17, no. 4, , pp. 551-560., Apr. 1999

- G. Mazzini, G. Setti, and R. Rovatti, "Chip pulse shaping in asynchronous chaos-based DS-CDMA," IEEE Trans. Circuits Syst. I, vol. 54, no. 10, pp. 2299–2314, Oct. 2007.

- 14. Amir Beygi, Ali Mohammadi, Adib Abrishamifar. "AN FPGA-BASED IRRATIONAL DECIMATOR FOR DIGITAL RECEIVERS" in 9th IEEE International Symposium on Signal Processing and its Applications, pp. 1-4, ISSPA-2007.

- Ming Jian, Weng Ho Yung, and Bai Songrong, "An Efficient IF Architecture for Dual-Mode GSM/W-CDMA Receiver of a Software Radio," IEEE Int'l Workshop on Mobile Multimedia Communications, vol. 87932, , pp. 21-24. Nov. 1999

M. Cummings, S. Haruyama, "FPGA in the Software Radio". IEEE

- M. Cummings, S. Haruyama, "FPGA in the Software Radio". IEEE Communications Magazine, v37, pp.108-112. Feb. 1999.

- Rabiner, Crochiere, Optimum FIR Digital Filter Implementations for Decimation , Interpolation, and Narrow-Band Filtering, IEEE

- Transactions on Acoustics, Speech, and Signal Processing, October 1975

- Rajesh Mehra, Dr. Swapna Devi, "FPGA Based Design of an Optimized Digital Down Converter for Software Radio Wireless Applications" Innovative Conference on Embedded Systems, Mobile Communication and Computing, pp. 43-51, ICEMC2-2010.

- Xilinx Corp., Virtex-4 Xtreme DSP Design Considerations User Guide.2008

- 20. Xilinx Corp., DDS Compiler v2.1, 2008

- 21. Xilinx Corp., System Generator User Guide, 2008

- 22. Xilinx Corp., Xilinx ISE 10.1 Software Manuals, 2008.

#### **AUTHOR PROFILE**

Majid S. Naghmash Received His Msc. degree in the satellite communication engineering from University of Technology Baghdad – Iraq-2004 and Doctor of philosophy in wireless and mobile system from Universiti Sains Malaysia (USM) Malaysia –Penang -2011. He is currently a head of power engineering department at College of Electrical and Electronic Engineering Techniques-Foundation of technical Education-Iraq. He has been a full-time lecturer in the

Computer Department, Baghdad, Iraq, since March 2012. He also worked as senior researcher in the Iraqi Center of Development and Research since 1994.

Network Administration.

Hazim Salah Abdulsatar Received his B.Sc. in Electrical from the Faculty of Electrical and Electronic Engineering, University of Sarajevo in 1984, and received the M.Sc. degree in Electrical and Electronic engineering from Faculty of Electrical Engineering, University of Belgrade in 1986. Currently he is Assist Lecturer, Researcher and training supervisor, Electronic techniques department in Institute of Technology Baghdad. His research interests include, Electronic circuit design, Wired & Wireless

Administration.

Tahseen Flaih Hasan Received his B.Sc. in Electrical from the Faculty of Electrical and Electronic Engineering, University of Sarajevo in 1983, and received the M.Sc. degree in Electrical and Electronic engineering from Faculty of Electrical Engineering, University of Belgrade in 1985. Currently he is Assist Lecturer, Researcher and training supervisor, Electronic techniques department in Institute of Technology Baghdad. His research interests include, Electronic circuit design, Wired & Wireless Network