# Performance Analysis of Non-Identical Master Slave Flip Flops at 65nm Node

Urvashi Chopara, Alok Kumar Mishra, D. Vaithiyanathan

Abstract: This paper presents the performance analysis of the different master slave flip flop reported and comparison of their parameters such as power, area, delay setup time and hold time. To reduce the number of transistor count various logic structure mater slave design have been proposed that results reduction in total area of the flip flop. Advantage and disadvantage of the each flip flop has been discussed. Process corner analysis of all flip flop is also presented at supply voltage of 0.7 volts at 27°C temperature. Percentage reduction in power and speed of operation i.e. frequency are discussed

Keywords: Transmission gate, auxiliary transistor, Flip Flop, switching activity.

### I. INTRODUCTION

$\Upsilon$ HE technological advancement such as Internet of Thing (IoT) devices means that processors are now going to be comprehensive [1]. IoT have application in various field that includes smart environments and transportation, healthcare, traffic etc. However, prevalent deployment of these devices demands low power/energy [2]. Based on such background several types of master slave flip flop logic structure have been reported. From the last decade main idea behind the development of the flip flops is the need of low power consumption circuit without any degradation in speed and area concern are also there behind the development in addition to single-phase clocked circuits minimization power efficiency[3][4]. A considerable reduction in power consumption can be seen using single phase clocked circuits. A flip flop should be contention free that helps in lowering power consumption concerns [5] [6].

### II. REVIEW OF DIFFERENT MASTER SLAVE

In the era of VLSI circuit there is a need of a storing element that consumes less power and will not get effected by the changing input. A master slave circuit fulfils this requirement [6]-[10]. The conventional master slave i.e., SRMS Flip Flop consist of 30 transistor. In order to reduce

### Revised Manuscript Received on November 22, 2019.

\* Correspondence Author

**Urvashi Chopra**, PG Student, Department of Electronics and Communication Engineering, National Institute of Technology Delhi, India Email:urvashichopra911@gmail.com

Alok Kumar Mishra, PhD Scholar, Department of Electronics and Communication Engineering, National Institute of Technology Delhi, India Email: alokkmishra@nitdelhi.ac.in

**D.Vaithiyanathan\***, Assistant Professor, Department of Electronics and Communication Engineering, National Institute of Technology Delhi, India Email: dvaithiyanathan@nitdelhi.ac.in

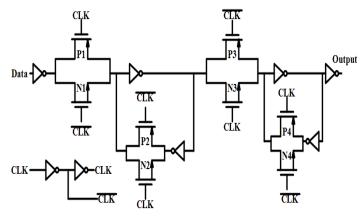

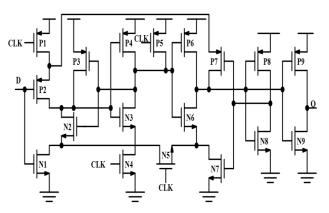

area some other Flip Flop have been reported. One of them is Transmission gate Flip Flop (TGFF) shown in fig.1 which is the most commonly used Flip Flop now a days. It consist of 4 transmission gates, 6 inverters and 2 inverters in its clock generator circuit. There is requirement of additional circuitry for generating clock and clock bar signal in both SRFF and TGFF clock. Clock and clock bar signals makes sure that either one of master slave should work at a time. Along with the requirement of extra circuitry for clock and clock bar signal there is a problem of clock overloading in TGFF. There is a work load of 12 transistors on a clock which causes a persistent power consumption even at the condition when input vestiges static. This setback in additionally occurs in SRFF too [11]-[16].

Fig. 1. CMOS circuit of TGFF

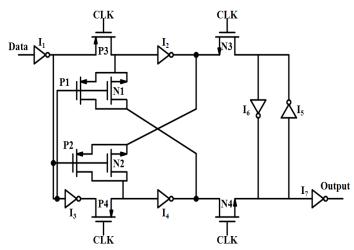

Fig. 2. CMOS circuit of ACFF

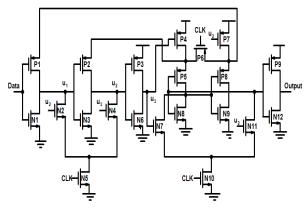

Fig. 3. TCFF CMOS circuit

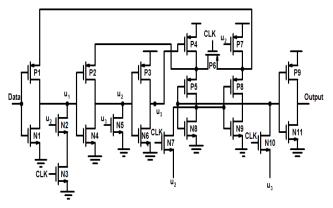

Fig. 4. CMOS circuit of LRFF

Fig. 5. CMOS circuit of 18TSPC

Therefore the aim of the circuit designer is not only reducing the transistor count but also to achieve a circuit that rescue it from clock overloading. A number of circuit have been reposed so far including these two properties. One of them is Adaptive Coupled Flip Flop (ACFF) in Fig.2 which consist of 22 transistors. It consist of 4 pass transistors that help to provide a strong 0 or strong 1 to master and slave. ACFF consist of a differential structure having a NMOS and a PMOS transistor connected parallel having same input at gate terminal. This differential structure forms a latch in master ride and it overcomes the impact of process variation on master latch. There is a considerable variation in power consumption can be seen from table. Transistor count

reduction is only 2 transistor but power is considerable. This is due to no clock overloading problem in <u>ACFF</u>. Another circuit called topologically compressed Flip Flop based on the idea of making master circuit using multiplexer circuit. By topologically compressing the circuit of SR Flip Flop that use multiplexer as a master, <u>TGFF</u> [6] has achieved like <u>ACFF</u> [5], <u>TCFF</u> [3] also have no clock overloading in fig. 3. Another reported Flip Flop design is Logic Structure Reduction Flip-Flop (<u>LRFF</u>) [2] in fig.4 that consist of 19 transistors with no work load on clock problem. It is further extension of <u>TCFF</u>. It consist of CPL structure (Complementary Pass Logic) that replace 2 <u>NMOS</u> transistor connected in such having one transistors with input clock and other with input <u>u1</u>, <u>u2</u> to a transistor having input as clock and <u>u1,u2</u> connected to source.

The recent <u>MSFF</u> reported is <u>18TSPC</u> flip flop that have transistor count of 18 in fig.5. Main idea behind <u>18TSPC</u> is the replacement of master and slave by multiplexer.

In <u>TCFF</u> only master is replace by a multiplexer but in <u>18TSPC</u> both master and slave are replaced by multiplexer.in <u>18TSPC</u> also used the topological compression technique. Transistor having clock signal are converted to a single transistor with clock signal as input. Drawback of <u>18TSPC</u> is that the master is not holding the data correctly when  $\underline{clk}=1$ . There is no direct Path from input to output can be seen in <u>18TSPC</u> FF.

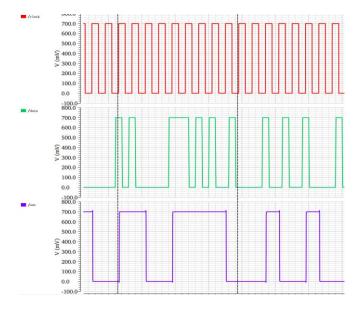

Fig. 6. Output Waveform of Master Slave Flip Flops

### III. RESULT AND DISCUSSION

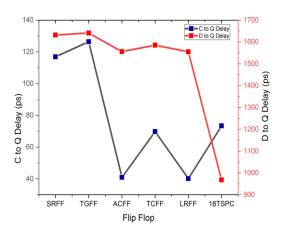

Tabulation comparison of flip flops is shown in Table I. It is shown that as transistor count is reducing from  $\underline{TGFF}$  to  $\underline{18TSPC}$ , power consumed by the flip flop is also reducing. Clock to Output and Data to Output delay of the flip flops are in a decreasing manner because of less number of transistors in the critical path. Further comparisons of these Flip Flops

are made on the basis of Layout Area, <u>Setup</u> time, Hold time, and PDP's.

TABLE I COMPARISON OF VARIOUS FF DESIGNS AT 500MHZ AT 0.7 V

| =                             | 111 00011111111111111111111111111111111 |       |       |       |        |  |

|-------------------------------|-----------------------------------------|-------|-------|-------|--------|--|

| FF Designs                    | TGFF                                    | ACFF  | TCFF  | LRFF  | 18TSPC |  |

| Number of Transistors         | 24                                      | 22    | 21    | 19    | 18     |  |

| Layout Area(um <sup>2</sup> ) |                                         | 39.07 |       | 45.14 | 28.76  |  |

| Clock to Q Delay(ps)          | 126.4                                   | 40.98 | 69.77 | 40.17 | 73.37  |  |

| Data to Q Delay(ps)           | 1641                                    | 1556  | 1585  | 1555  | 968.4  |  |

| Average power (uW)            | 1.099                                   | 0.594 | 0.760 | 0.561 | 0.285  |  |

| SetupTime(ps)                 | 208.2                                   | 239.6 | 239.8 | 209.8 | 283.6  |  |

| Hold Time(ps)                 | 190.6                                   | 160.3 | 160.2 | 190.2 | 215.2  |  |

| PDP <sub>CQ</sub> (aJ)        | 138                                     | 24.3  | 53.02 | 22.53 | 20.91  |  |

| $PDF_{DQ}(fJ)$                | 1.803                                   | 0.924 | 1.204 | 0.872 | 0.276  |  |

## TABLE II CQ DELAY AND POWER OF 18TSPC WITH TEMPERATURE (nW)

| Temp | CQ Delay(18 TSPC) | Power(18 TSPC) |

|------|-------------------|----------------|

| -25  | 73.28             | 0.264u         |

| 0    | 73.23             | 0.273u         |

| 25   | 73.35             | 0.284u         |

| 50   | 73.61             | 0.299u         |

| 75   | 74.01             | 0.320u         |

| 100  | 74.61             | 0.349u         |

| 125  | 75.37             | 0.387u         |

### TABLE III POWER VS SUPPLY (uW)

| Supply\<br>f/f | TGFF   | ACFF   | TCFF   | LRFF   | 18 TSPC |

|----------------|--------|--------|--------|--------|---------|

| 0.5            | 0.535u | 0.285u | 0.393u | 0.231u | 0.154u  |

| 0.6            | 0.753u | 0.408u | 0.480u | 0.371u | 0.211u  |

| 0.7            | 1.099u | 0.594u | 0.760u | 0.561u | 0.285u  |

| 0.8            | 1.532u | 0.903u | 1.108u | 0.866u | 0.386u  |

| 0.9            | 2.324u | 1.596u | 1.692u | 1.476u | 0.627u  |

| 1.0            | 4.680u | 3.278u | 3.225u | 3.076u | 1.578u  |

### TABLE IV SWITCHING ACTIVITY(S.A.)VS POWER

| (4 11)   |        |        |        |        |        |

|----------|--------|--------|--------|--------|--------|

| S.A.\F/F | TGFF   | ACFF   | TCFF   | LRFF   | 18TSPC |

| 100%     | 1.312u | 1.128u | 1.342u | 0.925u | 0.480u |

| 50%      | 1.954u | 1.776u | 2.717u | 1.690u | 0.607u |

| 25%      | 1.355u | 0.919u | 1.592u | 0.851u | 0.369u |

| 12.5%    | 1.080u | 0.497u | 1.048u | 0.439u | 0.248u |

| 0%       | 0.940u | 0.216u | 0.700u | 0.225u | 0.315u |

### TABLE V PROCESS CORNER POWER (uW)

| TIBLE VIROCESS CORVERTOWER (UV) |       |       |       |       |         |

|---------------------------------|-------|-------|-------|-------|---------|

| Process                         | TGFF  | ACFF  | TCFF  | LRFF  | 18 TSPC |

| Corners                         |       |       |       |       |         |

| TT                              | 1.098 | 0.592 | 0.324 | 0.556 | 0.285   |

| SS                              | 0.968 | 0.461 | 0.257 | 0.425 | 0.254   |

| SF                              | 1.122 | 0.640 | 0.352 | 0.602 | 0.301   |

| FS                              | 1.120 | 0.599 | 0.339 | 0.574 | 0.296   |

| FF                              | 1.397 | 1.054 | 0.656 | 1.060 | 0.468   |

Fig.6 shows the output waveform. Waveform satisfies for different combinations of clock and data. Table II shows the

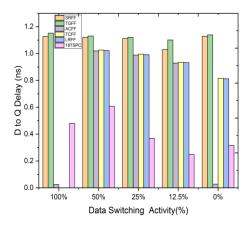

CQ DELAY and POWER comparison of 18TSPC circuit at a temperature range of 25 degree to 125 degree. As temperature if rising delay and power is increasing, but in a controlled fashion. Table III shows the power consumed by Flip Flops at different supply voltages. 18 TSPC FF have least power consumption value among different FF. Table IV shows power vs. switching activity variation of different flip flops. Switching activity is the fraction of occurrence of data at constant clock pulses. 18TSPC have least power consumption among 5 flip flops.

Fig. 7. Data to Q delay and Clock to Q Delay of different Flip flops

Fig. 8. Data Switching Activity vs. Data to Q Delay.

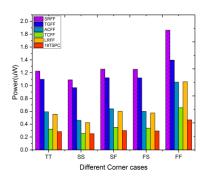

Fig. 9. Process Corner analysis of different flip flops

### Performance Analysis of Non-Identical Master Slave Flip Flops at 65nm Node

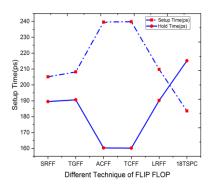

Fig. 10. Setup and Hold time of various flip flops

### IV. CONCLUSION

From the results we can see that there is considerable reduction in power dissipation when clock overloading problem has been eliminated. There are two advantage in the <u>ACFF</u>, first is two pass transistor is used in order to pass strong zero or strong 1 from either of them second is differential structure having <u>PMOS</u> and <u>NMOS</u> in parallel that helps to pass strong logic 0 or logic <u>lin</u> latch. From the <u>ACFF</u> we can get the idea of how transistor count can be reduce without affecting the performance. In <u>TCFF</u> redundant transistor are replace by 2 transistor each in Master and Slave. From the <u>LRFF</u> one can learn To reduces two transistor having input as <u>clk</u> and node voltage to only one transistor having as input and node voltage at source terminal of the transistor having clock as input.

#### REFERENCES

- Y. Cai, A. Savanth, P. Prabhat, J. Myers, A. S. Weddell and T. J. Kazmierski, "Ultra-Low Power 18-Transistor Fully Static Contention-Free Single-Phase Clocked Flip-Flop in 65-nm CMOS," in IEEE Journal of Solid-State Circuits, vol. 54, no. 2, pp. 550-559, Feb. 2019.

- Solid-State Circuits, vol. 54, no. 2, pp. 550-559, Feb. 2019.

J. Lin, M. Sheu, Y. Hwang, C. Wong and M. Tsai, "Low-Power 19-Transistor True Single-Phase Clocking Flip-Flop Design Based on Logic Structure Reduction Schemes," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 25, no. 11, pp. 3033-3044, Nov. 2017.

- N. Kawai et al., "A Fully Static Topologically-Compressed 21-Transistor Flip-Flop With 75% Power Saving," in IEEE Journal of Solid-State Circuits, vol. 49, no. 11, pp. 2526-2533, Nov. 2014.

- H. Kawaguchi and T. Sakurai, "A reduced clock-swing flip-flop (RCSFF) for 63% power reduction," in IEEE Journal of Solid-State Circuits, vol. 33, no. 5, pp. 807-811, May 1998.

- C. K. Teh, T. Fujita, H. Hara and M. Hamada, "A 77% energy-saving 22-transistor single-phase-clocking D-flip-flop with adaptive-coupling configuration in 40nm CMOS," 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, 2011, pp. 338-340.

- E. Consoli, G. Palumbo and M. Pennisi, "Reconsidering High-Speed Design Criteria for Transmission-Gate-Based Master-Slave Flip-Flops," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 20, no. 2, pp. 284-295, Feb. 2012.

- K. Yamada, H. Maruoka, J. Furuta and K. Kobayashi, "Radiation-Hardened Flip-Flops With Low-Delay Overhead Using pMOS Pass-Transistors to Suppress SET Pulses in a 65-nm FDSOI Process," in IEEE Transactions on Nuclear Science, vol. 65, no. 8, pp. 1814-1822, Aug. 2018.

- V. Stojanovic and V. G. Oklobdzija, "Comparative analysis of masterslave latches and flip-flops for high-performance and low-power systems," in IEEE Journal of Solid-State Circuits, vol. 34, no. 4, pp. 536- 548, April 1999.

- Jiren Yuan and C. Svensson, "New single-clock CMOS latches and flipflops with improved speed and power savings," in IEEE Journal of Solid-State Circuits, vol. 32, no. 1, pp. 62-69, Jan. 1997.

- A. Hirata, K. Nakanishi, M. Nozoe and A. Miyoshi, "The cross chargecontrol flip-flop: a low-power and high-speed flip-flop suitable for

- mobile application SoCs," Digest of Technical Papers. 2005 Symposium on VLSI Circuits, 2005., Kyoto, Japan, 2005, pp. 306-307.

- K. Kobayashi et al., "A Low-Power and Area-Efficient Radiation-Hard Redundant Flip-Flop, DICE ACFF, in a 65 nm Thin-BOX FD-SOI," in IEEE Transactions on Nuclear Science, vol. 61, no. 4, pp. 1881-1888, Aug. 2014.

- N. Nedovic and V. G. Oklobdzija, "Hybrid latch flip-flop with improved power efficiency," Proceedings 13th Symposium on Integrated Circuits and Systems Design (Cat. No.PR00843), Manaus, Brazil, 2000, pp. 211-215.

- Jiren Yuan and C. Svensson, "Principle of CMOS circuit power-delay optimization with transistor sizing," 1996 IEEE International Symposium on Circuits and Systems. Circuits and Systems Connecting the World. ISCAS 96, Atlanta, GA, USA, 1996, pp. 637-640 vol.1.

- H. Partovi, R. Burd, U. Salim, F. Weber, L. DiGregorio and D. Draper, "Flow-through latch and edge-triggered flip-flop hybrid elements,"

1996 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, ISSCC, San Francisco, CA, USA, 1996, pp. 138-139.

- Umimg Ko, A. Hill and P. T. Balsara, "Design techniques for highperformance, energy-efficient control logic," Proceedings of 1996 International Symposium on Low Power Electronics and Design, Monterey, CA, USA, 1996, pp. 97-100.

- 16. F. Aezinia, S. Najafzadeh and A. Afzali-Kusha, "Novel High Speed and Low Power Single and Double Edge-Triggered Flip-Flops," APCCAS 2006 - 2006 IEEE Asia Pacific Conference on Circuits and Systems, Singapore, 2006, pp. 1383-1386.

- Absel, Kalarikkal, Lijo Manuel, and R. K. Kavitha. "Low-Power Dual Dynamic Node Pulsed Hybrid Flip-Flop Featuring Efficient Embedded Logic", IEEETransactions on Very Large Scale Integration (VLSI) Systems, 2012.

### **AUTHORS PROFILE**

**Urvashi Chopra** currently pursuing M.Tech in ECE(VLSI) from National Institute of Technology Delhi. She received BE degree in Electronics and Communication Engineering from Chandigarh College of Engineering and Technology, Panjab University Chandigarh in 2017. Her area of interest is low power VLSI design and Embedded Systems.

Alok Kumar Mishra received the Bachelor of Technology in Electronics and Communication Engineering from Uttar Pradesh Technical University Lucknow in 2012 and Master of Technology in Electronics Design and Technology from Tezpur University Assam in 2017. He is currently pursuing his PhD in the VLSI Design in National Institute of Technology Delhi, Delhi, India. He was a Research Associate under Special

Manpower Development Program Chip to System Design Project in National Institute of Technology Delhi and Lab Engineer in Indian Institute of Information Technology Allahabad.

**D.Vaithiyanathan** is currently working as Assistant Professor in the Department of Electronics and Communication Engineering, National Institute of Technology Delhi, India. From 2010 to 2017, he held the position of Teaching Fellow in the Department of Electronics and Communication Engineering, College of Engineering Guindy, Anna University, Chennai. He received his M.E

degree in Applied Electronics from Government College of Technology Coimbatore and Ph.D from College of Engineering Guindy, Anna University, Chennai. His research interest includes Embedded System, Memory Design, Low Power Design and VLSI Architecture for Digital Signal and Image Processing.