# Design a Low Power and High Speed Parity Checker using Exclusive—or Gates

Brahmaiah Battula, Valeti SaiLakshmi, S. Durga Sri Sravya, Putta Vijaya Lakshmi, Sunanda Karpurapu, S. Lakshmi Navya Sri

Abstract: In the presented paper we designed the parity checker by using EX-OR modules. The two EX-OR modules are presented to design the parity checker and correlated their outcomes based on the constraints like power, area, delay and power delay product (PDP). The previous design is with eight transistors EX-OR, but in the present six transistors EX-OR is used to design the parity checker. While correlating the parity checker design with 8T EX-OR and 6T EX-OR, the 6T EX-OR parity checker design gives optimized power, delay, area and PDP over the 8T EX-OR parity checker design. Simulations are done by using the 130nm mentor graphics tool. Finally the constraints like power, area, delay and PDP gets optimized successfully with the presented technology. Also, alternatively we can replace EX-OR modules with NAND modules to design parity checker.

Key terms: Power Delay Product (PDP), Parity Checker, EX-OR modules, Mentor Graphics tool.

#### I. INTRODUCTION

In this the parity codes are explained with different A paritybit-signature especially apt for exhaustive methods proposed and results shown that it is agreeable to valuable error coverage computations. And A PC relations based on consolidated generators has been studied and also gave easy formulas for cryptography, finally resulted with successful outcomes. Also A comparison among the parity-relations and its parameters are exhibited and found that they can be used to find the degree-of-freedom to analyze parity generators, to observe the durability. A technology to build codes using certain rate for the given number is presented, represented as repetition and single PC (RSPC) code and found that it works well for various ranges of code-rates. To raise the basic cone and to calculate the pseudo-code-words of PC code is studied and found few technologies, also gives some tools to examine the irreducible pseudo-code words. And A theoretical study on matrix transformations is done using Fourier-transforms and permutations. Also, their capacity on white-Gaussian-noise is showed. Also A paritygenerator based on uni-resonant-tunneling-bipolar-transistor (RTBT) is described and found that it yields important advantages as compared to previous ones. A virtual memory using hit RAM, which gains fastness and capacity, is proposed which results in less energy usage and delay.

Manuscript received on February 02, 2021.

Revised Manuscript received on February 08, 2021.

Manuscript published on February 28, 2021.

\* Correspondence Author

**Brahmaiah Battula\***, Department of ECE, JNTUK, Guntur, India. Email: <a href="mailto:brahmabattula@gmail.com">brahmabattula@gmail.com</a>

Valeti SaiLakshmi, Department of ECE, JNTUK, Guntur, India. Email: sailakshmivaleti@gmail.com

S. Durga Sri Sravya, Department of ECE, JNTUK, Guntur, India. Putta Vijaya Lakshmi, Department of ECE, JNTUK, Guntur, India. Karpurapu Sunandha, Department of ECE, JNTUK, Guntur, India. S. Navya Sri, Department of ECE, JNTUK, Guntur, India.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/)

The code suited to solve burst faults is demonstrated, since the used components is less than their code lengths it is shown as LDPC codes concept and concluded that it is efficient in correcting the faults. Various errors finding PC is described which can totally detect faults with the help of test-patterns that are created from identity and binary matrix which in turn supposed to find various errors which raises wired-OR networks shows the parity checker codes [1]-[9]. An altered A\* algorithm has been invented to fasten the tree search and concluded that it decreased the tree count as correlated with other A\* algorithms. And A part of errorblocks with one-second assemble figure of bit-interleaved parity (BIP) disruption is proposed and evaluated using Poisson-error and error-burst distribution. Also A generator matrix (GM)-depending technique is used and resulted that it needs low calculation time as compared with previous ones. A number of bit-parity depend, error finding technique for parallel CRC calculations is presented, by using some soft ware and ASIC development it is known that it is capable of finding errors that comprises low area and time. Parity vector which build minimized residual-generators is derived and concluded that the error finding probability is upgraded as compared to old techniques. An efficient method of parity-space dependent fault-detection and isolation (FDI) technology straight from input to through put is studied and found to be fruitful at every point. A stationary-wavelet-transform (SWT) is used in the residual wave along with that a novel residual generator, minimization technique is described and correlated with other techniques which found to be successful shows the issues of several techniques [10]-[16]. In the parity checker we use some recordings like A normal and efficient method to merge constrained-codes with parity-check (PC) codes for optical-recording is presented and found that it can rate 2/3code with no parity at normal as well as high density. Crossparity-check (CPC) codes to secure the information present in magnetic-tape is proposed and checked, found that it is used to divide the pc matrix by some number and to gain the remainder [17]-[19]. Likewise there are several techniques to detect the errors in the transmission and reception of bits as A new technology of low-density PC (LDPC) producer in china-digital-radio (CDR) is described and enforced on Xilinx FPGA which resulted 400 Mbps output and also reached the error essentials of CDR. Low-density based PC (LDPC) code is designed and studied in three parts with various technologies and found that it is having good performance. An LDPC code using finite-affine-planes is shown and found that it is having high fault detection capability with high rate. A low-density based generator matrix is changed as low-density PC code and concluded that it reduced the encoding difficulty and enhanced the decoder circuit resilience [20]

# Design a Low Power and High Speed Parity Checker using Exclusive-or Gates

And the calculations are optimized by following the techniques as A quantum-stabilizer-code is built which is depending on syndrome-assignment through classic PC matrix and studied; finally found that they provide quality through put. An 11-bit pc was described using verticallyintegrated-diode (VID) and concluded that it restored huge amount of EX-OR gates in standard PC. With the use of PC encoder an effective design was made which reduced the flip-flop count completely. Here self-testing-embedded (STE) PC was used with EX-OR gate as fundamental block which provided easy and accurate results. A new architecture of systematic-circulant (SC) generator-matrix depending on matrix transforms is demonstrated and concluded that the density reduces automatically with normal mathematical difficulty. The effective encoding of quasi-cyclic (QC) LDPC codes is studied and resulted that the difficulty of the code depends on the number of bits and length of code for serial and parallel encoding respectively [24]-[29].

#### II. IMPLEMENTED DESIGN:

In this parity checker is structured through the Ex-or gates in transistor level.

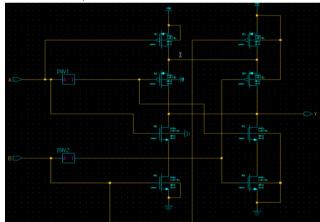

## A. Existed 8 Transistor Ex-or Design:

In this we implemented the two input Ex-or gate by using the eight transistors. This eight transistors Ex-or design uses the pass transistor logic. This existed 8T Ex-or design shows the highest power utilized, more delay and such that more PDP. To reduce these constraints like power, delay, transistor count, size and PDP.

Fig.1: Schematic of eight transistor Ex-or

Fig.2: simulated outcomes of eight transistor Ex-or

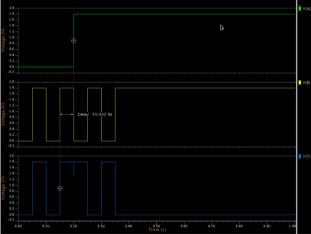

## B. Implemented 6 Transistor Ex-or Design:

We implemented the two input Ex-or design with six transistors by using the Pass transistor logic (PTL) style. So that the optimized six transistor Ex-or gives low power, less delay, less size, optimized transistor count and reduced PDP.

Fig3: schematic of six transistor Ex-or

Fig4: Simulated outcomes of six transistor Ex-or

The simulated outcomes of 6T Ex-or visualizes in the clear manner without any overshoot and undershoot when compared over the 8T Ex-or design. The constraints of power, delay and PDP are tabulated in the table 1.

Table1: comparison between 6T and 8T Ex-or design

| 10       | Table1: comparison between 01 and 01 Ex-or design |                                  |                               |                            |                         |  |  |  |  |

|----------|---------------------------------------------------|----------------------------------|-------------------------------|----------------------------|-------------------------|--|--|--|--|

| S.<br>No | Gate<br>Desig<br>ned                              | No.of<br>Transi<br>stors<br>used | Power dissipation(na nowatts) | Delay<br>(nanoSec<br>onds) | PDP<br>(attojo<br>ules) |  |  |  |  |

| 1        | EX-<br>OR                                         | 8                                | 6.4727                        | 50.002                     | 323.64<br>79            |  |  |  |  |

| 2        | EX-<br>OR                                         | 6                                | 5.6580                        | 50.034                     | 283.09<br>23            |  |  |  |  |

:The logic involved to design Ex-or gate is if inputs are two different logic then output is '1'. Otherwise if those two inputs are similar then output is '0'. So by using the both eight transistor Ex-or and six transistor we implemented the parity checker design.

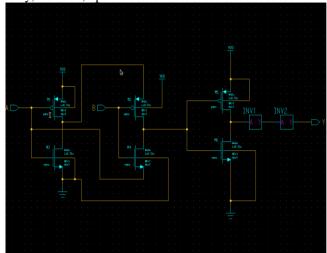

#### C. Design of Parity Checker:

Parity checker employs a key role in the digital communication for finding out the error bits. The procedure involved in this is if we sends the data from one stage to another stage in the middle there is chance of adding the noise that is the additional data gets added and then it reaches at the receiver. Because of this there is a possibility of modification in the transmitted data that is either from '0' to '1' or '1' to '0'. So to identify that error bit we used the parity bit at the edge of the message signal.

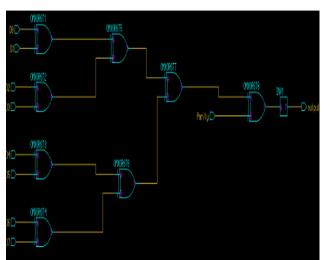

Fig.5: Schematic of Parity checker

## Table2: truth Table of Parity Checker

| S. No | Input Data          | Parity | Output |

|-------|---------------------|--------|--------|

|       |                     | Given  |        |

| 1     | Even number of ones | 0      | 1      |

| 2     | Even number of ones | 1      | 0      |

| 3     | Odd number of ones  | 0      | 0      |

| 4     | Odd number of ones  | 1      | 1      |

According to the table2 if there are even numbers of ones and if the given input parity bit is zero then the output values that is check shows '1'. In the same for even number of ones if the given parity bit is one then check shows the output as '1'. The parity checker for odd number of ones if the given parity bit is zero then check shows the output value as '1'. The parity checker for odd number of ones if the given parity bit is one then check shows the output value as '0'. So according to the truth table the schematic of parity checker works. The operation involved in parity checker is to identify the errors while sending the data. So the parity checker design first verifies the total number of logical ones is even or odd while transmitting the data. At the receiver it verifies the number of ones that the sent data and received data are same or not. The number of ones at the transmitted data is correlated with the parity bit, which was occurred due to parity producer and specifies the number of bits in advance of sending the data. If number of bits is equated, no errors are shown otherwise if the number of bits at the transmitter and receiver are not equal then there is an error in the data. The schematic is designed to result a '1' if the parity is equal, and a '0' if not.

#### III. SIMULATION RESULTS:

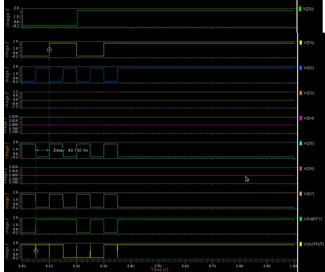

Fig.6: Simulated outcomes og Parity checker with eight transistor Ex-or design.

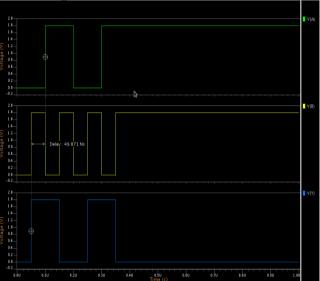

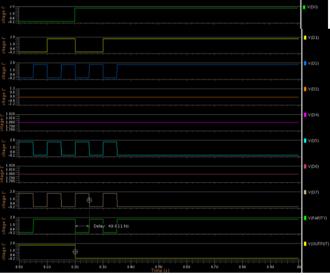

Fig. 7: Simulated outcomes of parity checker six transistor Ex-or design.

Table 3: Comparison table of Parity checker eight transistor Ex-or and Parity checker Six transistor Ex-or

| S. No | Ex-or used<br>to design<br>parity<br>checker | Power dissipation (nano watts) | Delay (nano<br>Seconds) | PDP (atto joules) |

|-------|----------------------------------------------|--------------------------------|-------------------------|-------------------|

| 1     | EX-OR 8T                                     | 47.1539                        | 49.795                  | 2348.0284         |

| 2     | EX-OR 6T                                     | 28.3703                        | 49.611                  | 1407.4789         |

In this the circuit is simulated by giving all the information bits to modify and to feed in all the probable amalgamations. In this we can check out all the 256 probable bit amalgamations at once, with odd and even parity bit. In this the outcomes are mainly focused to check the parity checker functionality. The focus is mainly verified only when the feed in parity bit is zero that is for the even parity check.

# Design a Low Power and High Speed Parity Checker using Exclusive-or Gates

And it shows that the schematic of parity checker is giving correct and proper functionality. But in this the result shows there is an observed delay. This occurred due to the philosophy schematic and the CMOS inverter utilized in the parity checker schematic. This is calculated by observing the time from edge to edge when the result gets modified. The power dissipation for the eight transistor Ex-or parity checker is 47.1539 nano watts and the delay is 49.795 nano seconds and PDP is 2348.0284 atto joules. And the implemented design six transistor Ex-or parity checker Power dissipation is 28.3703 nano watts and delay is 49.611 nano seconds and PDP is 1407.4789 atto joules. This design is implemented at the 1.8V Power supply.

## IV. CONCLUSION:

From the literature, it shows that the implemented design is more and well effective in terms of area, power, delay and PDP in correlation with the existed structure. So that the use of this implemented structure is taken into analysis because of the size, and the power delay product for this is very effective. The reduction in the schematic has minimized the constraints like power, delay and PDP among the previous structure. The necessity of the implemented design is more preferable while drawing the minimum outcomes than the previous structure. It clears that 59.57 % of power is reduced when compared to previous structure, likewise 0.0009% of delay is minimized when compared to previous structure, more over the 62.60% of total power delay product is reduced in comparison to the previous structure.

### **REFERENCES:**

- Sheldon B. Akers, "A Parity Bit Signature For Exhaustive Testing", IEEE Transactions on Computer-Aided Design, Vol. 7, No. 3, March 1988, pp. 333-338.

- Lowell H. Miles, "An 860-Mb/S (8158,7136) Low-Density Parity-Check Encoder", IEEE Journal of Solid-State Circuits, Vol. 41, No. 8, Aug. 2006, pp. 1686-1691.

- KuiCai, "A General Construction of Constrained Parity-Check Codes For Optical Recording", IEEE Transactions on Communications, Vol. 56, No. 7, July 2008, pp. 1070-1079.

- Travis R. Oenning, "A Low-Density Generator Matrix Interpretation of Parallel Concatenated Single Bit Parity Codes", IEEE Transactions on Magnetics, Vol. 37, No. 2, Mar. 2001, pp. 737-741.

- Jingnan Hu, "Block Markov Superposition Transmission of Repetition and Single-Parity-Check Codes", IEEE Communications Letters, Vol. 19, No. 2, Feb. 2015, pp. 131-134.

- Qin Huang, "Cyclic and Quasi-Cyclic LDPC Codes on Constrained Parity-Check Matrices and Their Trapping Sets", IEEE Transactions on Information Theory, Vol. 58, No. 5, May 2012, pp. 2648-2671.

- Anne Canteaut, "Parity-Check Relations on Combination Generators", IEEE Transactions on Information Theory, Vol. 58, No. 6, June 2012, pp. 3900-3911.

- Yuchen Jiang, "Optimized Design of Parity Relation Based Residual Generator for Fault Detection: Data-Driven Approaches", IEEE Transactions on Industrial Informatics, Vol. 17, Iss. 2, April 2020, pp. 1449-1458.

- DimitrisNikolos, "Optimal Self-Testing Embedded Parity Checkers", IEEE Transactions on Computers, Vol. 47, No. 3, March 1998, pp. 313-321.

- NorifumiKamiya, "High-Rate Quasi-Cyclic Low-Density Parity-Check Codes Derived From Finite Affine Planes", IEEE Transactions on Information Theory, Vol. 53, No. 4, April 2007, pp. 1444-1459.

- Dongying Chen, "Low-complexity High-performance Low-Density Parity-Check Encoder Design for China Digital Radio Standard", IEEE Access, Vol. 5, 2017, pp. 20880-20886.

- QiujuDiao, "A Matrix-Theoretic Approach For Analyzing Quasi-Cyclic Low-Density Parity-Check Codes", IEEE Transactions on Information Theory, Vol. 58, No. 6, June 2012, pp. 4030-4048.

- WittawatKositwattanarerk, "Lifting the Fundamental Cone and Enumerating the Pseudocodewords of a Parity-Check Code", IEEE

- Transactions on Information Theory, Vol. 57, No. 2, Feb. 2011, pp. 898-909

- T. Matsumoto, "Parity Generator Circuit Using a multistate Resonant tunneling Bi Polar Transistor", Electronics Letters, Vol. 24, No. 24, Nov. 1988, pp. 1506-1507.

- Chia-Fu Chang, "Advanced Information of Parity Bits for Decoding Short Linear Block Codes Using the A\* Algorithm", IEEE Transactions on Communications, Vol. 61, No. 4, April 2013, pp.1201-1211.

- SinaVafi, "Cyclic Low Density Parity Check Codes With the optimum Burst Error Correcting Capability", IEEE Access, Vol. 8, Nov. 2020, pp. 192065-192072.

- 17. Yulei Wang, "Data-Driven Design of Parity Space-Based FDI System for AMT Vehicles", IEEE/ASME Transactions on Mechatronics, Vol. 20, Iss. 1, Feb. 2015, pp. 405-415.

- Wen-Ben Jone, "Multiple Fault Detection in Parity Checkers", IEEE Transactions on Computers, Vol. 43, Iss. 9, Sep 1994, pp. 1096 – 1099.

- Hao Ye, "A New Parity Space Approach For Fault Detection Based on Stationary Wavelet Transform", IEEE Transactions on Automatic Control, Vol. 49, No. 2, Feb. 2004, pp. 281-287.

- Takeshi Suzuki, "Synonym Hit Ram—A 500-Mhz CMOS SRAM Macro With 576-Bit Parallel Comparison And Parity Check Functions", IEEE Transactions on Solid State Circuits, Vol. 35, No. 2, Feb. 2000, pp. 163-174.

- B. Comaglia, "Errored Block Detection with Bit Interleaved Parity Failures in SDH Network", IEEE Transactions on Communications, Vol. 43, No. 12, Dec. 1995, pp. 2904-2906.

- X. Ding, "A Characterization of Parity Space and its Application to Robust Fault Detection", IEEE Transactions on Automatic Control, Vol. 44, No. 2, Feb. 1999, pp. 337-343.

- HosseinFalsafain, "A Generator-Matrix-Based Approach for Adaptively Generating Cut-Inducing Redundant Parity-Checks", IEEE Communications Letters, Vol. 20, Iss. 4, April 2016, pp. 640 – 643.

- Tom Fuja, "Cross Parity Check Convolutional Codes", IEEE Transactions on Information Theory, Vol. 35, No. 6, Nov. 1989, pp. 1264-1276

- Ching-Yi Lai, "A Construction of Quantum Stabilizer Codes Based on Syndrome Assignment by Classical Parity-Check Matrices", IEEE Transactions on Information Theory, Vol. 57, No. 10, Oct. 2011, pp. 7163-7179.

- DipanwitaGangopadhyay, "Multiple-bit Parity-based Concurrent Fault Detection Architecture for Parallel CRC Computation", IEEE Transactions on Computers, Vol. 65, Iss. 7, July 2016, pp. 2143 – 2157.

- N. M. Martin, "Eleven-Bit Parity Generator with a Single, Vertically Integrated Resonant Tunneling Device", Electronics Letters, Vol. 24, No. 11, May 1988, pp. 681-683.

- Mu Zhang, "Density optimization of generator matrices of quasicyclic low-density parity-check codes and their rank analysis", IET Communications, Vol. 8, Iss. 14, 2014, pp. 2547–2555.

- Zongwang Li, "Efficient Encoding Of Quasi-Cyclic Low-Density Parity-Check Codes", IEEE Transactions on Communications, Vol. 54, No. 1, Jan. 2006, pp. 71-81.

# **AUTHORS PROFILE**

Brahmaiah Battula, Assistant Professor received his B.Tech degree from KIET, Korngi, Kakinada (D.t), Andhra Pradesh and M.tech from SMCET, Hyderabad, Andhra Pradesh. And have 8 years of teaching experience as an Assistant professor in various engineering colleges, Currently working as an Assistant professor in Department of ECE in KKR&KSR Institute of Technology and Sciences,

Vinjanampadu, Guntur (Dt), Andhra Pradesh, India. Totally 3 publications and 2 books are there in various journals. Areas of interests are Embedded Systems based wireless Communications, VLSI and IOT.

Valeti SaiLakshmi, Assistant Professor received her B.Tech degree from Sri Mittapalli College of Engineering, Tummalapalem, Guntur (D.t), Andhra Pradesh and M.tech from Sri Padmavathi Mahila University, Tirupathi, Andhra Pradesh. And have 1 years of teaching experience as an Assistant professor in various engineering colleges, Currently working as an Assistant professor in Department of ECE in Hindu

College of Engineering and Technology, Amaravathi Road, Guntur (Dt), Andhra Pradesh, India. Totally 1 publication are there in various journals. Areas of interests are VLSI, Signal Processing, and wireless communication.