# Low Noise and high linearity Wide-band Low Noise Amplifier for 5G Receiver Front End System

## M. Ramana Reddy

Abstract: This work Demonstrates a wideband LNA for 5G receiver front end modules with high linearity, Low noise reused topology has an inter stage wideband inductor based two common source cascade stages. The configuration provides the bias current; better Noise figure increases the forward gain. By providing RC Series network at gate terminal of second stage the return losses are reduced and stability will be increased. After pre and post simulation all parameters are better than the existing LNAS. After post simulation results, the Noise figure is achieved less than 1dB and forward gain as flat 16dB for wide band width of 1.5 - 5.5 GHz. At the 1dB compression point the output is 20dbm achieved and OIP3 IS +40dbm is achieved. The chip size of an LNA along with pad is 0.64mm2. The design is GaAspHEMT process at 50nm technology.

Keywords: LNA, OIP3, pHEMT, Noise figure, Forward gain.

## I. INTRODUCTION

Recent years the 5G communications systems are popular because of huge data rate, economical, high reliable small size. Theses all parameters are possible by chosen technology and selected band frequency. The preferable band frequencies for 5G IS SUB- 6 GHz and mw wave frequencies. Usually the mm wave frequencies are suitable for military applications. For 5G systems required many process steps for design and implementation to increase data rate, high reliable .increase the coverage area the transceiver required better sensitivity and more dynamic range.

The most important block in any receiver is LNA. The LNA can play an important role in the entire performance of receiver. The most important parameter in any LNA design and its performance forward gain S21, Input and output matching network Noise Figure, linearity, IIP3, OIP3 and 1dB compression point. The CMOS technology has drawback of highest Noise Figure, Small gain and less linearity. But low cost and better system integration [1] – [2]. The GA As, pHEMT process of technology of compound semiconductor (III -IV group periodic table components) process has Low Noise, high linearity advantages. This is widely used in in industry as well as academic fields [3]. In order to meet requirements the all existing published work papers authors suggested that different topologies andtechnology processes.

Manuscript received on March 30, 2021. Revised Manuscript received on April 05, 2021. Manuscript published on April 30, 2021.

\*Correspondence Author

M. Ramana Reddy\*, Department of ECE, Chaitanya Barathi institute of Technology, Osmania University, Hyderabad (Telangana), India Email: mramanareddy\_ece@cbit.ac.in

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC BY-NC-ND license (<a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>)

In reference [4] the authors suggested the current reuse technology with cascaded inter stage resonance is demonstrated for the design of LNA, but designis restricted for 5.2 GHz frequency with minimum substrate resistance. Similarly in gm boosting with current reuse technique is implemented. Similarly in reference [6] a 5.7 GHz differential mode LNA is designed. In this proposedLNA a wideband low noise, high linearity GaAs pHEMT technology with two stage common source transistor cascaded current reused technique with enhanced matchingnetwork at inter stage.

## II. PROCEDURE FOR PAPER SUBMISSION

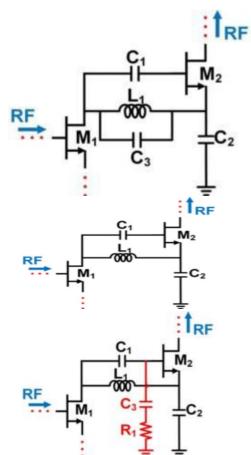

The two stages cascaded common source (cs) current reused topology the bias current is shared in two stages, so that the power consumption is reduced .The different types of current reuse topologies are shown in figure below.

Figure: 1 Different Current reused topologies a) Resistive b) Inductive c) LC Resonant based d) The proposed topology

Retrieval Number: 100.1/ijitee.F87180410621 DOI: 10.35940/ijitee.F8718.0410621 Journal Website: www.ijitee.org

From fig. 1.a resistance inter stage current reuse network reduces the voltage, but its noise characteristics increased the power consumption. Fig 1.b due to inductance the chip size will increase and it occupies large area, fig 1.c it also occupies more area but increases the gain. Fig 1.d the proposed two stages cascaded enhanced inters stage matching RC network helps to increases the gain, stability and return losses. The inter stage network can play an important role for better performance of the proposed wideband LNA design.

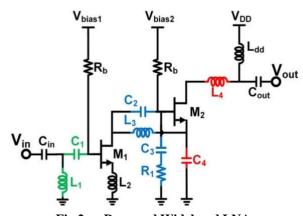

The proposed wideband LNA design schematic is shown in figure 2. An enhanced mode GaAs pHEMT process of 50nm technology achieved a better performance of parameters especially high linearity and Noise figure.

Table1: Proposed Values in wideband LNA design

| Table1: FToposed Values in wideband LNA design |                |  |  |  |  |  |

|------------------------------------------------|----------------|--|--|--|--|--|

| PARAMETER                                      | DESIGNED VALUE |  |  |  |  |  |

| $M_1$                                          | 8 × (0.75 μm)  |  |  |  |  |  |

| $M_2$                                          | 8 × (0.75 μm)  |  |  |  |  |  |

| Cin                                            | 100.0 pF       |  |  |  |  |  |

| Cout                                           | 100.0 pF       |  |  |  |  |  |

| R <sub>b</sub>                                 | 2.0 kΩ         |  |  |  |  |  |

| L <sub>dd</sub>                                | 18.0 nH        |  |  |  |  |  |

| V <sub>bias1</sub>                             | 0.6 V          |  |  |  |  |  |

| V <sub>bias2</sub>                             | 3.0 V          |  |  |  |  |  |

| $V_{DD}$                                       | 5.0 V          |  |  |  |  |  |

| $I_{DD}$                                       | 60.0 mA        |  |  |  |  |  |

Fig 2: **Proposed Wideband LNA**

The depletion mode required a negative power supply. So it is replaced with enhanced mode, to provide negative supply to depletion mode the number of components are increased so that chip size will increased. Hence the enhancement mode pHEMT transistor is chosen with gate width of 75 µm and number of figures are 8 for both stages in order to get better noise and linearity performance and also with 5v,60ma current supply. In the schematic C<sub>in</sub>, C<sub>out</sub> and  $L_{dd}$  are the external connections. The  $L_1$  and  $C_1$  is used as a input matching network. The source degenerated inductor is used for better input matching, so that decrease the Noise. The output matching is achieved by L4 and C4 at the M<sub>2</sub> transistor of source terminal .The RC network at the gate of transistor M2 is to increase stability and also improves the return losses. The inductor to be chooses in small size in order to reduce the chip size.

#### III. SIMULATED RESULTS AND DISCUSSIONS

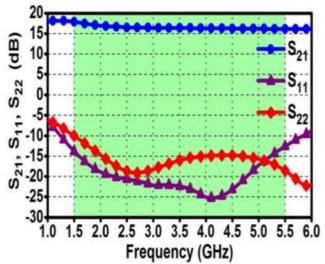

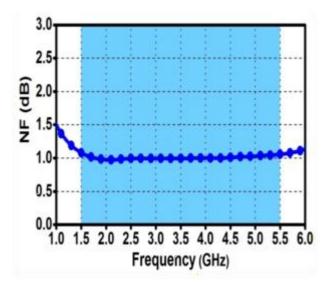

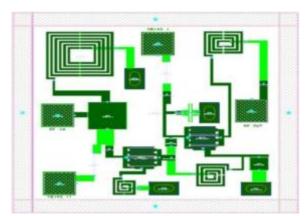

The post simulated results are achieved the better performance by EM simulator of Agilent ADS software. The proposed wideband LNA micrograph is shown in figure 3 and the occupied area of 0.64mm<sup>2</sup>. The proposed wideband LNA achieved better performance with single power supply 5V and it dissipates 300 mW. The S<sub>21</sub>, S<sub>11</sub> and S<sub>22</sub> parameters are simulated and shown in figure 4. A stable flat forward gain (S<sub>21</sub>) 16dB is achieved and shown in figure

5. The input / output return losses are less than -1db in the frequency range of 1.5GHz -5.5GHz. The reverse isolationis less than -25dB is achieved in the required band. The post layout simulation are shown figure infigure 5.

. Fig 3: Simulation results of S21, S11and S22

Fig.4: Simulation result of Noise Figure

Retrieval Number: 100.1/iiitee.F87180410621 DOI: 10.35940/ijitee.F8718.0410621 Journal Website: www.ijitee.org

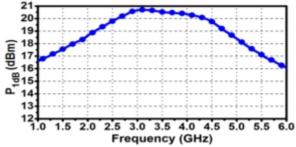

Fig.5: 1dB Compression point

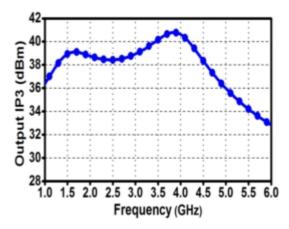

Fig.6: Output Interception Point (OIP3)

Fig.7: Micrograph for proposed Wideband LNA

Table: 2 Comparison of Parameters of references with present work

|               |          | present wo      | 1 17       |           |       |

|---------------|----------|-----------------|------------|-----------|-------|

| PARAME<br>TER | [10]     | [9]             | [8]        | [7]       | 0.5   |

|               |          |                 |            |           | μm    |

|               |          |                 |            |           | GaA s |

|               |          |                 |            |           | рНЕ   |

| Technology    | 0.35     | 0.50 μm         | 0.5        | 0.25      | MT    |

|               | μm       |                 | μm         | μm        |       |

|               |          | AlGaAs/G<br>aAs |            |           |       |

|               | GaN      |                 | In<br>GaAs | GaAs      |       |

|               | HE<br>MT | pHEMT           |            | pHEM<br>T |       |

|               |          |                 | pHE        |           |       |

Retrieval Number: 100.1/ijitee.F87180410621 DOI: 10.35940/ijitee.F8718.0410621 Journal Website: www.ijitee.org

|            |      |          | MT   |       |       |

|------------|------|----------|------|-------|-------|

| Freq (GHz) | 2 –  | 2.5 -5.0 | 3.5  | 1.5 - | 1.5 - |

|            | 4.5  |          |      | 2.7   | 5.5   |

| BW (GHz)   | 2.5  | 2.5      |      | 1.2   | 4.0   |

| Gain (dB)  | 17.2 | 17       | 16.7 | 17.5  | 16    |

| NF (dB)    | 2.9  | 3.0      | 1.8  | 0.75  | 1.0   |

| IRL/ORL(d  | <-9. | <-10     | <-9  |       | <-15  |

| B)         | 5    |          |      |       |       |

| OIP3       | -    | -        | -    | >34   | >34   |

| (dBm)      |      |          |      |       |       |

| P1db       |      | 2.3      | 10   |       | 17    |

| (dBm)      |      |          |      |       |       |

| Pdc (mW)   | 230  | 33       | 11.4 | 300   | 300   |

| Chip       | 2.25 | 1.5      |      | 1.948 | 0.64  |

| Area       |      |          |      |       |       |

other important parameter is Noise Figure (NF) is achieved the 1.5GHz - 5.5GHz wideband frequency range. The post layout simulation result of 1db compression point is 17dbm to 20.5dbm max over the frequency range of 1.5 to 5.5GHz as shown in figure 6. The OIP3 of the LNA is achieved up to 41dbm at 3.6GHz frequency. This wideband LNA of GaAs pHEMT achieved highest bandwidth, better Noise Figure, small chip size and achieve better linearity. Therefore this is very much suitable in 5G Communication receiver's front end

### IV. CONCLUSION

The proposed Ga As pHEMT process of wideband LNA is performed and evaluated at 50nm using current reuse topology. The design is achieved better performance for all the parameters to propose for 5G front end systems. An inductor based inter stage matching network improved the bandwidth. The RC cascade series network is connected at second stage is performed the better return losses and stability of the system by choosing transistor size and its biasing provided better Noise Figure. The Simulation result at post layout process forward gain of 16dB flat and Noise Figure achieved 1dB at a wideband width of 1.5GHz to 5.5GHz. The linearity achieved a +40dbm and OIP3 is achieved 20dbm at 1dB compression point. The chip size including pad is 0.64mm<sup>2</sup>.

## REFERENCES

20

- . K. Kang *et al.*, "A 60-GHz OOK receiver with an on-chip antenna in 90nm CMOS," *IEEE J. Solid-State Circuits*, vol. 45, no. 9, pp. 1720–1731,Sep. 2010.

- Y. Yu, H. Liu, Y. Wu and K. Kang, "A 54.4–90 GHz Low-Noise Amplifier in 65-nm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 52, no. 11, pp. 2892–2904, Nov. 2017

- 3. H. Morkner, M. Frank, and D. Millicker, "A high performance 1.5 dB low noise GaAs PHEMT MMIC amplifier for low cost 1.5-8 GHz commercial applications," in *IEEE Microwave Millimeter-Wave Monolithic Circuits Symp. Dig.* pp.13–16, 1993.

- C. Y. Cha and S. G. Lee, "A 5.2-GHz LNA in 0.35 μm CMOS utilizing inter-stage series resonance and optimizing the substrate resistance," *IEEE J. of Solid-State Circuits*, vol. 38, pp. 669-672, Apr.2003.

w.ijite

## Low Noise and high linearity Wide-band Low Noise Amplifier for 5G Receiver Front EndSystem

- H. Liao and H. R. Chuang, "A 5.7-GHz 0.18-µm CMOS gain controlled differential LNA with current reuse for WLAN receiver," *IEEE Microw. Wireless Compon. Lett.*, vol. 13, pp. 526-528, Dec. 2003.

- 6. J. S. Walling, S. Shekhar, and D. J. Allstot, "A gm-boosted Current-reuse LNA in 0.18 $\mu$ m CMOS," in IEEE Radio Freq. Integr. Circuits Symp., pp 613-616, June, 2007.

- 7. J. S. Yao, X. P. Sun, and B. Lin, "1.5–2.7 GHz ultralow noise bypass LNA," in IEEE MTT-S Int. Microw. Symp. Dig., June, 2014.

- Y. C. Hsu, P. H. Wu, C. C. Chen, J. Y. Li, S. F. Lee, W. J. Ho, and C. K. Lin, "Single-chip RF frontend MMIC using InGaAs E/D pHEMT for 3.5 GHz WiMAX applications," In European Microwave conference, pp. 1217-1220, Oct. 2007.

- Y. Y. Peng, X. Y. Wang, F. Y. Ma, and W. Q. Sui, "A low power S-band receiver using GaAs pHEMT technology," in IEEE 13th ISIC Symp. Dig., Dec., 2011.

## **AUTHORS PROFILE**

**Dr. M. Ramana Reddy**, a graduate in ECE from IETE, New Delhi and M.Tech (I&C) from JNTUK, and PhD from JNTUK, Kakinada. He is presently working as an Assistant Professor in the department of ECE, CBIT, and Hyderabad since 2004. His key area of research is VLSI Design in analog and digital systems, and has 14

publications in peer-reviewed international journals and conference proceedings. As a facilitator for continuous learning, he has brought together Faculty, Researchers, students and Industries, their publications, research work, membership, achievements.

Published By:

Blue Eyes Intelligence Engineering

and Sciences Publication

© Copyright: All rights reserved.