# A Novel 1-Bit Full Adder Design Using DCVSL XOR/XNOR Gate and Pass Transistor Multiplexers

#### P. Divakara Varma, R.Ramana Reddy

Abstract— Adders are the basic building blocks in digital computer systems. Arithmetic operations are widely used in most digital computer systems. Addition is a fundamental arithmetic operation and is the base for arithmetic operations such as multiplication and the basic adder cell can be modified to function as subtractor by adding another xor gate and can be used for division. Therefore, 1-bit Full Adder cell is the most important and basic block of an arithmetic unit of a system. Hence in order to improve the performance of the digital computer system one must improve the basic 1-bit full adder cell. There is always a trade-off between speed and power dissipation in VLSI Design. To achieve high speeds, high drivability hybrid-DCVSL design methodologies are used to build adder cell in this work. Static CMOS, DCVSL adders are compared with hybrid XOR and XNOR based hybrid adder cell for delay, power dissipation and number of transistors utilized. The hybrid adder is designed using DCVSL gates because these can produce both complementary and true outputs using single gate architecture. The multiplexers in the design are based on the pass transistor logic (PTL) because these are simple to construct and occupies less chip area per component.

Index Terms—DCVSL, Multiplexer, PTL, XOR/XNOR

#### I. INTRODUCTION

Low power and High speed are the design trade-offs in VLSI industry. Until recently performance has been synonymous with speed. Emergence of portable computing devices are enhancing the importance of low power design methodologies. In pass transistor logic, the transistors are used as voltage controlled switches to implement the logic. The PTL logic is bidirectional. There is no static power dissipation in PTL gates. The pass transistor logic suffers logic degradation at the output by an amount of Threshold Voltage (Vth). The advantage of Differential Cascode Voltage Switch Logic (DCVSL) is that it produces both true and complementary outputs when provided with true and complementary inputs. In DCVSL logic gates there is no static power dissipation (unlike static CMOS Ciruits). The hybrid Adder cell utilizes DCVSL logic for generation of

# Manuscript published on 30 March 2013.

\*Correspondence Author(s)

**P.Divakara Varma**, Department of Electronics and Communication Engineering, MVGR College of Engineering, Vizianagaram-AP, INDIA.

**Dr. R. Ramana Reddy**, Department of Electronics and Communication Engineering, MVGR College of Engineering, Vizianagaram-AP, INDIA.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license <a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>

XOR and XNOR outputs and PTL logic is used for the design of 2:1 multiplexer unit.

#### II. EXISTING ADDER DESIGNS

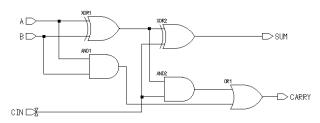

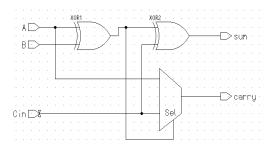

Basic full adder design

Fig. 1. Basic full adder

General expression for full adder is

$$Sum = A \oplus B \oplus C_{IN} \tag{1}$$

$$Carry = A \cdot B + A \cdot C_{IN} + B \cdot C_{IN}$$

(2)

From the basic full adder design shown in Fig. 1. sum is obtained by performing the Exclusive-OR function on all the inputs and Carry output is equal to same logic state when any two inputs are assigned with same state.

## A. Static CMOS full adder

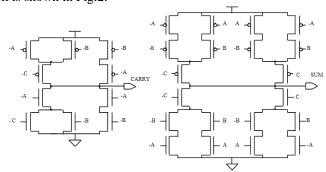

The Schematic Diagram of a 1-bit Static CMOS full adder cell is shown in Fig.2.

Fig. 2. Static CMOS 1- Bit full adder

The static CMOS consists of Pull-Up and Pull-Down networks. The PMOS transistors in Pull-Up network is the dual network of the NMOS Transistors in Pull-Down network.

The "-" sign on input terminals indicates the complementary signals. The advantage of CMOS logic is that it dissipates less dynamic power. The disadvantage of static CMOS logic is the higher propagation delays and require 2n transistors where n is the number of inputs and larger chip area and also suffers with low fan-out capability.

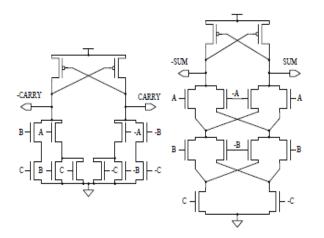

#### B. DCVSL full adder

Static DCVSL is a differential method which requires both true and complementary signals to be routed to gates. Two complementary nMOSFET switching trees are constructed to a pair of cross-coupled pMOSFET transistors. Depending on the differential inputs one of the outputs is pulled down by the corresponding nMOSFET network. The differential output is then latched by the cross-coupled pMOSFET transistors. Since the inputs drive only the nMOSFET transistors of the switching trees, the input capacitance is typically two or three times smaller than that of the conventional static CMOS logic. The advantage of DCVSL is in its logic density that is achieved by elimination of large pMOSFETs from each logic function. Both pull down networks in the Fig. 3 will never conduct at the same time.

Fig. 3. Basic architecture of DCVSL Logic

Fig. 4 shows the circuit diagram of the static DCVSL full adder.

Fig 4. Full adder implementation using DCVSL Logic

# III. 1-BIT FULL ADDER IMPLEMENTATION METHODOLOGIES

1-bit full adder can be implemented using

- 1. Two XOR gates and one 2:1 Multiplexer

- 2. Two XNOR gates and one 2:1 Multiplexer

- 3. One XOR gate, XNOR gate and two 2:1 Multiplexers.

#### Method -1

1-bit full adder using Two XOR gates and one 2:1 Mux

Expressions for Sum and Carry are given by equations (1) & (2). These can be rewritten as

$$Sum = X \oplus C_{IN} \tag{3}$$

where  $X = A \oplus B$

$$Carry = A \cdot X' + C_{IN} \cdot X \tag{4}$$

where X' is complement of X

Hence Sum can be implemented using two XOR gates. Carry can be implemented using a 2:1 multiplexer with A and  $C_{\rm IN}$  as input lines and X as selection line. The implementation is as shown in Fig.5.

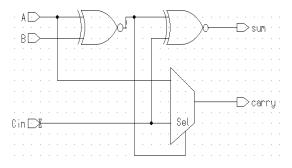

Fig. 5. 1-bit Full adder with XOR and 2:1 Multiplexers

### Method -2

1-bit full adder using Two XNOR gates and one 2:1 Mux

Expressions for Sum given in equations (3) can be rewritten as

$$Sum = (X' \oplus C_{IN})' \tag{5}$$

Hence Sum can be implemented using two XNOR gates. Carry can be implemented using a 2:1 multiplexer with A and  $C_{\rm IN}$  as input lines and X' as selection line. The implementation is as shown in Fig.6.

FIG. 6. 1-BIT FULL ADDER WITH XNOR AND 2:1 MULTIPLEXERS

#### Method -3

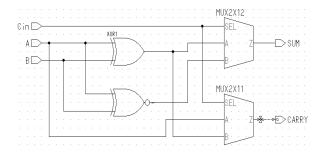

1-bit full adder using one XOR gate, one XNOR gates and two 2:1 Mux

In this method the expressions for Sum is obtained from expanding the equation (3) and carry is obtained from expression

$$Sum = X' C_{IN} + X C_{IN}'$$

and

$$Carry = A \cdot X' + C_{IN} \cdot X$$

(6)

The implementation is as shown in Fig.7.

Fig. 7. 1-bit Full adder with XOR, XNOR Gates and 2:1 Multiplexers

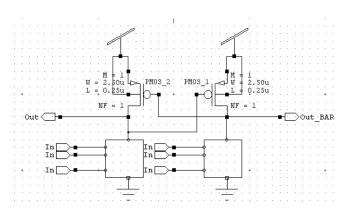

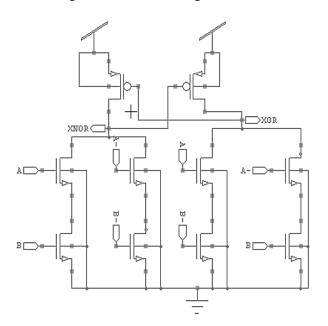

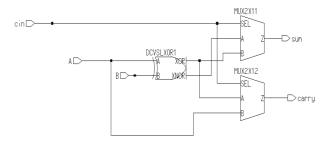

1-bit full adder in this paper is implemented using method 3 and designed using a DCVL XOR/XNOR gate. The advantage of DCVSL gates is that these gates can produce both true and complementary outputs i.e., both X and X', provided that true and complimentary inputs are available.

The 2:1 multiplexer is designed using pass transistor logic. The advantage of pass transistor logic is that it can be implemented using very less number of transistors, hence very less power dissipation. Lower noise margin is the disadvantage of Pass Transistor logic.

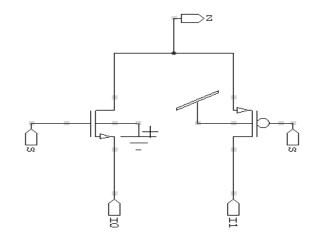

Fig. 8. XOR/XNOR implementation using DCVSL

Fig. 9. Multiplexer implementation using Pass Transistor Logic

Final circuit of 1-bit full adder using DCVSL gates and 2:1 Multiplexer is given below.

Fig. 10. 1-bit full adder implementation

#### IV. EXPERIMENTAL RESULTS

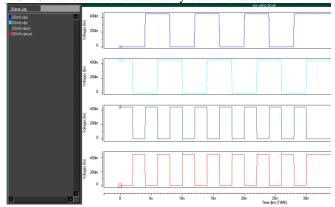

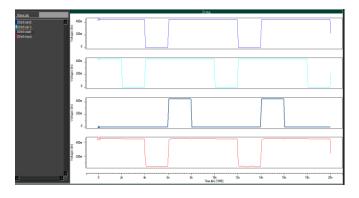

Extensive Simulations are carried out on Static CMOS adder as base case and performances of DCVSL and hybrid Full adder circuits are compared with that of base case. The simulations are carried out to calculate average power dissipation and delay using a set of input vectors for equal time periods. Tanner EDA tools are used to extract netlist and HSPICE software is used to carry out simulations.

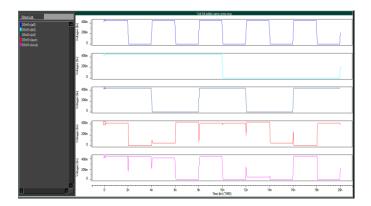

Fig 11. Waveforms of DCVSL XOR/XNOR gate

Fig 12. Waveforms of 2:1 Mux using Pass Transistor Logic

Fig 13. Waveforms of 1- bit fulladder using DCVSL XOR/XNOR gate and PTL 2:1 multiplexers

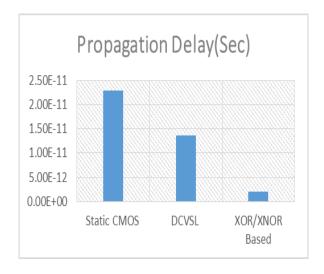

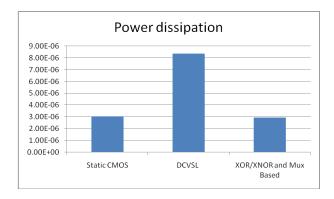

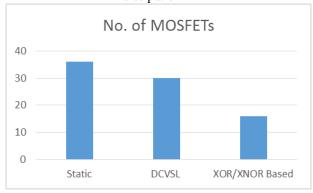

Table I. Experimental results

|                           | Delay (sec) | Power dissipation (Watts) | No. of<br>Transistors |

|---------------------------|-------------|---------------------------|-----------------------|

| Static CMOS               | 2.29E-11    | 3.05E-06                  | 36                    |

| DCVSL                     | 1.36E-11    | 8.38E-06                  | 30                    |

| XOR/XNOR<br>and Mux Based | 1.98E-12    | 2.96E-06                  | 12                    |

Fig. 14. Implementation technique Vs Propagation Delay

Fig. 15. Implementation technique Vs Dynamic Power dissipation

Fig. 16. Implementation technique Vs No. of MOSFETs required

#### V. CONCLUSIONS

From the results it can be observed that the propagation delay and number of transistors required is reduced in 1-bit full adder implementation using DCVSL technique compared to static CMOS technique. But dynamic power dissipation is increased. This drawback can be overcome by implementing adder cells using XOR/ XNOR and multiplexer in DCVSL methodology. It can be observed that Propagation delay, dynamic power dissipation and requirement of no. of transistors had been reduced remarkably. The problem with pass transistor based multiplexer is that there is logic degradation in the output. When implemented with NMOS pass transistor, the output is decreased by Vth when transmitting logic '1' to the output. This can be eliminated by utilizing the Transmission gate technology or using additional inverters at output stages. In both cases there is need for additional transistors and hence increase in power dissipation and effective chip area.

#### REFERENCES

- John P. Uyemura, (2002) Introduction to VLSI Circuits and Systems, John Wiley & Sons.

- H.T. Bui, Y. Wang and Y. Jiang, "Design and analysis of low-power 10-transister full adders using XOR-XNOR gates," IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process, Vol. 49, no. 1, pp. 25-30, Jan. 2002.

- K. Navi, O. Kaehi, M. Rouholamini, A. Sahafi, S.Mehrabi, N. Dadkhahi, "Low power and High performance 1-bit CMOS fill adder for nanometer design". IEEE computer Society Annual Symposium VLSI (ISVLSI), Montpellier fr, 2008, pp.

- Subodh Wairya, Rajendra Kumar Nagaria and Sudarshan Tiwari, (2011) "New Design Methodologies for High-Speed Low-Voltage 1 Bit CMOS Full Adder Circuits," Journal of Computer Technology and Application, Vol. 2, No. 3, pp. 190-198.

- Sumeer Goel, Mohammed A. Elgamel, Magdy A. Bayoumi, Yasser Hanafy, (2006) "Design Methodologies for High-Performance Noise-Tolerant XOR-XNOR Circuits," IEEE Transactions on Circuits and Systems- I, Vol. 53, No. 4, pp. 867-878.

- Design of Energy efficient Full adder using hybrid CMOS logic style Mohammad Shamim Imtiaz, Md Abdul Aziz Suzon, Mahmudur Rahman, International Journal of Advances in Engineering & Technology, Jan 2012.

- Analysis of Several 2:1 Multiplexer Circuits at 90nm and 45nm Technologies, Ila Gupta, Neha Ârora, Prof. B.P. Singh, International Journal of Scientific and Research Publications, Volume 2, Issue 2, February 2012

- Subodh Wairya, Garima Singh, Vishant, R. K. Nagaria and S. Tiwari (2011), "Design Analysis of XOR (4T) based Low Voltage CMOS Full Adder Cell," In Proceeding of IEEE International Conference on Current Trends In Technology (NUiCONE'11), Ahmedabad, India pp. 1-7.

- Subodh Wairya, Rajendra Kumar Nagaria and Sudarshan Tiwari Comparative Performance Analysis of XORXNOR Function Based High-Speed CMOS Full Adder Circuits For Low Voltage VLSI Design, International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.2, April 2012

- 10. A New Static Differential CMOS Logic with Superior Low Power Performance Muhammad E.S. Elrabaa Analog Integrated Circuits and Signal Processing, 43, 183–190, 2005

- Design Of Energy-Efficient Full Adder Using Hybrid-CMOS Logic Style Mohammad Shamim Imtiaz, Md Abdul Aziz Suzon, Mahmudur RahmanInternational Journal of Advances in Engineering & Technology, Jan 2012.

#### **AUTHOR PROFILE**

P. DIVAKARA VARMA, Received his bachelor's degree in Electronics and Communication Engineering form Andhra University, Visakhapatnam. Presently pursuing Masters degree (M.Tech) in VLSI Design from JNT University, Kakinada. His research interests include Low Power VLSI, VLSI system Design

Dr. R. RAMANA REDDY did AMIE in ECE from The Institution of Engineers (India) in 2000, M.Tech (I&CS) from JNTU College of Engineering, Kakinada in 2002, MBA (HRM & Marketing) from Andhra University in 2007 and Ph.D in Antennas in 2008 from Andhra University. He is presently working as Professor & Head, Dept. of ECE in MVGR College of Engineering, Vizianagaram. Coordinator, Center of

Excellence - Embedded Systems, Head, National Instruments LabVIEW academy established in Department of ECE, MVGR College of Engineering. Convenor of several national level conferences and workshops. Published about 31 technical papers in National/International Journals / Conferences. He is a member of IEEE, IETE, ISTE, SEMCE(I), IE,ISOI. His research interests include Phased Array Antennas, Slotted Waveguide Junctions, EMI/EMC, VLSI and Embedded Systems.