# Design and Implementation of Impulse Distributed Waveform Generator Time Interleaved Impulse Generator

# S.Janaki, Siva Yellampalli

Abstract—This paper presents the design and implementation of impulse distributed waveform generator which generates UWB pulses with a bandwidth of 7GHz (1GHz to 8GHz). It utilizes time interleaved impulse generators to generate waveforms. Wide bandwidth is achieved by reducing the width of the impulses generated by time-interleaved impulse generators. Each of the impulse generators are triggered by the tunable delay unit which introduces the delay between the impulses generated. The Pulse shaping circuit shapes the impulses, by pulse amplitude tuning. The amplitude tuned impulses are combined together to obtain the waveform by using on-chip transmission line. Pulse width tuning and delay tuning makes this circuit reconfigurable. The pulse width can be tuned from 80ps to 1ns, and trigger delay can be varied from 30ps to 100ps.

Index Terms—delay tuning, impulse generator, pulse width tuning, time-interleaved.

#### I. INTRODUCTION

Ultra Wide Bandwidth radio has become a very promising wireless technology. It possesses major attractive advantages in wireless communications, networking, radar, imaging, and positioning systems. It provides extremely broad bandwidth for transmission and very high data rate by generating and processing high speed pulses [1].UWB transmissions transmit information by generating radio energy at specific intervals and occupying a large bandwidth. In pulse based UWB, the pulses are very short, in subnano second time resolution, so most signal reflections do not overlap the original pulse and the multipath fading of narrow band signals does not exist. [2] So, the basic requirements of UWB systems are to achieve the large signal bandwidth, to generate and process the UWB pulses with sub-nano second time resolution and also to achieve this with low power consumption and small circuit complexity which translates into low cost.

A fully integrated UWB transceiver in CMOS technologies can be given as a solution for the above requirements of sub nano-second pulse generation and low power consumption. [3]. The existing system of UWB waveform generation has a pulse bandwidth of 5GHz(.5GHz to 5.5GHz), the minimum

#### Manuscript published on 30 June 2013.

\*Correspondence Author(s)

S.Janaki, VLSI Design and Embedded System, Visveswaraiah technological University/ VTU Extension Centre, UTL Technologies Ltd.,Bangalore,India.

Dr. Siva Yellampalli, VLSI Design and Embedded System, Visveswaraiah technological University,VTU Extension Centre, UTL Technologies Ltd., Bangalore, India.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license http://creativecommons.org/licenses/by-nc-nd/4.0/

time delay of 104ps and the generated impulse has a minimum pulse width of 140ps.[3].

The main objective of this work is to increase bandwidth compared to the existing system. Bandwidth can be increased by reducing the pulse width [4] and also by reducing the trigger delay. [5].

Pulse width can be reduced by reducing the charging time of the feedback path of the impulse generators and the trigger delay can be reduced by properly choosing the size of the current starved inverter used in the delay unit. In this work, the minimum pulse width is achieved as 80ps and the minimum trigger delay is achieved as 30ps. Thus, the bandwidth has been increased upto 7GHz (1GHz to 8GHz), which is higher compared to the existing work.

In this paper, the impulse distributed waveform generator is designed in .18µm CMOS technology and can achieve a bandwidth of 7GHz from 1GHz to 8GHz. The delay unit is implemented to introduce the delay between the trigger signals. The impulse generators are implemented to generate the impulses. The switched current source is implemented to shape the amplitude of the individual impulses. The on-chip transmission line is implemented to combine all the impulses to generate the waveform.

Impulse Distributed Waveform Generator is explained briefly in Section – II. The circuit implementation of all the blocks is discussed in Section-III. Experimental results as compared to the existing work are shown in Section-IV. Conclusion is given in Section-V.

# II. IMPULSE DISTRIBUTED WAVEFORM **GENERATOR**

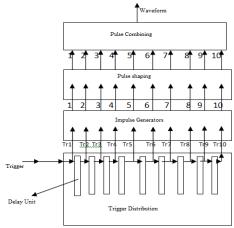

Fig. 1 shows a 10-tap impulse distributed waveform generator implemented in 0.18µm CMOS technology. The designed circuit consists of the following sub-blocks such as trigger distribution block, impulse generator, pulse shaping block, and pulse combining block. To the circuit a trigger signal i.e. the base band data is given as the input .The purpose of the trigger distribution block is to introduce delay between the inputs applied to the two consecutive impulse generators. So the output of the delay unit should be the same as the input but with a delay.

# A. Time-Interleaved Impulse Generator

The delayed trigger signal is distributed to each impulse generator, which enables narrow basis impulses to be generated at a specific sampling time by one of the impulse generators. The rate of the trigger signal may vary from KHz to MHz, based on the baseband data.

Whenever, there is a pulse in the baseband data, the impulses are generated. i.e. the impulse generator and other circuits operate only when a pulse is transmitted. Thus the power consumption reduces considerably, which explains the major benefit of time- interleaved architecture. Also, the pulse shapes are predetermined and do not change in real time. The above two characteristics makes the Time – interleaved Impulse Generators suitable for UWB pulse generation. [3]. The technique of time interleaving has been used to achieve higher sampling rate [3]. The overall sampling rate  $F_s$  is given by

$$F_s = f_s \times N$$

-----(1)

Where  $f_s$  is the sampling clock frequency of each impulse generator, and N is the number of impulse generators. i.e.,  $f_s$  can be effectively lowered by N. So, 10 tap time interleaving is chosen to generate a 1ns UWB pulse with 100ps delay between each. i.e. a sampling rate of 10GSamples/s. [3]

All the impulses are assumed to have uniform shape and amplitude. Amplitude and the shape of the waveform are tuned by pulse shaping block. Every impulse can be processed individually. Here, we use impulse to emphasize the pulse generated by each impulse generator is ultra-short, and to distinguish it from the overall generated UWB pulse. An on chip transmission line is used to combine the conditioned impulses. The output impedance of the pulse conditioner is modeled as  $G_0$  and  $C_0$  which loads the transmission line. Conditioned impulses forms a travelling wave on the loaded transmission line. Such a distributed circuit structure extends the bandwidth at the output node [3] – [5].

Fig. 1 Block Diagram of Impulse Distributed Waveform Generator

## III. CIRCUIT IMPLEMENTATION

# A. Trigger Distribution Block

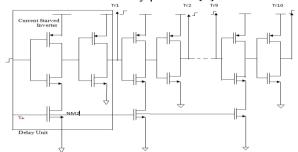

The trigger distribution block consists of 10 delay units to introduce delay. The circuit for the delay unit is shown in fig.2 [3] It consists of two stages of inverter. The first stage is an asynchronous, current starved active delay line, to achieve low power and large tuning range [3]. The second stage is an inverter just to obtain the same trigger signal at the output. The delay per unit is designed to be from 30 to 100ps and can be tuned by varying the delay tuning voltage  $V_{\rm dt}$ .  $V_{\rm dt}$  determines the drain current of the first stage inverter and also changes the fall time of the current starved inverter. A single  $V_{\rm dt}$  is used for all delay units and all the delay units produce uniform delay. The advantage is the trigger signal

runs at the pulse repetition Frequency (PRF), which is usually much lower than the RF Nyquist rate [4].

Fig.2 Trigger distribution block

# B. Impulse Generators

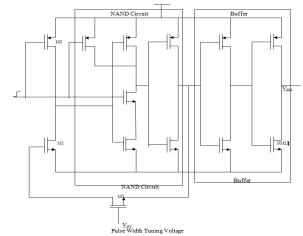

The impulse generator is shown in the fig3. The circuit consists of a NAND circuit, and a feedback loop, followed by two stage inverter. A short impulse is generated by the NAND operation of the input trigger signal and its delayed version. The delay time in the feedback loop, which consists of the propagation delay of NAND gate, the following inverter and the charging time of M1, determines the pulse width. The feedback loop has a NMOS transistor M3 as a voltage controlled transistor. By varying the width-tuning voltage,  $V_{\rm wt}$  the time constant of the charging path of M1 changes, which changes the pulse width [3]. The narrow basis pulses are generated at a specific sampling time by one of the impulse generators. The impulses generated can be expressed in the time domain

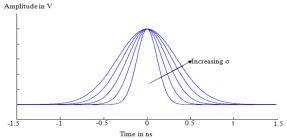

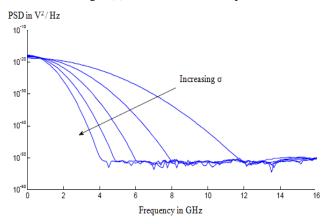

$$X(t) = \frac{A}{\sqrt{2\pi\sigma}} \exp\left(-\frac{t^2}{2\sigma^2}\right) \quad ----(2)$$

where A is the magnitude factor and  $\sigma$  is the pulse shape factor controlling the pulse width [4].Fig.4(a) and Fig.4(b) shows that the generated impulse in the time domain and its corresponding Power Spectral Density (PSD).It also explains that the impulse generated is with the smaller  $\sigma$ , pulse width is smaller and the bandwidth is larger. For UWB communication applications, the pulse width of the UWB pulse has to be smaller than 1 nanosecond i.e. the impulse width has to be less than 100ps, to cover the designated frequency band. [4].

Fig.3 Impulse Generator

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.

Fig.4 (a) Time Domain of Impulse

Fig.4 (b) Frequency Domain of Impulse

In this work, minimum width of the impulse is achieved as 80ps, which is considerably smaller compared to the existing work, which implies considerable increase in the bandwidth.

## C. Pulse Shaping & Combining Circuit

The Switched current source is used in the pulse shaping circuit. It can change the impulse amplitude, which is equivalent to multiplying each generated pulse x(t) by a coefficient. Each impulse can be independently conditioned, i.e., changed to desired pulse shape, polarity and amplitude in each path called tap, and then combined to form the output pulse waveform by a wide-band pulse combining circuit [3]. The output of a DWG in the time domain is given as

$$y(t) = \sum_{k=1}^{N} c_k x(t - T_d)$$

-----(3)

where  $c_k$  is the tap coefficient, and  $T_d$  is the delay on the trigger distribution. The output waveform y (t) is determined by three factors, the coefficients  $c_k$ , the delay  $T_d$  and the pulse shape x (t) generated by each impulse generator. The frequency response is given by

$$y(j\omega) = x(j\omega) \sum_{k=1}^{N} c_k \exp(-j\omega T_d)$$

(4)

$$= x(j\omega)H(j\omega)$$

where

$$H(j\omega) = \sum_{k=1}^{N} c_k \exp(-j\omega T_d)$$

----(5)

x (j $\omega$ ) is the spectrum of the impulse signal x (t), and H (j $\omega$ ) is the transfer function of pulse shaping circuit. The impulse response of impulse signal

$$h(t) = \sum_{k=1}^{N} c_k x(t - T_d)$$

----(6)

Thus, the output spectrum can be changed by changing width of the impulses generated as well as by reducing the trigger delay. [3].

# Retrieval Number: A0933063113/13©BEIESP Journal Website: www.ijitee.org

#### IV. MEASUREMENT RESULTS

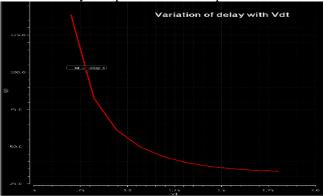

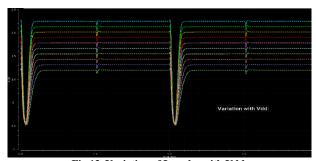

The circuit is implemented in  $0.18\mu m$  CMOS technology with the supply voltage as 1.8V. A 200MHz step signal is used as the input trigger. Fig.5 shows the variation of delay with  $V_{dt}$ . The delay tuning voltage  $V_{dt}$  is varied from 0.7~V to 1.8V. The delay is 30ps at 1.8V and 130ps at 0.7V.

Fig.5. Variation of Delay with Vdt

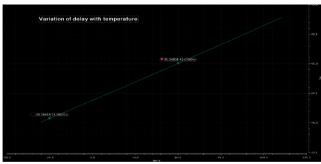

Fig.6. Variation of Delay with Temperature

It has a minimum delay of 30ps, which is considerably less compared to the existing system which implies reduced width of generated UWB pulse. The timing accuracy is determined by the delay and hence it is affected by process, voltage and temperature variations. Fig.6 shows the variation of delay with the temperature. The temperature is varied from -30°C to 110°C, and the variation in the delay is observed as 35.3ps to 43.5ps which is also lesser than the existing system[3].

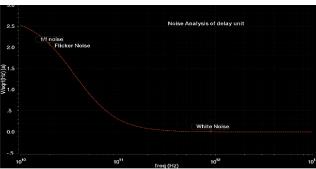

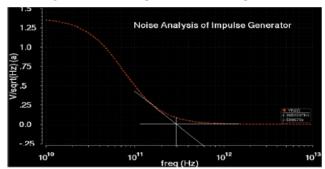

Fig.7 Noise Analysis of Delay unit

The noise contributed by the delay unit is observed from the noise analysis shown in Fig.7. The white noise at high frequency is  $2 \times 10^{-21}$  V/sqrt (Hz) or V<sup>2</sup>/Hz and the flicker noise is  $1.19444 \times e^{-35}$  V<sup>2</sup>/Hz. The Total Summarised Noise is  $2.52552 \times e^{-18}$  V<sup>2</sup>/Hz. The summary states that noise contributed by NM2 (Fig.2) is 99.56%, and contributions of other components are negligible or almost zero.

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.

157

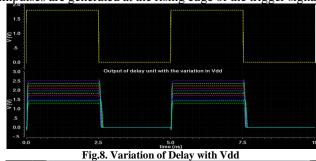

So, it is understood that noise is only because of the component NM2, and if the size of that particular transistor can be increased without affecting the output of the delay unit, the noise can be reduced. Table 1 &2 summarizes the noise optimization by increasing the size of NM2.Further increase in the size of NM2 distorts the expected output. Table 1 summarizes the noise contribution before optimization and Table 2 summarizes the noise after optimization. Fig.8 shows the parametric analysis of variation of V<sub>dd</sub>.

TABLE 1 - NOISE SUMMARY - 1 DELAY UNIT

| Noise as per the initial Design $W_{\text{NM2}} = 2\mu$ |                          |

|---------------------------------------------------------|--------------------------|

| Total Summarised Noise                                  | 2.52552e <sup>-18</sup>  |

| Noise Contributed by NM2                                | 2.51436 e <sup>-18</sup> |

| Noise due to Drain current                              | 2.50603 e <sup>-18</sup> |

| Noise due to r <sub>d</sub>                             | 4.21165 e <sup>-21</sup> |

| Noise due to r <sub>s</sub>                             | 4.1224 e <sup>-21</sup>  |

| Flicker noise component                                 | 1.19444 e <sup>-35</sup> |

TABLE2 NOISE SUMMARY -2 DELAY UNIT

| Noise after optimization $W_{NM2} = 5\mu$ |                          |

|-------------------------------------------|--------------------------|

| Total Summarised Noise                    | 1.31687 e <sup>-18</sup> |

| Noise Contributed by NM2                  | 1.31162 e <sup>-18</sup> |

| Noise due to Drain current                | 1.30729 e <sup>-18</sup> |

| Noise due to r <sub>d</sub>               | 2.18984 e <sup>-21</sup> |

| Noise due to r <sub>s</sub>               | 2.13954 e <sup>-21</sup> |

| Flicker noise component                   | 1.56906 e <sup>-36</sup> |

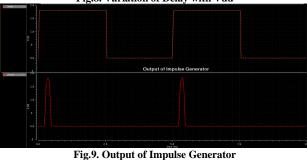

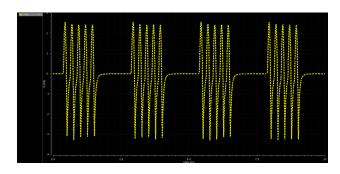

The supply voltage is 1.8V. But, the circuit can tolerate the change in the supply voltage from 1.3V to 2.5V.i.e, a tolerance of  $\pm 0.6$ V, and can produce an undistorted output. Fig.9 shows the output of the impulse generator. The impulses are generated at the rising edge of the trigger signal.

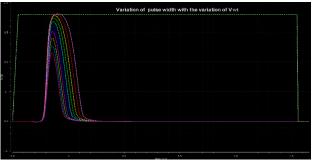

Fig. 10 shows the variation of width of the impulses generated The pulse width can be varied from 80ps to 1ns. Vwt is varied from 1.8 V to 0.7V. As the controlling voltage decreases, the pulse width increases. The minimum pulse width is obtained as 80ps which is lesser than the existing system having minimum pulse width as 132ps.

Fig.10.Variation of Impulse Width with Vwt

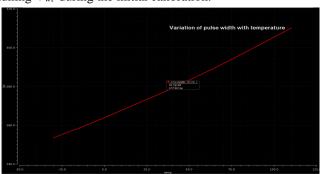

Fig.11 shows the variation of width with temperature. Variation is from 252ps to 312ps. The difference is 60ps, which is preferable for this circuit and can be compensated by tuning V<sub>wt</sub> during the initial calibration.

Fig.11. Variation of Impulse width with Temperature

Fig.12. Noise Analysis of Impulse Generator

Fig.12 shows the noise analysis for the impulse Generator. The corner frequency is observed as  $2.9 \times 10^{11}$  Hz. And the white noise is observed as  $2.589678 \times 10^{-21}$ . Flicker noise is dominant in the frequency range of operation of this circuit. The Total Summarised Noise is  $2.66901 \times e^{-18} \, V^2 / Hz$ . The summary states that noise contributed by NM12 (Fig.3) is 99.64%, and contributions of other components are negligible or almost zero. So, it is understood that noise is only because of the component NM12, and if the size of that particular transistor can be increased without affecting the output of the delay unit, the noise can be reduced. Table 3 summarizes the noise contribution of NM12. The optimized noise summary is summarized in Table 4.

Fig13 shows the parametric analysis of variation of V<sub>dd</sub>. The supply voltage is 1.8V. But, the circuit can tolerate the change in the supply voltage from 1.2V to 2.5V.i.e, a tolerance of  $\pm 0.7$ V, and can produce an undistorted output.

#### TABLE 3 NOISE SUMMARY 1 IMPULSE GENERATOR

| Noise as per the initial Design W <sub>NM12</sub> = 5µ |                          |

|--------------------------------------------------------|--------------------------|

| Total Summarised Noise                                 | 2.66901e -18             |

| Noise Contributed by NM12                              | 2.65942 e <sup>-18</sup> |

| Noise due to Drain current                             | 2.65061 e <sup>-18</sup> |

| Noise due to r <sub>d</sub>                            | 4.45394 e <sup>-21</sup> |

| Noise due to r <sub>s</sub>                            | 4.35654 e <sup>-21</sup> |

| Flicker noise component                                | 1.07001 e <sup>-37</sup> |

TABLE 4 NOISE SUMMARY 2 IMPULSE GENERATOR

| Noise after optimization $W_{NM12} = 10\mu$ |                          |

|---------------------------------------------|--------------------------|

| Total Summarised Noise                      | 1.34998 e <sup>-18</sup> |

| Noise Contributed by NM2                    | 1.34637 e <sup>-18</sup> |

| Noise due to Drain current                  | 1.34193 e <sup>-18</sup> |

| Noise due to r <sub>d</sub>                 | 2.24201 e <sup>-21</sup> |

| Noise due to r <sub>s</sub>                 | 2.19908 e <sup>-21</sup> |

| Flicker noise component                     | 1.36375 e <sup>-38</sup> |

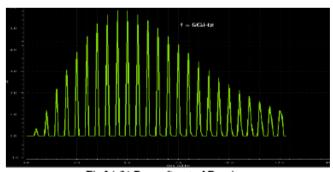

Fig.13. Variation of Impulse with Vdd is an example waveform synthesised by this

design, which has a pulse width of 0.8ns and Fig.14(b) shows Power Spectral Density which covers a band of 7GHz from 1GHz to 8GHz, with a center frequency of 5GHz.

Fig.14 (a) Waveform Synthesised by all 10 taps

Fig.14 (b) Power Spectral Density

#### V. CONCLUSION

Thus, the Impulse Distributed Waveform Generator is implemented using 0.18µm technology. The minimum impulse width is achieved as 80ps, and the minimum trigger dealy is achieved as 30ps, which leads to the generation of UWB waveform with a bandwidth of 7GHz (1GHz to 8GHz).

#### VI. ACKNOWLEDGMENT

I acknowledge Dr.V.Venkateshwarlu, Principal, UTL Technologies Ltd., for the encouragement to carry out this project, also I thank my colleagues, who has helped me to submit the paper to the journal.

#### REFERENCES

- JU-CHING LI, " The Design of CMOS Impulse Generators for Ultra-WideBand Communication and Radar Systems", The University of Texas at Arlington, August 2011., pp. 123–135.

- A. Jha, R. Gharpurey, and P. Kinget, "Quadrature-DAC based pulse generation for UWB pulse radio transceivers," Circuits and Systems, 2006. ISCAS 2006. Proceedings. 2006 IEEE International Symposium on, vol., no., pp.4 pp., 0-0 0, 2006.

- Yunliang Zhu, Member, IEEE, Jonathan D. Zuegel, John R. Marciante, and Hui Wu, Member, IEEE, "Distributed Waveform Generator: A New Circuit Technique for Ultra- Wideband Pulse Generation Shaping and Modulation", IEEE Journal of Solid State Circuits, Vol. 44, No. 3, 808-823, March 2009.

- Shin-Chih Chang, "CMOS 5th derivative Gaussian Impulse Generator for UWB application", The University of Texas at Arlington. December -2009

- Y. Zhu, J.D. Zuegel, J.R. Marciante, H. Wu, "A 10GS/s Distributed Waveform Generator for Subnanosecond Pulse Generation and Modulation in 0.18um standard Digital CMOS", inProc. IEEE Radio Freq. Integrated Circuit Symp., 2007.

- Yunliang Zhu\_, Jonathan D. Zuegel\_, John R. Marciante\_, and Hui Wu,"A 10.9 GS/s, 64 Taps Distributed Waveform Generator with DAC-Assisted Current-Steering Pulse Generators in .18µm Digital CMOS",IEEE Topical meeting on Silicon Monolithic Integrated Circuits in RF Systems, 2008.

- Sanghoon Sim, Dong-Wook Kim, Member, IEEE, and Songcheol Hong, *Member*, *IEEE*, "A CMOS UWB Pulse Generator for 6 – 10 GHz Applications", IEEE Microwave and Wireless Components Letters, Vol. 19, NO.2, 83-85, February 2009.

- W. C. Black and D. A. Hodges, "Time interleaved converter arrays," IEEE J. Solid-State Circuits, vol. SC-15, pp. 1022–1029, Dec. 1980.

- T.A Phan et al., "A 18-pJ/pulse OOK CMOS transmitter for multiband UWB impulse radio, "IEEE Microw. Wireless Compon, Lett., Vol.17, pp.688 -690, sep. 2007

- 10. D. D. Wentzloff and A. P. Chandrakasan, "Gaussian pulse generators for subbanded ultra-wideband transmitter," IEEE Trans. Microw. Theory Tech., vol. 54, no. 4, pp. 1647–1655, Apr. 2006.

- 11. S.-C. Chang, S. Jung, S. Tjuatja, J. Gao, and  $\hat{Y}.$  Joo, "A CMOS  $5^{th}$ derivative impulse generator for an IR-UWB," in Proc. 49th IEEE Int. Midwest Symp. Circuits and Systems, 2006 (MWSCAS'06), Aug. 2006, vol. 2, pp. 376-380.

- 12. S. Kozu et al., "A 100 MHz 0.4WRISC processor with 200 MHz multiply- adder, using pulse-register technique," in IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, 1996, pp. 140-141.