# Waveform Analysis of New Diode Clamped and Cascaded H-Bridge Multilevel Inverters with PWM Technique

N. Mohan Teja, R S Ravi Sankar, Talath Anjum, P.Sanjay

Abstract— This paper presents the waveform analysis of new diode clamped and cascade H-bridge multilevel inverters using Pulse width modulation technique. Multilevel voltage source converters are emerging as a new breed of power converter options for high-power applications. The multilevel voltage source converters typically synthesize staircase voltage wave from several levels of dc capacitor voltages. One of the major limitations of the multilevel converters is the voltage unbalance between different levels. The techniques to balance the voltage between different levels normally involve voltage clamping or capacitor charge control. An analysis of how existing multilevel carrier-based PWM affect switch utilization for the different levels of a new diode clamped and H-bridge inverter are conducted and compared.

Index Terms - Clamping Diodes, cascaded H-bridge inverter, Multi Level Inverter, Pulse Width Modulation

#### I. INTRODUCTION

The concept of multilevel converters has been introduced since 1975. The term multilevel began with the three-level converter. Subsequently, several multilevel converter topologies have been developed. However, the elementary concept of a multilevel converter to achieve higher power is to use a series of power semiconductor switches with several lower voltage dc sources to perform the power conversion by synthesizing a staircase voltage waveform. Capacitors, batteries, and renewable energy voltage sources can be used as the multiple dc voltage sources. The commutation of the power switches aggregate these multiple dc sources in order to achieve high voltage at the output. However, the rated voltage of the power semiconductor switches depends only upon the rating of the dc voltage sources to which they are connected. A multilevel converter has several advantages over a conventional two-level converter that uses high switching frequency pulse width modulation (PWM). The attractive features of a multilevel converter can be briefly summarized as follows. Staircase waveform quality: Multilevel converters not only can generate the output voltages with very low distortion, but also can reduce the dv/dt stresses; therefore electromagnetic compatibility (EMC) problems can be reduced. Multilevel converters produce smaller Common-mode (CM) voltage.

#### Manuscript published on 30 March 2014.

\*Correspondence Author(s)

N. Mohan Teja, Vignan's Institute of Information Technology, Duvvada, India.

R S Ravi Sankar, Vignan's Institute of Information Technology,

Talath Anjum, Vignan's Institute of Information Technology, Duvvada, India.

P.Sanjay, Vignan's Institute of Information Technology, Duvvada, India.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an <u>open access</u> article under the CC-BY-NC-ND license <a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>

Therefore, the stress in the bearings of a motor connected to a multilevel motor drive can be reduced. Switching frequency: Multilevel converters can operate at both fundamental switching frequency and high switching frequency PWM. It should be noted that lower switching frequency usually means lower switching loss and higher efficiency. Among the best known topologies are the H-bridge cascade inverter, the capacitor clamping inverter (imbricated cells), and the diode clamping inverter.

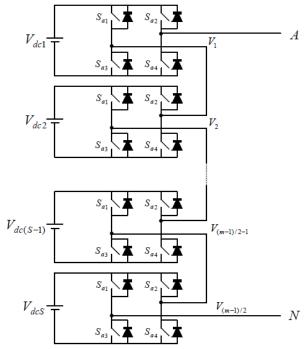

## II. CASCADED H-BRIDGE WITH SEPARATE DC SOURCES MULTILEVEL INVERTERS

A relatively new converter structure, cascaded-inverters with separate dc sources (SDC's) is introduced here. This new converter can avoid extra clamping diodes or voltage balancing capacitors. Each SDC is associated with a single-phase full-bridge inverter. The phase output voltage is synthesized by the sum of four inverter outputs, i.e.,  $V_1 + V_2 + V_3 + V_4$ . The "level" in a cascaded-inverters based converter is defined by m = 2s + 1, where m is the

output phase voltage level, and 's' is the number of dc sources. For example, a 9-level cascaded inverters based converter will have four SDC's and four fullbridges.

The basic cascaded H-bridge inverter is as shown in the Figure 1.

Fig. 1 Circuit Diagram of cascaded H-bridge Inverter

ww.ijitee.org

Published By:

Blue Eyes Intelligence Engineering

and Sciences Publication (BEIESP)

© Copyright: All rights reserved.

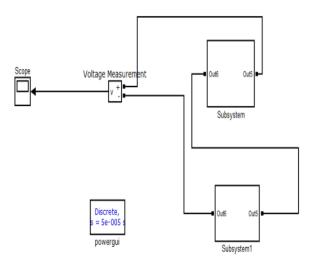

Fig. 2 Simulink of H-bridge Inverter

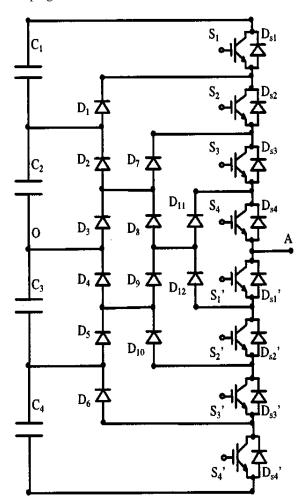

## III. NEW DIODE CLAMPED MULTI LEVEL INVERTER

The new diode clamping inverter is shown in Fig. 2. For the five-level case, a total of eight switches and twelve diodes of equal voltage rating are used, which are the same with the conventional diode clamping inverter with diodes in series. This pyramid architecture is extensible to any level unless otherwise practically limited. A M-level inverter leg requires (M-1) storage capacitors, 2(M-1) switches and (M-1) clamping diodes

Fig. 3 Circuit Diagram of Five Level New Diode Clamped Inverter

Retrieval Number: J15380331014/14©BEIESP Journal Website: <u>www.ijitee.org</u>

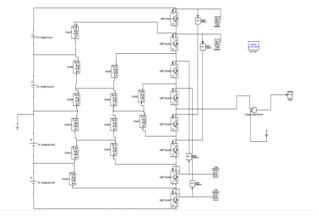

Fig. 4 Simulink of New Diode Five Level Inverter

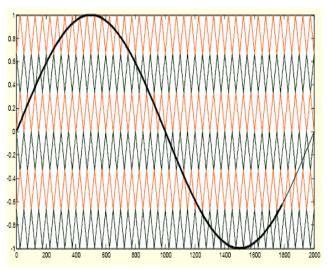

## IV. SINUSOIDAL PULSE WIDTH MODULATION TECHNIQUE

For an m-level inverter, m-1 carriers with the same frequency fc and same peak-to-peak amplitude  $A_c$  are disposed such that the bands they occupy are continuous. The reference, or modulation, waveform has peak-to-peak amplitude  $A_m$  and frequency  $f_m$ , and it is centered in the middle of the carrier set. The reference is continuously compared with each of the carrier signals. If the reference is greater than a carrier signal, then the active device corresponding to that carrier is switched on and if the reference is less than a carrier signal, then the active device corresponding to that carrier is switched off. In multilevel inverters, the amplitude modulation index,  $m_a$  and the

frequency ratio  $m_f$  are defined as

$$m_a = \frac{A_m}{(m-1)A_c}$$

Equation – 1

$m_f = \frac{f_c}{f_m}$  Equation – 2

Fig. 5 Sinusoidal Pulse Width Modulation Technique

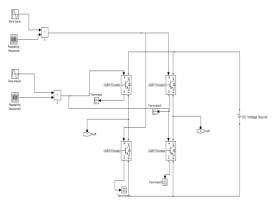

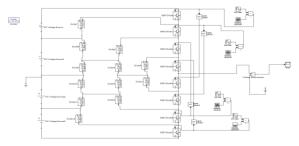

## V. SIMULINK MODELS OF MULTILEVEL INVERTERS WITH PWM TECHNIQUE

Fig. 6 Simulink subsystem of PWM based cascaded H-bridge Inverter

Fig. 7 Simulink of PWM based Five Level New Diode Clamped Inverter

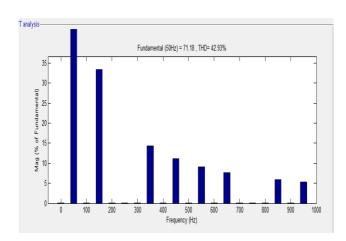

## V. SIMULATION RESULTS FOR DIODE CLAMPED INVERTER

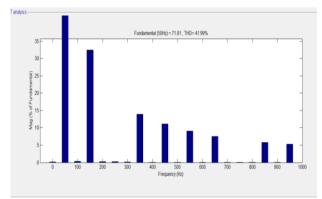

Fig. 8 THD of five level h bridge inverter

Fig. 9 THD of Five Level New Diode Clamped Inverter

Retrieval Number: J15380331014/14©BEIESP Journal Website: <u>www.ijitee.org</u>

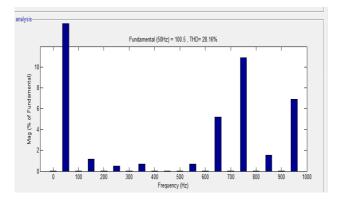

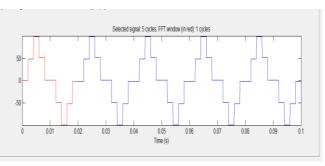

Fig. 10 THD of 5-level H-bridge inverter with PWM Technique

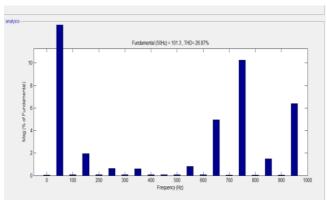

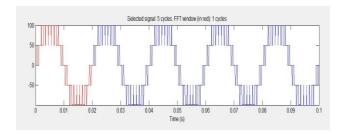

Fig. 11 THD of Five Level New Diode Clamped Inverter with PWM Technique

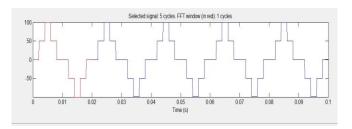

## VI. WAVEFORMS OF NEW DIODE CLAMPED AND CASCADED H-BRIDGE INVERTERS (FIVE LEVEL)

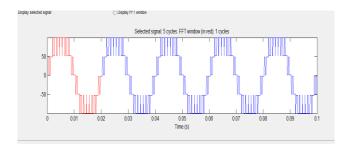

Fig. 12 Simulation Result for Line voltages of 5-level H-bridge Inverter

Fig. 13 Simulation Result for Line Voltages of Five Level New Diode Clamped Inverter

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.

Fig. 14 Simulation Result for Line Voltages generated using PWM Technique of Five Level H-bridge Inverter

Fig. 18 Simulation Result for Line Voltages generated using PWM technique of Five Level New Diode Clamped Inverter

### VII. PERCENTAGE TOTAL HARMONIC DISTORTION ANALYSIS OF H-BRIDGE MULTILEVEL INVERTER WITH DIFFERENT LEVELS USING PWM

| Cascaded H-<br>bridge clamped<br>inverter (Levels) | %THD Without using PWM technique | %THD Using PWM technique |

|----------------------------------------------------|----------------------------------|--------------------------|

| 3 level                                            | 79.89                            | 35.06                    |

| 5 level                                            | 42.93                            | 28.16                    |

| 7 level                                            | 31.35                            | 18.56                    |

| 9 level                                            | 25.79                            | 14.44                    |

#### VIII. PERCENTAGE TOTAL HARMONIC DISTORTION ANALYSIS OF NEW DIODE CLAMPED MULTILEVEL INVERTER WITH DIFFERENT LEVELS USING PWM

| Diode clamped inverter (Levels) | %THD Without<br>using PWM<br>technique | %THD Using PWM technique |

|---------------------------------|----------------------------------------|--------------------------|

| 3 level                         | 79.43                                  | 33.98                    |

| 5 level                         | 41.99                                  | 26.87                    |

| 7 level                         | 30.25                                  | 16.93                    |

| 9 level                         | 24.62                                  | 12.45                    |

#### IX. CONCLUSION

In this paper Pulse width modulation technique is applied on cascaded H-bridge and new diode clamped multilevel inverters and percentage of total harmonic distortions of several levels of inverter are simulated and compared. The simulated results are presented in this paper and it is concluded that PWM technique has given good fundamental spectrum (101.7%) and Total Harmonic Distortion (12.45%). As the number of levels increases the harmonic distortion also decreases. Comparing with the cascaded H-

Retrieval Number: J15380331014/14©BEIESP

Journal Website: www.ijitee.org

bridge multilevel inverter new diode clamped inverter has less Total Harmonic Distortion.

#### REFERENCES

- Jih-Sheng Lai, Fang Zheng Peng, "Multilevel converters- A New Breed Of Power Converters," IEEE Transactions on Industry Applications, VOL. 32, NO. 3, MAY, JUNE 1996.

- Soern Baekhoej Kjaer member of IEEE, John k.Pedersen senior member of IEEE, And Frede Blaabjerg fellow of IEEE "A Review Of Single-Phase Grid-Connected Inverters For Photovoltaic Modules," IEEE Transactions on Industry Applications, VOL.41, NO. 5, PP1292-1306. SEP./OCT. 2005.

- Xiaoming Yuan, Ivo Barbi, "Fundamentals of a New Diode Clamping Multilevel Inverter," IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 15, NO. 4, JULY 2000

- J.S.Lai and F.Z.Peng, "Multilevel converters—A new breed of power converters," IEEE Trans. Ind. Applicat., vol. 32, May/June 1996.

- A.Rufer, "An aid in the teaching of multilevel inverters for high power applications," in Proc. Rec. IEEE PESC'95, 1995,pp. 347– 352.

- C.Newton and M.Sumner, "Multilevel converters: A real solution to medium high voltage drives?," Inst. Electron. Eng.—Power Eng. J., pp.21–26, Feb. 1998.

- F.Z.PENG and J.S.Lai, "A Static VAR Generator Using A Staircase Waveform Multilevel Voltage - Source Converter," IN PROC. PCIM/POWER QUALITY, 1994, PP. 58-66. "Power Converter Options For Power System Compatible Mass Transit Systems," 1994, PP. 285-294.

[1] **N MOHAN TEJA** was born on 14th August, 1993 at Visakhapatnam. He is Pursuing B.Tech in Vignan's institute of information technology, Visakhapatnam, Andhra Pradesh, India

R S RAVI SANKAR was born on 25th, August, 1976 at Visakhapatnam. He received his M.Tech in Electrical Power Engineering from JNTU Hyderabad, Hyderabad and A.M.I.E in Electrical & Electronics Engineering from Institute of Engineers, India. He is presently working as an Associate Professor in Vignan's Institute of Information technology, Visakhapatnam, Andhra Pradesh, India. His research areas include Multi-Level Inverters, Electrical Drives,

and Power Quality Problems in Distribution systems, Power Electronics.

[3] TALATH ANJUM was born on 14th april,1992 at visakhapatnam. She is Pursuing Btech in Vignan's institute of information technology, Visakhapatnam, AP, India.

[4] **P SANJAY** was born on 6th september,1992 at visakhapatnam. He is Pursuing Btech in Vignan's institute of information technology, Visakhapatnam, AP, India

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.