# Implementation of Digital Cross Connect For Simplex Mode of Communication

Chitra Sree. P, Ravi Shankar.J

Abstract—DCS available in the market is expensive and bulky and not scalable and reprogrammable. We have simulated various DCS modes, mainly concentrates on developing indigenous SOC architecture that is reprogrammable, scalable and upgradable. The various switching modes of proposed DCS are round robin, priority and request and acknowledge, The design is simulated using Verilog Hardware Description Language (HDL) in Xilinx ISE9.1i version software and can be implemented on Xilinx Spartan2 family based FPGA board.

Index Terms—Telecommunication, Switching, DCS, simplex mode, round robin, priority, request and acknowledge

#### I. INTRODUCTION

A digital cross connect [DCS] is presently used as standard in data communication and telecom. The Digital cross connect devices are the most compact and high-density ones of their kind, supporting a range of services such as high data speed, network connectivity and streaming of data bits. The DCS is accepted as a key standard by the following technological bodies: the International Telecommunication -Telecommunication ITU-T. It finds application in Landline exchanges Broadband Exchanges, Internet Hubs, Mobile Switching for both Inter & Intra circle, Voice, Data & Video switching capabilities and Wireless switching or Wi-Fi. Optical/Synchronous Digital hierarchy(SDH) networking in mesh accordance with ITU-T recommendations G.709, for SDH in accordance with ITU-T recommendations G.821, G.826, G.828, G.829 and also finds application for Ethernet in accordance with ITU-T recommendations G.7041.

In any multiuser environment, there is a need of flexible and reliable switching architecture. Historically, DCS is mostly widely accepted standard for switching applications in communication technology-

- Radio Frequency (RF) Broadband

- Global Switching Mobile (GSM)

- Code Division Multiple Access (CDMA)

- Public Switched Telephone Network (PSTN).

# Manuscript published on 30 January 2014.

\*Correspondence Author(s)

**Chitra Sree.P**, Department of Electronics And Communication Engineering, SJB Institute of technology, Bangalore, India. **Ravi Shankar.J**, Venus technologies, Bangalore, India.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license <a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>

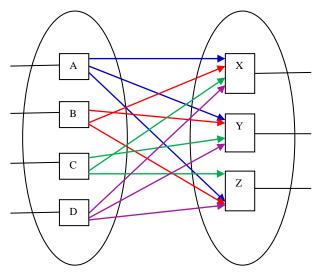

Fig 1.Digital cross connect

#### II. CHALLENGES IN DCS

Switching is an essential component of telephone, telegraph, data-processing, and other technologies.

The main Challenges in DCS are

- Size

- Cost

- Scalability

- High speed switching

- Reprogrammable

- Maintenance

- Cross talk

There is no such System on Chip [SOC] design or architecture displayed in public domain for DCS. To develop an indigenous DCS which is reconfigurable and customizable.

# III. PROPOSED DCS

## A. Background

A **Simplex mode** of communication is a connection in which the data flows in only one direction, from the transmitter to the receiver. Here whether the receiver is ready or not for data reception is checked. If it is not ready, it has to be woken up and the data bits are transmitted.

## B. Switching modes

The proposed DCS will demonstrate the following switching modes:

- Round and robin mode,

- Interrupt mode

- Priority mode

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved. Here we consider there are four transmitters named as A, B, C and D and four receivers named as X, Y and Z.

**Round robin mode-** For each data transmission, time slices are assigned in equal portions and in circular order to each transmitter i.e. from A to receiver X for first twenty seconds,

Fig 2.Digital Cross connect 4 X 3

to receiver Y in next twenty seconds and to receiver Z and handling all data transmission in without priority. Here the line of communication is allotted to the requesting device in round robin manner. Here the possible combinations of data transmission from each transmitter to each receiver in a time slice of twenty seconds.

Table 1. Possible combinations of data transmission from transmitter to receiver in round robin mode

| transmitter | Receiver | time     |  |

|-------------|----------|----------|--|

|             |          |          |  |

| A           | X        | 0-19s    |  |

| A           | Y        | 20-39s   |  |

| A           | Z        | 40-59s   |  |

| В           | X        | 60-79s   |  |

| В           | Y        | 80-99s   |  |

| В           | Z        | 100-119s |  |

| С           | X        | 120-139s |  |

| С           | Y        | 140-159s |  |

| С           | Z        | 160-179s |  |

| D           | X        | 180-199s |  |

| D           | Y        | 200-219s |  |

| D           | Z        | 220-239s |  |

**Priority mode** -Assigning priorities enables one to exert significant control over the flow of data bits, in providing quicker service to the most important data requests, and provide slower service to the less important data requests. Consider there are two service provider, in service provider1 (S1) there are A, B, C, D devices and in service provider2 (S2) there are X, Y, Z devices. Assume B has highest priority, only after the transmitter has transmitted data to all receivers

one by one in a round robin manner. Then according to priorities the remaining transmitters transmit data to receivers. Assuming transmitter B has priority then followed by, D, C and A. The following are the possible combinations.

Table 2. Possible combinations of data transmission from transmitter to receiver in priority.

| Transmitter | Receiver | time     |

|-------------|----------|----------|

| В           | X        | 0-19s    |

| В           | Y        | 20-39s   |

| В           | Z        | 40-59s   |

| D           | X        | 60-79s   |

| D           | Y        | 80-99s   |

| D           | Z        | 100-119s |

| C           | X        | 120-139s |

| C           | Y        | 140-159s |

| C           | Z        | 160-179s |

| A           | X        | 180-199s |

| A           | Y        | 200-219s |

| A           | Z        | 220-239s |

**Interrupt mode-**In this mode, if the transmitter needs to communicate with the receiver, then it follows the protocol described below: Here the transmitter sends request signal to receiver, if the receiver has data bits the acknowledge signal is high otherwise low. Then the receiver sends this acknowledge to transmitter only it ready for reception of the data.

The following table is the possible combinations of transmission of data from each transmitter to each receiver while one of them is made to wait for its data transmission. If transmitter D is waiting, the following table is the possible combinations of data transmissions from each transmitter to each receiver.

Table 3. Combinations of data transmissions from each Tx to each Rx if tx D is in wait state

| Tx Rx   | Tx Rx      | Tx Rx     | Tx Rx      | Tx Rx                              | Tx Rx                      |

|---------|------------|-----------|------------|------------------------------------|----------------------------|

| A→<br>X | A→Y<br>B→X | A→Z<br>B→ | A→X<br>B→Z | A <b>&gt;</b> Y<br>B <b>&gt;</b> Z | A <b>→</b> Z<br>B <b>→</b> |

| D \17   | C \        | Y<br>C→   |            | C \                                | 37                         |

| , , ,   | 2          | X         | •          |                                    | Y                          |

Tx -transmitter, Rx-receiver

If transmitter C is waiting, the following table is the possible combinations of data transmissions from each transmitter to each receiver.

Table 4. Combinations of data transmissions from each Tx to each Rx if tx C is in wait state.

| Tx Rx |

|-------|-------|-------|-------|-------|-------|

| A→X   | A→Y   | A→Z   | A→X   | A→Y   | A→Z   |

| B→Y   | B→X   | B→Y   | B→Z   | B→Z   | B→X   |

| D→Z   | D→Z   | D→X   | D→Y   | D→X   | D→Y   |

If transmitter A is waiting, the following table is the possible combinations of data transmissions from each transmitter to each receiver.

Table 5. Combinations of data transmissions from each Tx to each Rx if tx A is in wait state.

|                 |     | Tx Rx                 |                 |              |              |

|-----------------|-----|-----------------------|-----------------|--------------|--------------|

| B <b>→</b> X    | В→Ү | Β→Ζ                   | В→              | B <b>→</b> Y | B <b>→</b> Z |

| C <b>&gt;</b> Y | C→X | C→                    | X               | C→           | C→           |

| D→Z             | D→Z | Y                     | C <b>&gt;</b> Z | Z            | X            |

|                 |     | B→Z<br>C→<br>Y<br>D→X | D <b>→</b> Y    | D→X          | D <b>→</b> Y |

Table 6. Combinations of data transmissions from each Tx to each Rx if tx B is in wait state.

|     |     | Tx Rx |     |     |     |

|-----|-----|-------|-----|-----|-----|

| A→X | A→Y | A→Z   | A→X | A→Y | A→Z |

| C→Y | C→X | C→Y   | C→Z | C→Z | C→X |

| D→Z | D→Z | D→X   | D→Y | D→X | D→Y |

#### IV.SIMULATION RESULTS

The simulation results of various switching modes have been presented.

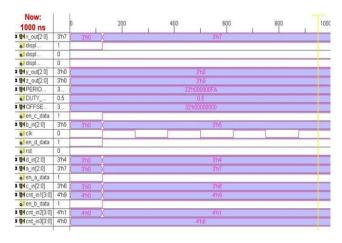

#### A. Round robin mode

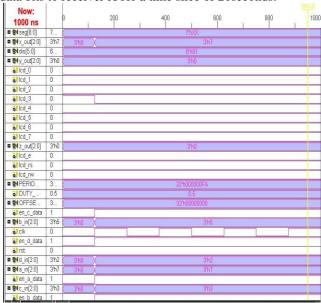

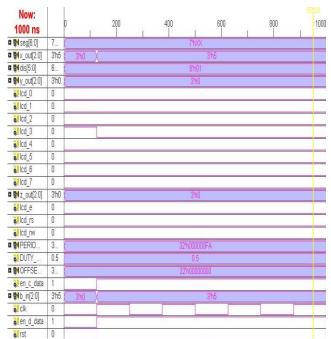

In figure 3 and 4, the transmitter A transmits data bits (also includes address bits)to receiver X for a time slice of 20seconds and to receiver Y for next 20seconds respectively. In this each transmitter transmits data for each receiver for time slice of 20 seconds

Fig 3. Data transmission from transmitter A to receiver X.

Fig 4. Data transmission from transmitter A to receiver Y.

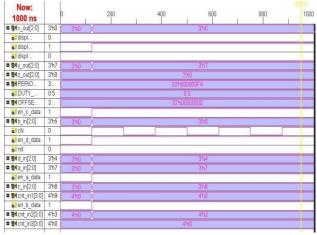

# B .Interrupt mode

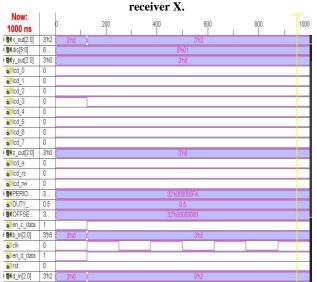

Here each transmitter requests receiver whether receiver is ready for data reception if it is free then it acknowledges the

Retrieval Number: H1435013814/14©BEIESP Journal Website: <u>www.ijitee.org</u> transmitter to send the data. Here below there are four transmitters A, B, C, D and three receivers X, Y, Z. One of the transmitters has to wait while other three transmitters are transmitting data.

In figure 5 while transmitter D is in wait state (ready for data transmission), the other transmitter A transmits data to receiver X, transmitter B transmits data to receiver Y and transmitter C transmits data to receiver Z.

Fig 5. Data transmission from tx A to rx X,tx B to rx Y and tx C to rx Z.

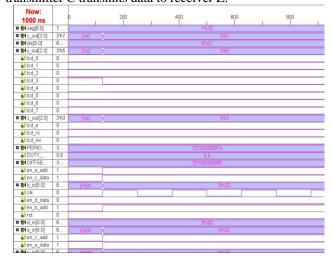

### C. Priority mode

In this each transmitter transmits data for each receiver for time slice of 20 seconds in a priority assigned to them.

In figure 6 if transmitter A has assigned high priority, then it first transmits data bits to receiver X for a time slice of 20seconds. In figure 7, if transmitter B has assigned high priority, then it first transmits data bits to receiver X for a time slice of 20seconds. In figure 8, if transmitter C has assigned high priority, then it first transmits data bits to receiver X for a time slice of 20seconds. In figure 9, if transmitter D has assigned high priority, then it first transmits data bits to receiver X for a time slice of 20seconds.

Fig 6. Data transmission from transmitter A (high priority)to receiver X.

Fig 7. Data transmission from transmitter B (high priority)to

Fig 8. Data transmission from transmitter C (high priority)to receiver X.

Fig 9. Data transmission from transmitter D (high priority)to receiver X.

Retrieval Number: H1435013814/14©BEIESP Journal Website: <u>www.ijitee.org</u>

#### **V.CONCLUSION**

In this project wired SOC-DCS was simulated using Xilinx 9.1 for various switching modes like round robin, interrupt and. In each of these modes data transmission is done between transmitter and receiver to reduce congestion of data among the users and traffic is managed considerably. The design can be implemented on Xilinx spartan2 family based FPGA board, using Verilog HDL.

#### VI. FUTURE ENHANCEMENT

The proposed digital cross connect can also be developed for other switching mode, which later can be improvised to 8x8, 16x16, 64x64, 128x128 and 256x256 and make it fully scalable and wireless too, leading to a SOC – DCS.

#### REFERENCES

- Vinita Singhal and Robert Le, "High-Speed Buffered Crossbar Switch Design using Virtex -EM Devices" XAPP240 (v1.0) March 14, 2000, pg 1-7.

- "Building Crosspoint Switches with CoolRunner-II CPLDs" XAPP380 (v1.0) June 5, 2002, pg 1-5.

- J. E. Flood, "Telecommunication Switcing, Traffic and Networks," Pearson 2011.

- Thiagarajan Vishwanathan, "Telecommunication Switching Systems and Networks," PHI 2012.

- GuoweiShi ,"Design and application of SDH digital cross-connect system", Communications, Circuits and Systems and West Sino Expositions, IEEE 2002 International Conference on communications. vol.2,pg 1293 - 1296

- Yuan Yuying, "Design and Realization of SDH Digital Cross-Connect Matrix", IEEE Conference Publications, WiCom ,2007,pg 692 - 695

- Yuan Yuying "The design of the SDH digital cross-connect matrix based on ASIC", World Automation Congress (WAC), IEEE Conference Publication, 2012.pg 1-4

# **AUTHOR PROFILE**

Chitra Sree.P, in the year 2010, Passed B.E. in Electronics & Communication Engineering from R.N.S.Institute of technology, Bangalore, (Karnataka). In the year 2013, pursed M.TECH in VLSI design and embedded systems from SJB Institute of Technology, Bangalore (Karnataka). My research area is telecommunication.

Ravi Shankar.J, in the year 1994, passed B.E in Electronics & Communication Engineering from NIE, Mysore (Karnataka). In the year 1998, passed M.Tech in industrial electronics from SJCE, Mysore (Karnataka). He is presently working as an senior technical consultant for government of Karnataka.