# Design of Low Power Optimized Filter Architecture using VLSI Technique

#### Pritesh R. Gumble, S.A. Ladhake

Abstract—In the prevalence of DSP applications the weighted operations are the multiplication and accumulation. Multiplier-Accumulator (MAC) unit that consumes low power is always a means to accomplish a high concert digital signal processing system. Finite impulse response (FIR) filters are widely used in various DSP applications where signal were present with noise (e.g. data converters). Uptill many proficient techniques have been introduced for the design of low snag bit-parallel multiple constant multiplications (MCM) process which reduces the intricacy of many digital signal processing systems. On the other hand, digit-serial adder architectures present remarkable n-bit designs which process dynamic size data, since digit-serial operators hold less area and power. The purpose of this work is to design and implementation of low power optimized digital Finite impulse response (FIR) filter architecture using VLSI technique. We design and analyze 1] Direct form 2] Transpose form 3] Transpose using MCM 4] Transpose using digit serial adder 5] Transpose using MCM and digit serial adder. Experimental results shows the efficiency of the various architectures and we found best performance results of Transpose using MCM and digit serial adder design in terms of area and power. To execute this work the design is verified using Active-HDL with MATLAB and synthesis [45nm] using Synopsys.

Index Terms— digit- serial adder architecture, FIR, Low Power, MAC, MCM.

#### I. INTRODUCTION

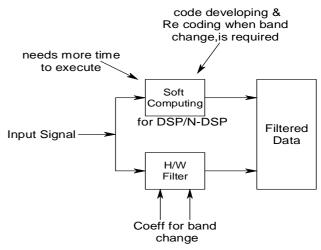

In high freq data converters signal were present with noise therefore we needed to process the combination of this data to filter out desired data. There are two options to filter out this data i.e. soft computing and hardware implementation of filter.

Soft computing demands development of code for filter, based on DSP processor or non DSP architecture processor. But still DSP processor needs development of filter code even though it's having MAC (multiply accumulation) structure inside, there is no issue of non DSP processor it needs huge efforts to develop filter code without MAC structure. It is an overhead to software developer to develop a code. Again it is based on sequential programming and sequential execution, which needs much time to produce more output [9].

#### Manuscript Received on December 2014.

**Pritesh R. Gumble,** Department of Electronics and Telecommunication Engineering Sipna College of Engineering and Technology, AmravatiMaharashtra State, India.

**Dr. S.A.Ladhake,** Principal, Sipna College of Engineering and Technology, Amravati, Maharashtra State, India.

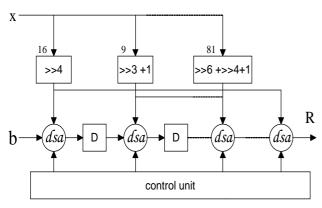

Fig-1 Proposed Work

It is an overhead to processor so, it demands h/w for such time consuming process. Hence soft computing is not suitable for run time variations.

Intended for the design of digital filters, the system function H(z) or the impulse response h(n) must be specified. Then the digital filter structure can be implemented or synthesized in hardware/software form by its difference equation obtained directly from H(z) or h(n).Each difference equation or computational algorithm can be implemented by using a digital computer or special purpose digital hardware or special programmable integrated circuit[15].

In order to implement the specified difference equation of the system, the required basic operations are addition, delay and multiplication by a constant.

FIR filter is a type of signal processing filter whose impulse response is of finite duration, because it settles to zero in finite time. FIR is also known as non recursive digital filter as they do not have the feedback.

In general FIR filter are normally designed to have a linear phase response and there is also great flexibility in shaping their magnitude response. In addition, FIR filters are inherently more stable and the effect of quantization errors is less severe than IIR filters.

Infatuated systems requiring different sample rates will need to be implemented in bit-serial, bit-parallel and digit-serial. Bit-serial technique process one input bit at a time and is functional for low-speed applications. These systems require fewer interconnections, less hardware. Bit-parallel systems process all input bits of a word in one clock cycle, and require the leading area, interconnection. These systems are best for high-speed applications. Whereas digit-serial systems process more than one input bit in one cycle. These systems are perfect for mild speed applications, for which bit-serial method is too slow, and bit-parallel method is faster than essential. The number of bits processed per cycle is referred to as the digit-size. For concord digit-size, the design reduces to a bit-serial system, and for digit-size equal to the word-length, the design reduces to a bit-parallel system. In

this paper, an efficient design methodology for low power optimized filter is presented.

## II. FILTER COEFFICIENT EXTRACTION AND RESULT OF FILTER

FIR filter are often preferred in many applications, since they provide an exact linear phase over the whole frequency range and they are always bounded i/p bounded o/p (BIBO) stable independent of the filter coefficients. The convolution sum relationship gives the system response as

$$R = \sum_{k=0}^{M-1} x(n-k)^*h(k) -----eqn(1)$$

Where R and x(n) are the output and input sequences, respectively. This equation gives the input-output relation of the FIR filter in the time domain. The realization for this equation is shown in following filter architectures which is the set of basic elements like latch, multiplier & adder [13].

By using Matlab 'fdatool' we have design the filter of 17 order, FIR type— equiripple, Density—20, Low pass,Fs-48Khz Fpass-9.6Khz and Fstop-10Khz. We get the required coefficient in floating point as the size of floating point representation is in 32/64/128 bit which will lead more area so we transform the floating point into integer with no change in filter response, after plotting the filter response of both float and integer of coefficient we conclude that, we can go with integer with no effect in filter response [3]. We get the 'h' as follows and Matlab convolution result as 'R'

h= [16 9 10 12 12 9 1 16 81 81 16 1 9 12 12 10 9 16]; ------hvalue(1)

x=1:20; ------xvalue(1)

R=conv(x, h) ------mat\_cmd(1)

R = 16 41 76 123 182 250 319 404 570 -----mat\_result(1)

### III. FILTER ARCHITECTURES AND SIMULATION RESULTS

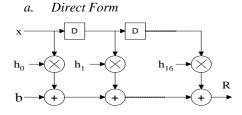

Fig- 2 design for direct form

| Total Dynamic Power(mW) | 5.8277 |

|-------------------------|--------|

| Total Cell Area (µm^2)  | 28455  |

Direct form implementation using basic elements like latch, multiplier & adder. The input size is of 8 bit so latches are of 8 bit size, multiplier is of 8x8 so, results is of 16 bit, adder is of [16 + no of tap i.e.17] ~ 32bit, which is taken with consideration of maximum values of coefficient and input X. Multiplier & adder be implemented using std ieee library of VHDL which is default in its definition [15].

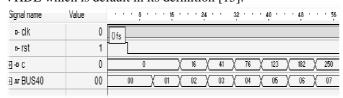

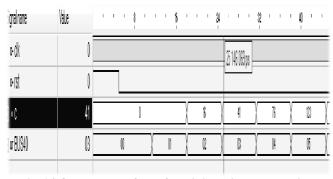

Fig- 3 Output waveform for direct form

### From w/f we verified the result [c] of direct form with matlab result mat\_result(1).

#### b. Transpose Form

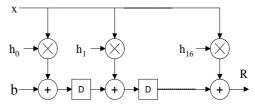

Fig- 4 Design for Transpose form

| Total | Dynamic pow    | ver(mW) | 12.7854 |

|-------|----------------|---------|---------|

| Tot   | al Cell Area(µ | ım^2)   | 34626   |

If the two digital filter structures have the same transfer function, then they are called equivalent structures. A simple way to generate an equivalent structure from a given realization structure is via the transpose operation. The transposed form is obtained by (i) reversing the paths, (ii) replacing pick-off nodes by latches and (iii) interchanging the input and output nodes. For a single input-output system, the transposed structure has the same transfer function as the original realization structure. As shown in figure by replacing pick-off node with latches the total cell area of transpose form get increased as compare to direct form. As well as total dynamic power also get increased [13].

Transpose form implementation is done using basic elements like latch, multiplier & adder. The input size is of 8 bit , here the main area intense element is latches with respective to DFF in-place of 8 bit size here 32 bit size is needed so area get increases, all other modules are same as that of direct form.

Fig-5 Output waveform for Transpose form

From waveform we verified the result [c] of Transpose

form with matlab result mat\_result(1).

#### c. MCM Form

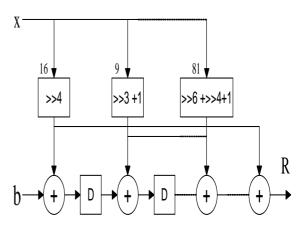

Fig-6 Design for Transpose MCM

| Total Dynamic power(mW) | 2.3450   |  |

|-------------------------|----------|--|

| Total Cell Area(µm^2)   | 20999.76 |  |

Here we replace the conventional multiplier with shift add method of multiplication. Again as we were design filter with equiripple approach, so we can reuse multiplication result for the similar coefficient values, which considerably reduce the area and power with respective to direct and transpose form. Fig.7 shows the example of one of the coefficient (81X) from series [4].

Fig-7 Shift- adds implementation of 81X

Fig-8 Output waveform for Transpose MCM

From waveform we verified the result [R] of Transpose MCM form with matlab result mat\_result(1).As shown in Fig. 8 here input x(xout) is extracted from control unit.

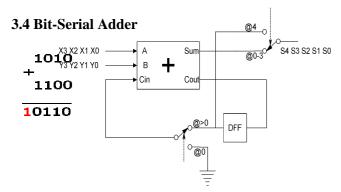

Fig-9 A bit-serial adder for word length of 4

Fig. 9 shows the bit-serial architecture for word length of 4 (W=4). This adder adds two four bit numbers X3X2X1X0 and Y3Y2Y1Y0 to get 4 bit sum S3S2S1S0 where bit 0 is the least significant bit and bit 3 is the most significant bit. Initially cin=0, we have to kept cin=0 using switch, after it we force full-adder with data X0Y0 we get the value of sum S0. For next iteration we connect cout to cin using switch and we force the full-adder X1Y1 we get the value of S1 and so on.

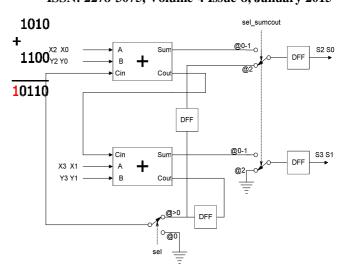

#### 3.5 Digit-serial Adder

In parallel system speed, power is high and in addition area constraint is also high, to shrink the power and area we prefer bit-serial structural design but it might be slow in speed. Although we gain the power and area constraint but it lost the speed. So there is no need of such an architecture while balance the things, that is speed, area and power constraint. This is stimulus to design a digit-serial architecture.

Fig-10 digit serial adder for digit-size two

dsa = digit serial adder (2 bit digit size)

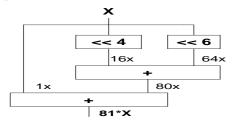

Fig-11 Architecture for digit serial adder (Transpose)

| Total Dynamic power(mW) | 7.3128    |

|-------------------------|-----------|

| Total Cell Area(µm^2)   | 13424.326 |

There are two approaches. First, by using bit serial adder we can process two input samples concurrently, and course each participation in a bit-serial approach; this corresponds to a word analogous bit-serial system with wedge size of two. Alliteratively, we can course the inputs in a word serialized manner, but course two bits of a word in analogous; this corresponds to a word-serial digit-serial implementation with digit-size two shown in Fig. 10. The digit-serial structural design needed less latches in the add computation segment, and in the data design alteration portions, and relatively requires simpler control circuit shown in Fig. 11. The reduction in the number of latches prefers the digit serial architecture for VLSI realization [1].

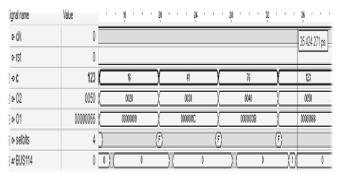

Fig-12 Output waveform for digit serial adder (Transpose)

#### Design of Low Power Optimized Filter Architecture using VLSI Technique

dsa = digit serial adder (2 bit digit size)

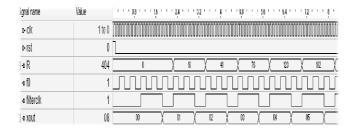

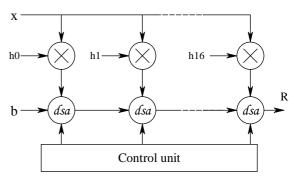

Fig-13 digit serial adders using transpose and MCM

| Total Dynamic power(µW) | 149.2223 |

|-------------------------|----------|

| Total Cell Area(µm^2)   | 988.81   |

Fig. 13 shows the design for digit serial adders using transpose and MCM along with the control unit which can reduce significant amount of power and area.

Fig-14 Output waveform for digit serial adder using transpose and MCM

Table: 1 Result Analysis for different filters

| Туре           | Combin<br>ational<br>Area<br>(µm^2) | Non<br>combin<br>ational<br>Area<br>(µm^2) | Total<br>cell<br>Area<br>(µm^2) | Cell<br>Intern<br>al<br>Power | Net<br>Switching<br>Power | Total<br>Dynamic<br>Power |

|----------------|-------------------------------------|--------------------------------------------|---------------------------------|-------------------------------|---------------------------|---------------------------|

| Direct<br>Form | 27050                               | 1404                                       | 28454                           | 3.42<br>mW                    | 2.4014<br>mW              | 5.8277<br>mW              |

| Transp<br>ose  | 29010                               | 5616                                       | 34626                           | 7.77<br>mW                    | 5.0117<br>mW              | 12.7854<br>mW             |

| MCM            | 15383                               | 5616                                       | 20999                           | 1.47<br>mW                    | 871.52<br>μW              | 2.3450<br>mW              |

| dsa<br>Trans.  | 13273                               | 151                                        | 13424                           | 4.21<br>mW                    | 3.10<br>mW                | 7.3128<br>mW              |

| dsa<br>MCM     | 837                                 | 151                                        | 988                             | 113.<br>24<br>μW              | 35.98<br>μW               | 149.222<br>3 μW           |

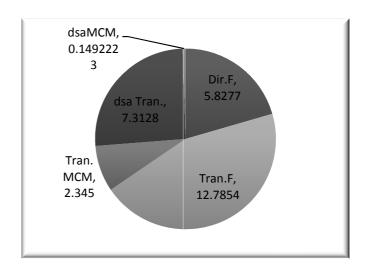

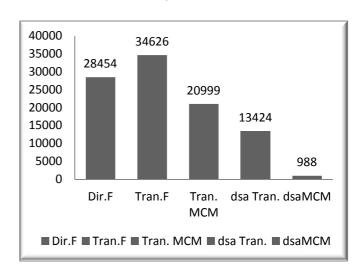

Table 1 shows the detailed analysis through different types of filter that we have designed to get optimized one in terms of cell area and dynamic power.

Chart-1 and chart-2 gives the graphical representation of total dynamic power and total cell area respectively.

Chart-1 Total Dynamic Power(mW)

Chart-2 Total cell Area

#### IV. CONCLUSION

This paper introduced the design architectures for the transpose using MCM and digit-serial adder operation for the realization of FIR filters. The experimental results indicate that the complexity of direct form, transpose form designs can be minimized by using the digit-serial MCM operation proposed here. It was revealed that the consciousness of digit-serial MCM FIR filter under the shift-add architecture yields crucial area and power reduction when compared to the filter designs implemented using other four i.e. direct, transpose, transpose using MCM, and transpose using digit serial adder form.

#### ACKNOWLEDGMENT

I offer sincere gratitude and thanks to Dr. S. A. Ladhake, Principal of institute and guide for the shared expertise in related fields as well as for provided necessary experiences during period of working on this paper.

#### REFERENCES

- Keshab K. Parhi, and Ching-Yi Wang, "Digit-Serial DSP Architectures" International Conference on Application Specific Array Processors, pp. 341-351.

- [2] Yun-Nan Chang, Janardhan H. Satyanarayana, and Keshab K. Parhi, "Systematic Design of High-Speed and Low-Power Digit-Serial Multipliers" IEEE Transactions On Circuits And Systems—II: Analog

- And Digital Signal Processing, Vol. 45, No. 12, December 1998, pp. 1585-1596

- [3] Ahmed Shahein, , Qiang Zhang, Niklas Lotze, and Yiannos Manoli, " A Novel Hybrid Monotonic Local Search Algorithm For Fir Filter Coefficients Optimization" IEEE Transactions On Circuits And Systems—I: Regular Papers, Vol. 59, No. 3, March 2012, pp. 616-627.

- [4] Levent Aksoy and Cristiano Lazzari, Eduardo Costa, Paulo Flores and Jose Monteiro, "Optimization of Area in Digit-Serial Multiple Constant Multiplications at Gate-Level", pp. 2737-2740.

- [5] Mustafa Aktan, Arda Yurdakul, and Günhan Dündar, "An Algorithm for the Design of Low-Power Hardware-Efficient FIR Filters", IEEE Transactions On Circuits And Systems—I: Regular Papers, Vol. 55, No. 6, July 2008, pp. 1536-1545.

- [6] Levent Aksoy, Cristiano Lazzari, Eduardo Costa, Paulo Flores, and José Monteiro, "Design Of Digit-Serial FIR Filters: Algorithms, Architectures, And A CAD Tool", IEEE Transactions On Very Large Scale Integration (VISI) Systems, pp. 1-14

- [7] Chi-Jui Chou, Satish Mohanakrishnan, Joseph B.Evans "Fpga Implementation Of Digital Filters" Proc. Icspat '93

- [8] Bahman Rashidi and Majid Pourormazd "Design and implementation of low power Digital FIR Filter based on low power multipliers and adders on Xilinx FPGA," IEEE Publications, 2011.

- [9] Pritesh R. Gumble, Dr. S.A. Ladhake "Architecture For High Performance, Low Power Data Converter And Filter, In Deep Submicron CMOS Technology", International Journal of Computing and Corporate Research, ISSN2249054X-V212M5-032012 Volume 2 Issue 2 March 2012.

- [10] Shanthala S, S. Y. Kulkarni, "VLSI Design and Implementation of Low power MAC unit with Block Enabling Technique," Eurojournals Publishing Inc. 2009

- [11] Nadia Khouja , Khaled Grati, Adel Ghazel "Low Power implementation of Decimation Filters in Multistandard Radio Receiver Using optimized Multiplication—Accumulation Unit ,",IEEE Publications, 2007.

- [12] Q. F. Zhao and Y. Tadokoro, "A simple design of FIR filters wit Power-of-two coefficients," IEEE Trans. Circuits Syst., vol. 35, no. 5.

- [13] S Salivahanan, A Vallavaraj, C Gnanapriya, "A text book of Digital Signal Processing", Tata McGraw-Hill Publication, pp. 453-514

- [14] K.K. Parhi, "VLSI digital signal processing system"

- [15] Volnei A. Pedroni, "Circuit Design with VHDL", PHI publication, pp. 275-303

Pritesh R.Gumble received his B.E. and M.E. Degrees from the Sant Gadge Baba Amravati University Amravati, India in 2008 respectively in Digital Electronic and registered for his Ph.D in S.G.B. Amravati. Currently he is working as Associate Professor in Electronics and Telecommunication Department at Sipna College of Engineering & Technology, Amravati. He is IETE Member, ISTE (New Delhi) Life Member. His topic of interest in Digital Design, VLSI.

**Dr. Siddharth A. Ladhake** received master's degree in 1990 and PhD in 2004 in Electronics Engineering from Sant Gadge Baba Amravati University, Amravati, India. He has 32 years of teaching experience and presently working as Principal at Sipna college of Engineering and Technology, Amravati(India).Previously he was holding a post of Professor from 1999 to 2005 at Prof. Ram Meghe Institute of Engineering and Research, Badnera,(India).His main research

interest include signal processing, image processing, code conversion multivalued logic etc. He is a senior member of IEEE, IETE, IE and ISTE. He has published 97 papers in National and International Journal and conferences.