# Design and Development of Microcontroller **Based Multilevel Inverter**

Ganesh H.Wani, D.K.Shedge

Abstract: Now a day mostly we produce power from non conventional energy sources and power hassle increases day by day. To diminish this power demand we need to emphasize power infusion methods. Multi-level inverter is accommodating to infuse power from distinct renewable sources like solar, wind-power. It generates the alternating output level of voltage from different DC level sources. This inverter uses 'm' H-bridges and several DC sources to obtain (2m+1) level of output voltage. This paper focuses on improvement of quality of desired output voltage waveforms with less number of switching devices.

Index Terms: Cascade H-bridge Multi-level Inverter (CHBMLI), Total harmonic Distortion (THD), Pulse Width Modulation (PWM)

#### I. INTRODUCTION

A Multi-level inverter is an electronic device which converts the DC voltage preferably low level to desired alternating voltage. Mostly, we use 2 level inverter while converting the alternating voltage from DC voltage source. The expected multi-layer output is acquired by blending multiple DC level voltage sources like batteries etc. These are the common sources used. A common multilevel inverter starts with 3 levels. As the levels increases the output waveform with low harmonics distortion is produced. As per the standard provided by IEEE std 519-1992, total harmonic distortion for the specific equipments should be 5% with the filter and 15-20% without the filter. When we increase the number of levels, the complexity of circuit also increases. Again when we are increasing inverter level, it increases number of proportional devices, with increased cost of inverter. When we increase the number of switches, switching losses are also increases. From the last decade, different topologies have been introduced with several advantages and disadvantage one upon other. These topologies are "diode clamped" (neutral clamped), "cascade H-bridge", "flying capacitor" (capacitor clamped), and "Modified cascade H-bridge". Some of these topologies have capacitor unbalancing and need additional power diode, which reduces the performance of multi-level inverter.

### Manuscript published on 30 August 2019.

\*Correspondence Author(s)

Ganesh H. Wani, a Engineering Student at AISSMS Institute of Information Technology, Pune, Maharshtra, India.

Dr.D.K.Shedge, Professor at AISSMS Institute of Information Technology, Pune, Maharshtra, India.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license <a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>

## II. SINGLE CELL CASCADED H-BRIDGE MULTILEVEL INVERTER

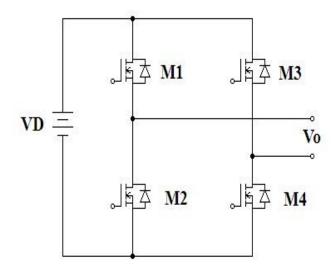

Basic multi-level inverter uses single cell which contains four switches connected to form a bridge as shown in figure 1. The switch M1 and M2 are connected to one arm and switch M3 and M4 are connected to other arm. In this the modulating wave (Sinusoidal wave) is compared with carrier triangular wave and resulting waveforms applies switching for Switch M1 and inverse of this wave given to M2. In similar way second modulating and carrier signal gives switching to M3 and M4

Fig: 1 Single Cell MLI

Fig-1 shows the single phase H-bridge cell. With the help of this cell we can obtain output voltage up to three levels and when cascading with other similar indistinguishable bridge gives five levels. Likewise when we cascade 'm' number of cell, number of levels 'n' in the output voltage turns to,

n = 2m + 1.

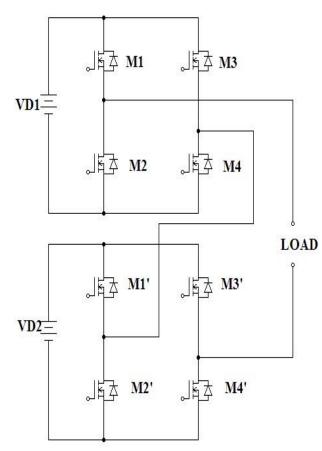

Fig-2 shows five level cascade H-bridge multi-level inverter. This five level inverter uses eight switches. These eight switches are organize in a such way to form two H-bridges, M1 and M2 forms one arm of first bridge with M3 and M4 forms other arm. Whereas switch M1' and M2' forms one arm of second H-bridge with switch M3, and M4'other arm.

# Design and Development of Microcontroller Based Multilevel Inverter

Fig.2: Two Cell MLI

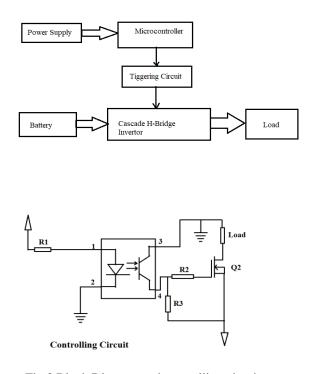

## III. BLOCK DIAGRAM AND CONTROLLING CIRCUIT

Fig.3 Block Diagram and controlling circuit The fig.3 shows functional diagram of cascade H-Bridge multi-level inverter. Each cascaded circuit is powered by separate battery source. The output signal of cascade H-bridge circuit is given to single phase load. Total 12 powers MOSFET are used in each H-bridge circuit and switching of MOSFET is controlled by the microcontroller

through an opto-isolator. A separate power supply is designed to control and trigger the circuit. Opto-isolator isolates power and control circuit. Synchronized switching strategy obtained by microcontroller to generate stepped power frequency output voltage.

#### IV. SEVEN LEVEL CASCADED H-BRIDGE INVERTER

Now a days there are many inverters available in the market but multilevel inverters has many advantages with great capabilities, out of this cascade H-bridge multi-level inverter focuses on improvement of output signal quality and damage of power devices with failure to achieve the desired current and voltage levels. Multilevel inverter designed in such way to overcome disadvantages of conventional inverters including some smart features which can be produce minimal distorted output current and voltage with minimal switching frequency.

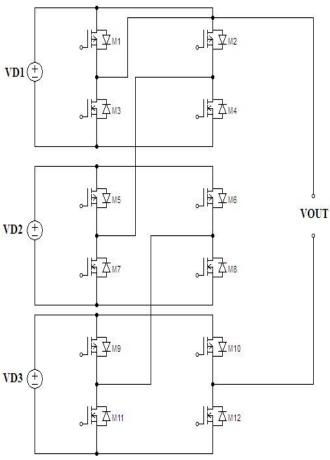

Fig.4 Seven level Cascaded H-Bridge MLI

Fig-4 shows seven levels cascade H-bridge multi-level inverter. It produces seven steps or levels of output in proportional to input source voltage. Input voltage source is suppose VD then expected steps are 3.VD, 2.VD,.VD, 0V,-VD,-2.VD,-3.VD. The output voltage oscillate between +3VD and -3VD. Switching state configuration determines output value of inverter. Switching states in seven levels cascade H-bridge multi-level inverter can be possible in seven different configurations. Each configuration gives output as follows,

w.ijitee.org

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) 1376 © Copyright: All rights reserved.

Mode: 1:

Here, This configuration makes MOSFET M1, MOSFET M2, MOSFET M5, MOSFET M6, MOSFET M9 and MOSFET M10 ON, So the level of output VOUT = 3VD.

Mode: 2:

Here, This configuration makes MOSFET M1, MOSFET M2, MOSFET M5, MOSFET M6, MOSFET M10 and MOSFET M12 ON, So the level of output VOUT = 2VD.

Here, This configuration makes MOSFET M1, MOSFET M2, MOSFET M6, MOSFET M8, MOSFET M10 and MOSFET M12 ON, So the level of output VOUT = VD

Here, this configuration makes MOSFET M2, MOSFET M4, MOSFET M6 MOSFET M8 MOSFET M10 and MOSFET M12 ON, So the level of output VOUT = 0V.

Mode: 5:

Here, This configuration makes MOSFET M2 MOSFET M4, MOSFET M6 MOSFET M8, MOSFET M9 and MOSFET M10 ON, So the level of output VOUT = -VD (-ve)

Mode: 6:

Here, This configuration makes MOSFET M2, MOSFET M4, MOSFET M7 MOSFET M8, MOSFET M11 and MOSFET M12 are ON, So the level of output VOUT = -2VD (-ve)

Mode: 7:

Here, This configuration makes MOSFET 3 MOSFET 4, MOSFET 7, MOSFET 8, MOSFET 11 and MOSFET 12 are ON, So the level of output VOUT = -3VD (-ve)

The summation of output of all bridges connected in series is load voltage. In this multi-level inverter output level is

N = 2X + 1

Where.

X = separately connected DC level Sources,

N = Number of output levels.

This multi-level inverter combines desired voltage from distinct DC level sources

# V. RESULT

A prototype of cascade H-bridge multi-level inverter seven levels is developed and compared with three level inverter and result obtained are summarizes in table given below.

| Sr.N | No Inverte | r Voltage<br>THD |

|------|------------|------------------|

| 1    | 3 Level    | 58 %             |

| 2    | 7 Level    | 17 %             |

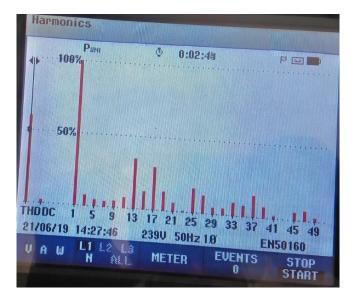

Fig. 4 Three level inverter THD content

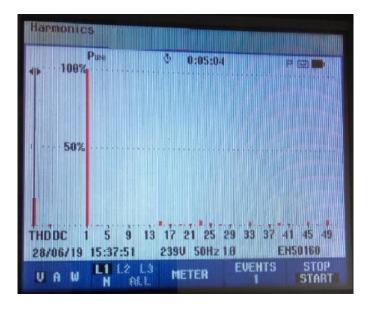

Fig. 5 CHML Seven level THD content

Fig. 6 CHML Seven Level waveforms

# Design and Development of Microcontroller Based Multilevel Inverter

Fig. 4 shows THD content measured by power quality analyzer of three levels inverter. Fig.5 shows THD content of cascade H-bridge multi-level inverter. The total harmonic distortion is a measurement of harmonics present in the output voltage waveform of cascade H-bridge multi-level inverter. Total harmonics distortion (THD) of output waveforms of inverter with respect to pure sine wave measured by power quality analyzer. Fig.6 shows the stepped waveform of cascaded H-bridge multilevel inverter, which becomes more sinusoidal if we increases the number of output voltage level. While comparing with three level inverter, content of THD is lesser in seven level CHML.

#### VI. CONCLUSION

In this way we have designed and developed Multi-level Inverter by using the single phase cascade H-bridge multi-level inverter. Analysis of different levels are compared and found total harmonics distortion (THD) content is approximately 40% less in seven levels than three level inverter. As levels are go increasing harmonics content decreases but up to particular point only.

#### REFERENCES

- Wahyn Mulyo Utomo, Afarulrazi abu Bakar, Suhaila Alias "Modeling of A Single Phase 7-Level Cascaded H-Bbridge Multilevel Inverter",(2.6) 2018 327-330 International Journal of Engineering & Technology

- J. I. Leon, S. Vazquez, S. Kouro, L. G. Franquelo, J. M. Carrasco, and J. Rodriguez, "Unidimensional Modulation Technique for Cascaded Multilevel Converters," IEEE Transactions on Industrial Electronics, vol. 56, no. 8, pp. 981-2986, Aug. 2009

- V.S. Kirthika Devi, and S. G. Srivani. "Performance assessment of PV energy conversion system with Buck-Boost and Cuk converter for cascaded H-Bridge inverter." 2016 Biennial International Conference on Power and Energy Systems: Towards Sustainable Energy (PESTSE). IEEE, 2016.

- V.S.Kirthika Devi, Dr.S.G.Srivani Iyengar "A New PWM Technique For symmetric and Asymmetric Seven Level Multilevel Inverter Topology with reduced number of DC sources" International Journal of Applied Engineering Research(IJAER), ISSN 0973-4562 Volume 10, Number 9, pp. 22299-22311, June (2015).

- S. Mekhilef, M. N. Abdul Kadir, and Z. Salam, "Digital control of three phase three-stage hybrid multilevel inverter," IEEE Trans. Ind. Informat., vol. 9, no. 2, pp. 719–727, May 2013.

- K. Ding, K.W. E. Cheng, and Y. P. Zou, "Analysis, of an asymmetric modulation methods for cascaded multilevel inverters," IET Power Electron., vol. 5, no. 1, pp. 74-85, Jan. 2012.

#### **AUTHORS PROFILE**

Ganesh H. Wani is an Engineering student of Electronics and Telecommunication Engineering at AISSMS Institute of Information Technology, Pune. His research interests include Power Electronics, Power Quality, Image processing.

Dr.D.K.Shedge is a Professor of Electronics and Telecommunication engineering at AISSMS Institute of Information Technology, Pune, received Ph.D from Savitribai Phule Pune University in 2015. His total teaching experience is 31 years. His research interests include Analog CMOS Design, Digital Signal Processing, Electronic measurement and control.

Retrieval Number: I8599078919/19©BEIESP DOI: 10.35940/ijitee.I8599.0881019 Journal Website: www.ijitee.org