# Three Phase 9-Level Hybridised Cascaded Multi-Level Inverter for Use in Smart Grid

Joshua Arumbakan, Kanchapogu Vaisakh

Abstract: Smart grid technology can be best utilized by having proper grid supporting equipment. This paper demonstrates the use of a three-phase, 9-level, hybridised cascaded multi-level inverter topology in a smart grid. A pulse width modulation scheme with phase disposition is employed in this inverter to control the firing signals to operate this circuit. These firing signals can be monitored and controlled for optimal usage in smart grid operation. Operational principles with switching equations are described in detail. Crucial voltage identification has been performed by analyzing the THD in output during source shortages by performing Fast Fourier transform analysis. Least THD of 15.82% is attained in the output voltage waveform of the proposed three phase inverter topology.

Keywords: inverter; hybridised, cascaded, 9-level; grid; smartgrid.

## **I.INTRODUCTION**

Smart grids can play a vital role in the world's technological advancement. A smart grid helps in the effective utilization of power by optimizing resources<sup>1</sup>. With the present day scenario of diminishing renewable energy resources, smart grids enable to connect all grid components to a central control hub to monitor and control the usage of power accordingly. A renewable energy based inverter when connected in synchronization through a smart grid to the main electrical grid results in lesser losses and better power utilization cum saving. Using modern inverters<sup>2-3</sup> the power conversion can be implemented with improved power quality. In previous developments, the diode-clamped<sup>4</sup>. flying-capacitor<sup>5,6</sup>, and cascaded H-bridge (CHB) multilevel inverters<sup>7</sup> were implemented and replaced the 3-level inverters<sup>8</sup> in medium and high-voltage applications<sup>9</sup> such as motors<sup>10</sup> and static var-compensator<sup>11</sup> applications.

Multi-level inverter topologies have better features of HV capability, reduced common mode voltages, almost sinusoidal outputs and helps in a smaller or even absence of output filter, that makes them suitable for use in applications of distributed generation<sup>12</sup> and also high power applications like traction<sup>13, 14</sup>. One of the most famous modulation strategies for the multi-level inverter topologies is sinusoidal pulse width modulation (PWM)<sup>15</sup>, which is used for two modes of carrier arrangements, namely level shifted (LS-PWM)

#### Manuscript published on 30 August 2019.

\*Correspondence Author(s)

Joshua Arumbakan, Research Scholar, Department of Electrical Engineering, Andhra University College of Engineering Visakhapatnam, Andhra Pradesh, , India.

Kanchapogu Vaisakh, Professor, Department of Electrical Engineering, Andhra University College Engineering Visakhapatnam, Andhra Pradesh, , India

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license <a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>

which is commonly known as phase disposition, and phase shifted (PS-PWM)<sup>16,17</sup>; and other well used modulation methods include multi-level SHE (selective harmonic elimination) and multi-level SVM18, 19 (space vector modulation). The main drawback of NPC inverter topology for implementation above three levels is the requirement of a capacitor voltage balancing control circuit and the high voltage applied across the clamped diodes; whereas the flying capacitor multi-level inverter uses the capacitors as clamping devices. The advantage of being used without the need of a transformer and redundant phase leg states which allow the switching stresses to be equally distributed among the power switches <sup>20,21</sup> is a very important characteristic of the FC topology in comparison with NPC topology. But, these inverters have the disadvantage of using numerous storage capacitors for high voltage levels, which can be quoted as a disadvantage.

A double flying capacitor multi-cell topology has been presented in Reference 22 which was implemented by adding two low-frequency switches to the standard configuration of the FC multi-level inverter. The main advantage of the proposed inverter in comparison with the flying capacitor multi-level inverter is the increase in the RMS value by two times of the output voltage and the voltage levels count and the neutering of the midpoint of the dc source. But, two extra switches must operate at the peak of the output voltage which also restricts the usage of this inverter in high voltage applications.

Asymmetric and/or hybrid multi-level inverters have been presented in References 23 and 24 in which the values of the dc voltage source magnitudes are unequal or alter dynamically. These topologies minimize the size and cost; and improve the reliability, since lesser switches and capacitors are employed<sup>25</sup>. The hybrid multi-level topologies include different multi-level topologies with unequal values of dc voltage sources and different modulation techniques used as per the different switches used for commutation. With appropriate selection of switching devices, the converter cost can be significantly reduced; but the application of different multi-level topologies leads to the deprivation of modularity and instills problems in switching frequency and restricts the modulation and control methods<sup>26</sup>.

The series connection of basic H-bridge inverters results in the multi-level CHB inverter configurations<sup>27</sup>, which have been known to have better operation. This inverter topology is a viable option for higher levels of operation because of its modular design and also because of the ease of control strategy. An NPC PWM 3-phase inverter having four switches in each arm has an output of 5-level voltage that

## Three Phase 9-Level Hybridised Cascaded Multi-Level Inverter for Use in Smart Grid

results in considerable suppression of the harmonic components when compared with the traditional full-bridge 3-level PWM inverters, which is not the case for single/three-phase PWM inverters. Majority of inverters adopt the full-bridge operation using sinusoidal modulation technique. The output voltage in them has two levels: zero and positive supply dc voltage levels in the positive half cycle making the harmonic components of the output voltage dependent on the carrier frequency. In order to expel these shortcomings, Sung-Jun Park proposed a 5-level PWM inverter which synthesizes five voltage levels per cycle. This inverter topology attenuated the harmonic components of the output waveforms compared with that of traditional fullbridge 3-level PWM inverter under symmetric dc voltage source and switching frequency.

This paper presents a three-phase, 9-level hybridised multilevel cascaded inverter topology, providing nine voltage levels per cycle per phase at the inverter output terminals. An additional clamping switch has been connected to improve the overall harmonic profile of the output waveforms. The major advantage is that the componentcount of the proposed inverter configuration is highly reduced when compared with the conventional CHB inverter, for similar output voltage and levels. Principles of operation and the switching functions are discussed in detail. Simulations in MATLAB/Simulink results are discussed to verify the validity of the three phase inverter topology.

## II.SMART GRID OPERATION

Most present generation grids have not altered for many decades and this characteristic of not evolving is a loss to the power sector. It is pitiful to be dependent on techniques that involve human interrogation and operation for faults occurring over an electrical grid. A century before today, electricity generation and consumption was limited to a few groups; and over time, development has been done by getting all the electrical grids on to a common frame, by interconnecting everything to a grid. This interconnection resulted in a massive grid that runs on a complex architecture and control strategy that is difficult to control and deal with. Recent advances in technology is giving options of updating the electrical grids to be smart in nature. As per the definition by National Institute of Standards and Technology(NIST), USA, a smart grid is "A modernized grid that enables bidirectional flows of energy and uses twoway communication and control capabilities that will lead to an array of new functionalities and applications"28; which means that the grid must be able to feed the load, and it must also be in a position to take energy from load points to be utilized at a place where there is requirement of power; and this power must be able to controlled and utilized in any way possible. As per Reference 29, Dr. S. Chakrabarti of IIT Kanpur states IEE defines smart grid to consist of the power and energy layer, the communication layer, and the IT/computer layer; which is a representation of the most important sections of the smart grid. The power and energy layer consist of the existing grid is to be interconnected to the various micro-grids, and the communication layer states the utilization of data collected from sensors connected over a smart grid and the IT/computer layer handles the data collected and requires coding to take the necessary action as and when needed. A smart grid typically consists of a number of sensors placed at the consumer, transmission and distribution sectors which are combinedly called as a smart grid. A smart grid can recognize a fault anywhere in the grid and take necessary action to isolate the fault causing path and also to reroute power to the power dependent loads so that less loads are affected by the outage. Also, the sensors placed properly help in identifying any fault accurately along with the location so that necessary action can be taken imminently to rectify the fault. Apart from this a smart grid has the capability to adapt to the load changes; the entire system is connected to the smart grid, and this enables the switch on and switch off of necessary units as per the load demand. A smart grid also does the task of collection and analysis of data through the cooperation of the consumer; i.e. the system collects data over a period of time, and algorithms are developed to understand and predict the increase or decrease of load requirement and thereby the system acts accordingly. Automation can be achieved without human intervention if a smart grid is installed perfectly. The inverter used in this chapter has the capability to function to satisfy the needs of a smart grid. Since renewable energy sources are not continuous or constant in nature, the smart grid adapts to the load requirement and draws power from suitable sources to maintain the load. This capability of the smart grid is very important as the main reason for blackouts or failing of a grid is due to unstable load requirements.

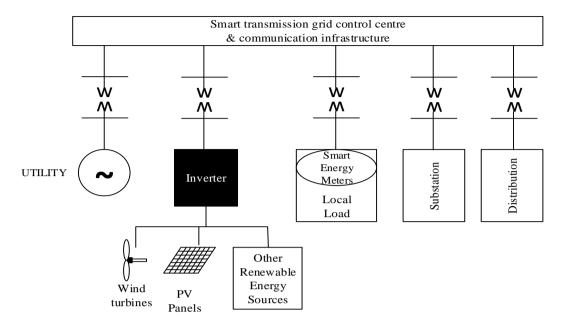

A smart grid uses advanced techniques to process the data available and it helps the grid to be ready and prevent any kind of power outage, as there is data available about the load requirement changes. The smart transmission grid control center shown in Figure 1 controls the entire operation of the grid; it controls when a source is to be connected to a grid, when to disconnect a faulty load and when to increase the power generation and when to decrease the generation i.e. it is like the central processing unit of the entire grid that controls through all the data available through the sensors. The communication infrastructure plays the role of collection of data to be processed by the smart transmission grid control center and also to send control signals to the required device when needed. It communicates with all the components available on the grid and gives instructions to them i.e. to control the operation of a circuit breaker, to send power through a different path after rerouting, etc. While connected to a smart grid, advanced technology of using a smart energy meter result in consumer's control of their load. The consumers can have a clear picture of the loads being used by them and over a period of time; thereby helping them reduce their load if possible during peak hours to help the environment and to prevent any outages in the grid. And since majority of the power bill is generated based on usage during peak hours, the consumer has the option to reduce the power consumption cost by using automation or Internet of things<sup>30</sup> to use certain power consuming loads

vw.iiitee.ora

Retrieval Number: J10820881019/19©BEIESP DOI: 10.35940/ijitee.J1082.0881019 Journal Website: www.ijitee.org

during low demand hours that is advantageous to both the consumer as well as the grid integrity. Smart grid takes time to be implemented over the entire grid, but once

implemented properly, it results in a flawless grid with minimal losses.

Fig. 1 Smart grid representation along with the inverter

## III.BASIC INVERTER TOPOLOGY

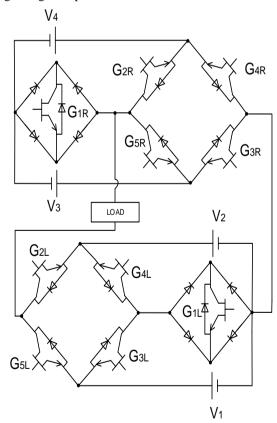

The proposed three-phase, 9-level cascade multi-level inverter, whose one phase is shown in Fig. 2is a cascaded multi-level inverter. Each of the two cells comprises a conventional H-bridge with one bidirectional switch connected to the center point of two dc sources. Proper switching of the inverter results in nine output-voltage levels:  $V_A$ ,  $2V_A$ ,  $3V_A$ ,  $4V_A$ , 0,  $-V_A$ ,  $-2V_A$ ,  $-3V_A$ ,  $-4V_A$ . The highest number of voltage levels attainable by cascading xnumber of 5-level inverter is 4x + 1.

Similar result was obtained by cascading NPC converter with a higher number of switching components. The additional switches G<sub>IL</sub> and G<sub>IR</sub> must be properly switched for controlling the direction of the load current. Table 1 shows the switching combinations that generated the nine output voltage levels (VA, 2VA, 3VA, 4VA, 0, -VA, -2VA, - $3V_A$ ,  $-4V_A$ ).

The switching functions of a phase of the proposed threephase 9-level hybridised cascaded multi-level inverter are realized by the use of basic logical AND, OR and NOT gates, which are as given in equations 1-10 in Section 4.The inverter is a robust model which can be used for different modulation indexes too. The area of discussion in this chapter confines to a modulation index of 1 with crucial voltage identification being the main aim. All the switches used are IGBTs which are controlled by a PWM scheme are discussed in Section 4. A single phase output has been discussed in detail as other phases correspondingly produce the same output.

The actual representation of a single phase in the proposed three phase inverter is shown in Fig.2.with ten IGBTs and 16 Diodes; and 4 symmetric sources. A hardware implementation can be incorporated by selecting devices as per the magnitude of the sources used. The main area of study is regarding the operation of the inverter.

Fig. 2 1-phase of the proposed inverter model

w.iiitee.ord

Retrieval Number: J10820881019/19©BEIESP DOI: 10.35940/ijitee.J1082.0881019 Journal Website: www.ijitee.org

| $G_{1L}$ | $G_{2L}$ | $G_{3L}$ | $G_{4L}$ | $G_{5L}$ | $G_{1R}$ | $G_{2R}$ | $G_{3R}$ | $G_{4R}$ | $G_{5R}$ | $V_0$ |

|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|-------|

| 0        | 0        | 1        | 0        | 0        | 1        | 0        | 1        | 0        | 0        | V     |

| 0        | 0        | 1        | 0        | 0        | 0        | 1        | 1        | 0        | 0        | 2V    |

| 1        | 0        | 1        | 0        | 0        | 0        | 1        | 1        | 0        | 0        | 3V    |

| 0        | 1        | 1        | 0        | 0        | 0        | 1        | 1        | 0        | 0        | 4V    |

| 0        | 0        | 1        | 0        | 0        | 0        | 0        | 1        | 0        | 0        | 0V    |

| 0        | 0        | 0        | 0        | 1        | 0        | 0        | 0        | 0        | 1        | 0V    |

| 0        | 0        | 0        | 1        | 0        | 1        | 0        | 0        | 1        | 1        | -V    |

| 0        | 0        | 0        | 1        | 0        | 0        | 0        | 0        | 1        | 1        | -2V   |

| 1        | 0        | 0        | 1        | 0        | 0        | 0        | 0        | 1        | 1        | -3V   |

Table. 1 Switching combinations for a single phase

The switching pattern of the gate pulses are as given in Table 1. The table describes each and every switching pattern for producing each level in the output. The switching table changes for phases B and C as per the reference waveform used. Since the input voltage sources are all symmetrical, the output  $V_0$  is referred as V, 2V, 3V, 4V, -V, -2V, -3V, -4V in the given table.

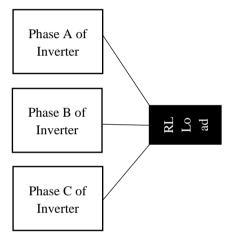

Fig. 3 Three phase layout of the proposed inverter

# IV.MODULATION TECHNIQUE

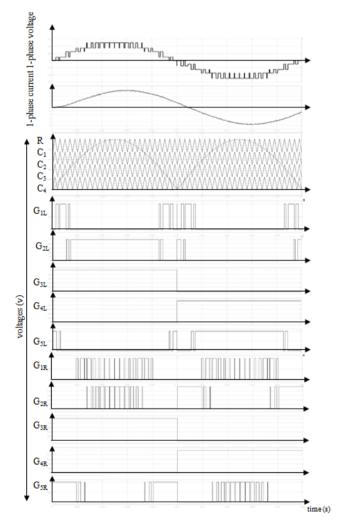

The entire power electronic circuit of an inverter is controlled by the modulation technique of the inverter. A phase disposition pulse width modulation scheme is used to control the firing pulses of the switches. A reference waveform which is a sinusoidal signal of frequency 50Hz in this case is compared with carrier waveforms, which are triangular pulses with a frequency of 5KHz are used for the

generation of pulses to control the switches. The governing equations of the topology are shown from equations 1-10.

$$G_{1L} = \bar{R} \le C_1 \tag{1}$$

$$G_{2L} = \overline{(\overline{R} \le C_1)} + (\overline{R} \le C_2) \tag{2}$$

$$G_{3L} = \overline{(\bar{R} \le C_2)} + (\bar{R} \le C_3) \tag{3}$$

$$G_{4L} = \overline{(\bar{R} \le C_3)} + (\bar{R} \le C_4) \tag{4}$$

$$G_{5L} = \overline{(\bar{R} \le C_4)} \tag{5}$$

$$G_{1R} = R \le C_1 \tag{6}$$

$$G_{2R} = \overline{(R \le C_1)} + (R \le C_2) \tag{7}$$

$$G_{2R} = \frac{(R \le C_1)}{(R \le C_2)} + (R \le C_2)$$

$$G_{4R} = \frac{(R \le C_2)}{(R \le C_3)} + (R \le C_4)$$

$$G_{5R} = \frac{(R \le C_4)}{(R \le C_4)}$$

(9)

$$G_{4R} = \overline{(R \le C_3)} + (R \le C_4) \tag{9}$$

$$G_{5R} = \overline{(R \le C_4)} \tag{10}$$

Where  $G_{1L}$ ,  $G_{2L}$ ,  $G_{3L}$ ,  $G_{4L}$ ,  $G_{5L}$ ,  $G_{1R}$ ,  $G_{2R}$ ,  $G_{3R}$ ,  $G_{4R}$ ,  $G_{5R}$ are the gate pulses generated, R is the rectified sinusoidal reference waveform, C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub>, C<sub>4</sub> are carrier triangular waveforms of 5kHz ranging from [0-0.25], [0.25-0.5], [0.5-0.75], [0.75-1] respectively.

## V.SIMULATION RESULTS

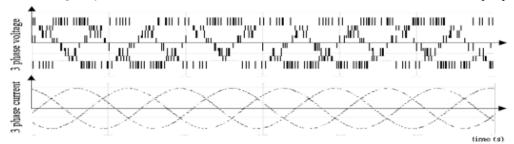

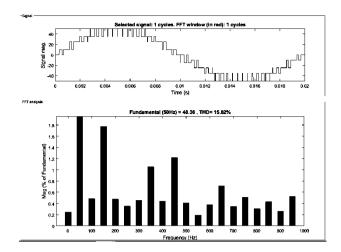

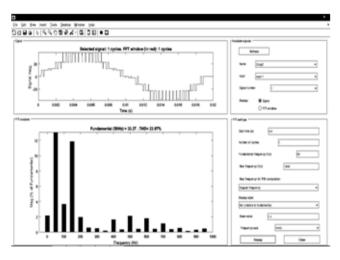

MATLAB's SIMULINK environment is used for the simulation of the proposed three phase topology and processing of the gate signals used to drive the circuit components. This is a symmetric modulated inverter and the output voltage is the sum of the input voltage sources used. This topology was simulated with  $V_1=V_2=V_3=V_4=12.5V$  per phase in the present simulation; the detailed results of a single phase of the simulated topology i.e. the reference, carrier signals and gate pulses has been shown in Figure 4, and the three phase output has been shown in Figure 5. The load used is an RL-load of  $10\Omega$ , 100mH per phase.

Fig. 4 Three phase output voltage and current observed

Fig. 5 THD of a phase of the three phase inverter

Fig. 6 Single phase output voltage and current with corresponding gate pulses

# VI.CRUCIAL VOLTAGE IDENTIFICATION

A crucial voltage source is that which when disrupted would change the circuit's parameters to the maximum. Simulation tests have been carried out to recognize the crucial voltage in the proposed topology so as to take the necessary precautions when implemented in hardware. Recognizing the crucial voltage source enables us to select a source of consistent magnitude at the crucial source point so as to avoid any derange in the circuit output.

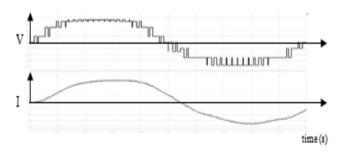

## Case 1 (When V<sub>1</sub>=0V)

The voltage source  $V_1$  is set to zero in simulation, so as to observe the behavior of the proposed topology. The voltage and current vary as shown in Fig. 7and the harmonic distortion is shown in Fig. 8.

Fig. 7 Voltage and current when  $V_1=0V$

Fig. 8 THD at the condition when V<sub>1</sub>=0

The number of voltage steps are reduced to 7 and the THD is increased to 17.42%.

## Case 2 (When $V_2=0V$ )

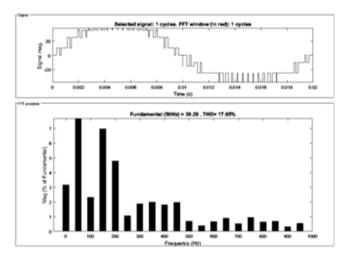

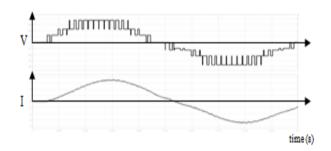

The voltage source  $V_2$  is set to zero in simulation, so as to observe the behavior of the proposed topology. The voltage and current waveforms generated are as shown in Fig.9and the harmonic distortion is as shown in Fig. 10.

Fig. 9 Voltage and current when V<sub>2</sub>=0V

Retrieval Number: J10820881019/19©BEIESP DOI: 10.35940/ijitee.J1082.0881019 Journal Website: www.ijitee.org

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) 4616 © Copyright: All rights reserved.

## Three Phase 9-Level Hybridised Cascaded Multi-Level Inverter for Use in Smart Grid

Fig. 10 THD at the condition when V<sub>2</sub>=0

The number of voltage levels are reduced to 7 and the THD is increased to 17.65% which is higher than the case when  $V_1=0$ .

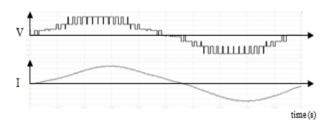

#### Case 3 (When V<sub>3</sub>=0V)

The voltage source V<sub>3</sub> is set to zero in simulation, so as to observe the behavior of the proposed topology. The voltage and current waveforms generated are as shown in Fig.11.and the harmonic distortion is as shown in Fig. 12.

Fig. 11 Voltage and current when V<sub>3</sub>=0V

Fig. 12 THD at the condition when  $V_3=0$

The number of voltage steps are reduced to 7 and the THD is increased to 24.52% which is higher than the case when  $V_1=0$  and  $V_2=0$ .

## Case 4 (When V<sub>4</sub>=0V)

The voltage source V<sub>4</sub> is set to zero in simulation, so as to observe the behavior of the proposed topology. The voltage and current vary as shown in Fig.13and the harmonic distortion is as shown in Fig.14.

Fig. 13 Voltage and current when V<sub>4</sub>=0V

Fig. 14 THD at the condition when V<sub>4</sub>=0

The number of voltage levels are reduced to 7 and the THD is increased to 23.59%. which is higher than the case when  $V_1=0$  and  $V_2=0$ , but lesser than the case when  $V_3=0$ .

### VII.RESULTS & DISCUSSIONS

A Three Phase 9-Level Hybridised Cascaded Multi-Level Inverter for use in Smart grid was implemented and its crucial voltage was identified in this paper. The proposed three phase topology can be implemented in a smart grid comprising of similar voltage magnitude sources. The ability to monitor and control the switching pulses results in complete control and working of the inverter linked with the smart grid. The exhibited harmonic profile is reasonable at 15.82% and the crucial voltage identification test resulted in the harmonic distortions of 17.42% when V<sub>1</sub>=0, 17.65% when  $V_2=0$ , 24.52% when  $V_3=0$ , and 23.59% when  $V_4=0$ ; this test shows that V<sub>3</sub>is the most crucial voltage source in the inverter setup in of the available three phases.

So, special precautions must be considered during hardware implementation to keep the voltage source 3 in all the phases stable.

## REFERENCES

- 1. FangxingLi; Wei Qiao; Hongbin Sun; Hui Wan; Jianhui Wang; Yan Xia ; Zhao Xu ; Pei Zhang, 'Smart Transmission Grid: Vision and Framework', IEEE Transactions on Smart Grid (Volume:1, Issue: 2, Sept. 2010), pp.168-177

- Hammond, P.W.: 'A new approach to enhance power quality for medium voltage drives'. Proceedings 1995 IEEE-IAS Petroleum and Chemical Industry Committee, 1995, pp. 231-235

- Lai, J.S., Peng, F.Z.: 'Multi-level converters-a new breed of power converters'. Conf. Rec. 1995 IEEE-IAS Annual Meeting, 1995, pp. 2348-2356

- Nabae, A., Takahashi, I., Akagi, H.: 'A new neutral-point-clamped PWM inverter', IEEE Transactions on Industry Applications, 1981, 17, (5), pp. 518-523

- Choi, N.S., Cho, J.G., Cho, G.H.: 'A general circuit topology of multilevel inverter'. Conf. Rec. 1991 IEEE Power Electronics Specialists Conference, 1991, pp. 96–103

- Meynard, T.A., Foch, H.: 'Multi-level conversion: high-voltage chopper and voltage-source inverters'. Conf. Rec. 1992 IEEE Power Electronics Specialists Conference, 1992, pp. 397-403

- Fang Zheng Peng ; J.W. McKeever ; D.J. Adams: 'A power line conditioner using cascade multilevel inverters for distribution systems', IEEE Transactions on Industry Applications, 1998, 34, (6), pp. 1293-

- Zhang, J. 'High performance control of a 3 level IGBT inverter fed AC drive'. Conf. Rec. 1995 IEEE Industry Applications Society Annual Meeting, 1995, pp. 22-28

- Menzies, R.W., Steimer, P., Steike, J.K.: 'Five-level GTO inverters for large induction motor drives'. Conf. Rec. 1993 IEEE Industry Applications Society Annual Meeting, 1993, pp. 595-601

- 10. Marchesoni, M., Mazzucchelli, M.: 'Multi-level converters for high power AC drives: a review'. Proc. IEEE International Symposium on Industrial Electronics'93, Budapest, Hungary, 1993, pp. 38-43

- 11. Hochgraf, C., Lasseter, R., Divan, D., Lipo, T.A.: 'Comparison of multi-level inverters for static var compensation'. Conf. Rec. 1994 IEEE- Industry Applications Society Annual Meeting, 1994, pp. 921-

- 12. M.H.J. Bollen; A. Sannino, "Voltage control with inverter-based distributed generation", IEEE Transactions on Power Delivery, Vol.20 (9), 2005, pp.519-520

- 13. Tolbert, L.M., Peng, F.Z.: 'Multi-level converters for large electric drives'. Proceedings of IEEE Applied Power Electronics Conference'98, 1198, vol. 2, pp. 530-536

- Bernert, S.: 'Recent developments of high power converters for industry and traction application', IEEE Transactions on Power Electronics, 2000, 15, (6), pp. 1102-1117

- 15. Carrara, G., Gardella, S., Marchesoni, M., Salutari, R., Sciutto, G.: 'A new multi-level PWM method: a theoretical analysis', IEEE Transactions on Power Electronics, 1992, 7, (3), pp. 497–505

- 16. McGrath, B.P., Holmes, D.G., Meynard, T.: 'Reduced PWM harmonic distortion for multi-level inverters operating over a wide modulation range', IEEE Transactions on Power Electronics, 2006, 21, (4), pp. 941-949

- 17. Kouro, S., Lezana, P., Angulo, M., Rodriguez, J.: 'Multicarrier PWM with DC-link ripple feedforward compensation for multi-level inverters', IEEE Transactions on Power Electronics, 2008, 23, (1), pp. 52-59

- 18. Celanovic, N., Boroyevich, D.: 'A fast space-vector modulation algorithm for multi-level three-phase converters', IEEE Transactions on Industry Applications, 2001, 37, (2), pp. 637-641

- Gupta, A.K., Khambadkone, A.M.: 'A general space-vector PWM algorithm for multi-level inverters, including operation in overmodulation range', IEEE Transactions on Power Electronics, 2007, 22, (2), pp. 517-526

- 20. Fazel, S.S., Bernet, S., Krug, D., Jalili, K.: 'Design and comparison of 4-kV neutral-point-clamped, flying-capacitor, and series-connected Hbridge multi-level converters', IEEE Transactions on Industry Applications, 2001, 37, (2), pp. 637–641, 2007, 43, (4), pp. 1032–1040

- 21. McGrath, B.P., Holmes, D.G.: 'Analytical modelling of voltage balance dynamics for a flying capacitor multi-level converter', IEEE Trans. Power Electron., 2008, 23, (2), pp. 543-550

- 22. Sadigh, A.K., Hosseini, S.H., Sabahi, M., Gharehpetian, G.B.: 'Double flying capacitor multicell converter based on modified phase-shifted pulsewidth modulation', IEEE Trans. Power Electron., 2010, 25, (6), pp. 1517-1526

- 23. Rech, C., Pinheiro, J.R.: 'Hybrid multi-level converters: Unified analysis and design considerations', IEEE Trans. Ind. Electron., 2007, 54, (2), pp. 1092-1104

- 24. Rech, C., Pinheiro, J.R.: 'Line current harmonics reduction in multipulse connection of asymmetrically loaded rectifiers', IEEE Trans. Ind. Electron., 2005, 52, (3), pp. 640-652

- 25. Rodriguez, J., Franquelo, L.G., Kouro, S., et al.: 'Multi-level converters: an enabling technology for high-power applications', Proc. IEEE, 2009, 97, (11), pp. 1786-1817

- 26. Malinowski, M., Gopakumar, K., Rodriguez, J., Perez, M.: 'A survey on cascaded multi-level inverters', IEEE Trans. Ind. Electron., 2010, 57, (7), pp. 2197-2206

- 27. Charles I. Odeh, Damain B. N. Nnadi, "Single-phase 9-level hybridised cascaded multi-level inverter", IET Power Electronics, 2013, pp.468-

- 28. https://www.nist.gov/engineering-laboratory/smart-grid

- 29. https://www.iitk.ac.in/ime/anoops/for15/ppts/

- Amanda Saint "Where next for the internet of things? [Information Technology Internet of Things]", Engineering & Technology, IEEE, Volume: 10, Issue: 1,2015, pp. 72-75.