# Design of the Configurable Watch Dog Timer using FPGA in Space Probe Application

Varsha Parekh, Pogaku Divya, K.Srilatha, P.Chitra

Abstract: Watchdog timer is a simple timer circuit. It is an indispensable part and is of paramount importance when coming to the embedded system. Most implementations of watch dog are simply based on simple feed dog strategy covering merely limited abnormal states of program. There are different types of watch dog timers due to the increasing need. They include Standard watchdog timer, Windowed watch dog timer, sequenced watch dog timer. But an effective watch dog timer should be able to detect all abnormal software modes and bring the system back to a known state. In addition to that, it must have its own clock and should be capable of providing a hardware reset on timeout to all the peripherals which the current timers lag. Hence the windowed watchdog timer where the window periods can be configured during the software initialization. In the watchdog timers which are available right now is processor dependent due to which there is a increase in the timing but there is a need of a watchdog timer which has capability to cut down or reduce timing hence watchdog timer which has got service, frame and controller windows have been used, which is independent of the processor and hence the timing is reduced effectively.

Index Terms: Watchdog Timer, Field Programmable Gate Array, Service Window, Frame Window, Controller Window.

# I. INTRODUCTION

Watchdog timer has been employed to various applications depending on the needs it has been also enhanced for particular usage. Watch dog timers find their use in the enhancing of imaging system in the presence of the soft errors. This error occurs when a radiation event causes a charge disturbance resulting in two types of errors which are data error and control flow error. Data error results in change of data stored in memory location of the microprocessor's register whereas the control flow error results in change of instruction address which causes the microprocessor to execute the incorrect next instruction [1]. Now at this point

Manuscript published on 30 August 2019.

\*Correspondence Author(s)

Varsha Parekh, Depart. of Electronics and Communication Engineering Sathyabama Institute of Science and Technology, Chennai.

Tamilnadu, India.

Pogaku Divya, Depart. of Electronics and Communication Engineering Sathyabama Institute of Science and Technology, Chennai.

K.Srilatha, Assistant Professor, Depart. of Electronics and Communication Engineering, Sathyabama Institute of Science and Technology, Chennai. Tamilnadu. India.

P.Chitra, Associate Professor, Depart. of Electronics and Communication Engineering. Sathyabama Institute of Science and Technology, Chennai.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license http://creativecommons.org/licenses/by-nc-nd/4.0/

there is a need of the watch dog timers like the standard and windowed. Whenever an input is given to the watchdog timer, it not only just detects the error but it has got a function in which counter is employed which counts the stored data and compares with the input and sees to it whether the error has occurred or not. In the watchdog timers available among them we have got standard watchdog timer, windowed watchdog timer. Windowed Watchdog has got a service window, frame window and controller window which are given to parameters like temperature, pressure and heat. The service window is smaller than the frame window. The windows can be programmed by writing the bit fields which is SWLEN and FWLEN in configuration register. The INIT input is the one through which the watchdog timer gets initialized. A high to low transition on the given input will start the service window the fail flag is in active because that is when the error occurs and the states no transition to be done. It is also possible to use an external interval timer to avoid the processor's intervention in generation of the INIT signal. But this kind of the configuration is been applied only when the task in required to be done in frames. On the power up the WDFAIL output has been asserted high but it is the sole responsibility of the software to initialize the watchdog and keep it running and to make that happen, which is bringing the watchdog to a working state, the watchdog reset which WDRST must be toggled from low to high and hence due to this action the watchdog inside the service window will trigger the WDFAIL flag and make it in the working condition. No failures will be registered by the watchdog timer as long as the frame window counters are being running if any fault occurs then there is a need when the watchdog resets the system and then shows that error has occurred at the data out by raising flag and enabling error occurrence on the other side no error occurrence indicate that the initial value at the data output.

A minimum value has been set at particular parameter indicating that the error has occurred at particular parameter and notifying the watch dog timer that if that particular value has been encountered then the watch dog fail occurs and setting the output to fail at that particular parameter whether it could be the heat, pressure or temperature. Now when the values given other than the parameter which causes the error then there will be a normal functioning of the system and consist of the SYSRST and the SYSCLK in which the SYSRST indicate the reset of the system when the error has occurred and the SYSCLK indicates the clock functioning or the start of the process [8].

# Design of the Configurable Watch Dog Timer using FPGA in Space Probe Application

Now the start of the service window, frame window and controller window is done by giving the enable of those respective windows as one which is (ENABLE=1). And the output to be displayed is given by the RSTOUT which is the point showing the output either the error occurred or the normal functioning. It is an indication as through which we can get to know that the error has occurred indicating the parameter of the error more specifically either heat may be and in the cases other that it indicates the normal functioning simulating output and displaying the initial value in the system. Hence windowed watchdog timer has been employed since it is more reliable. Windowed Watchdog timer has been used for many such applications. One such application includes the Space probe application. Since we have employed a windowed watchdog timer all the values for it are being set that is service window, frame window and the controller window. It discusses the implementation of the proposed watchdog timer in a Field Programmable Gate Array (FPGA).

#### II. MATERIALS AND METHODS

In the existing system the watchdog timer is a processor dependent. In detail the procedure of the functioning is like when an input is given to the system the value which is been given is being first checked with the temperature, pressure and heat values these error values for the parameters are the sensor values [5]. Most importantly the watchdog timer is not just used for checking the error occurrences but it is being used for the counter to check the values by counting and if the particular is being matched with the error value then the FAILFLAG 1 indicating that the fail has occurred and thereby giving the WDFAIL to one and so the WDFAIL is been set to one and then the processor is been given to that watchdog timer which indicates the watchdog timer to reset the system and then resets RSTOUT=1 the whole system. If there is no error occurred then the output is the same initial value which is given as an input. Now the whole process is dependent on the processor and the timing is increased so there is a need for the reduction in the timing and hence making the system for the quick process to occur. In this the use of the watchdog timer dependent on the processor which and indicate the temperature, pressure and heat together and then the error is shown at last without clearly showing where the error has occurred [7]. So that the particular error has been showed at last which tells that it is a system dependent on the processor.

## III. METHODOLOGY

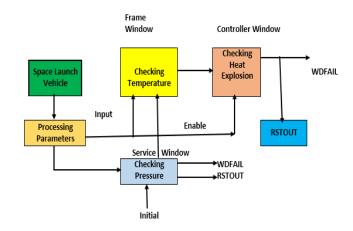

In the proposed system a processor independent system is been employed. From the below given block diagram it is shown that evident that the space launch vehicle has got the processing parameters that is the register and given to the service window, frame and controller window for checking of the pressure, temperature and the heat and if error at any of those error matches to the error value at the sensor value then the WDFAIL=1 and data out shows the error value of the parameter and holds it. Then goes to the other parameter and checks, if no error finally at the output it displays the error value which has been on hold indicating the error has occurred. Later when there is no occurrence of the error then

the initial value is being displayed in the system. Hence if an input value other than the error value given to the system then the initial value is only been displayed and showing that the no error has been occurred in the system. It is through this we can tell that it is not a processor dependent and can show the error at that particular value implying the error has occurred [3]. In terms of this no error can be show that the initial value is only displayed at the output and on the error cases the value with the error has been displayed Fig.No.1.

Fig.No.1: Block diagram of proposed system

The above block diagram is the proposed application of the space probe in which the parameters of the space launch vehicle like pressure, temperature and heat are being assigned to the service, frame and the controller window

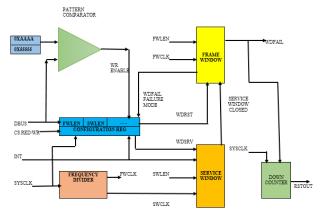

Fig.No.2.Funcational block diagram of proposed Watchdog timer respectively.

The windows are active when the enable is given as one for each one of them. After giving an enable to 1 to each one of them and also initializing the input then the process starts in the system checking first by counter one by one and then the detection of the error if the error has occurred else there is a normal display of the output Fig.No.2.which is the initial value.

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) 3556 © Copyright: All rights reserved.

#### IV. RESULTS AND DISCUSSION

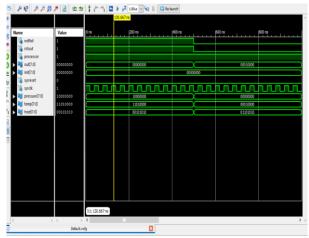

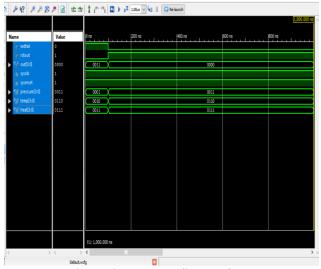

Fig.No.3: Existing System Output

The Fig.No.3 above simulation is for the existing system where it is dependent on the processor and the wdfail=1, Processor=1. Since the wdfail=1 in the error is shown and so the fail flag will be set to 1 and sent to wdfail where this wdfail =1 and be indicated to processor then the reset action will be performed. Now this whole existing system is on a major portion dependent on processor and then action is being performed of the system reset which takes a quite a while so the proposed system is employed with Frame Window, Service and Controller Window.

Fig.No.4: Proposed System Output

The above Fig.No.4 simulation is for proposed system where it is independent of the processor and wdfail=0 and so output is shown with init value. Here it has got the the usage of windows so it is independent on the processor and hence the timing pertaining to the indication to watchdog timer is less and hence useful and Frame Window, Service and Controller Window is one of major reasons of its deployment in the Watchdog timer.

## V. CONCLUSION

On the whole, the former system where using of watchdog timer is dependent on the processor where the timing is a major portion as it has to indicate the fail flag which would indicate the wdfail and to the processor implying a time consuming process. In addition to it where in

the proposed system has got the vital role such as the parameters of the heat, temperature and pressure are set to a error value where the fail flag would indicate and at those points the watchdog fail will be shown further the values which are set as error the sensor values and so at those points the error will be shown indicating the watchdog fail and when the error is not being encountered then the out will show its value either heat, temperature or pressure. In the next portion after the error has occurred then at the place where the has not occurred it would directly display the initial value which would correspond to clearance of error and hence that is how the functioning of the watchdog timer would take place indicating the timing is reduced and hence the employment of this watchdog timer using the frame window, service window and controller window indicating the heat, pressure and temperature respectively. The proposed system hence has got its major use in the space probe application where it would indicate the error at the point of occurrence and showing its scope in the application other than that to. It is therefore used in the functioning of the space probe application where it is independent on the processor and timing is cut down. Majorly timing is consideration and it is been achieved through the employment of the frame, service and controller window respectively.

## REFERENCES

- 1. Ganssle, J. G. 2008. The Art of Designing Embedded Systems. Second Edition, Elsevier, 298.

- 2. Kochan, R.; Kopylchak, A. &Korkishko, T. 2002. Improved watchdog timer for control the IBM PC based autonomous computer systems, in 'Modern Problems of Radio Engineering, Telecommunications and Computer Science. 181-182.

- 3. Giaconia, G.; Di Stefano, A. & Capponi, G. 2003. FPGA-based concurrent watchdog for real-time control systems, Electronics Letters 39(10), 769-770.

- 4. Pohronská, M. and Krajčovič, T. 2010. Fault-tolerant embedded systems with multiple FPGA implemented watchdogs. Proceedings of the International Conference CYBERNETICS AND INFORMATICS.

- 5. K.Ashok, K.Srilatha.2017.An implementation of the customer domain of the smart grid embedded in an internet of things" ARPN Journal of Engineering and Applied Sciences. vol.12(19).5653-5657.

- 6. Lennon, W.K., &Passino, K. M.2009. Intelligent Control for Brake Systems, IEEE Transactions on Control Systems Technology, Vol.7.188-202.

- 7. P. Garcia, K. Compton, M. Schulte, E. Blem, and W. Fu.2006.An overview of reconfigurable hardware in embedded systems," EURASIP Journalon Embedded Systems, vol. no. 1.13-13.

- 8. W.Sai Raghavendran, S.V.Raju, K.Srilatha. 2016. A novel approach to build a low cost architecture for offthe shelf target tracking using wireless communication", ARPN Journal of Engineering and Applied Sciences", vol.11(15).9242-9250.

- 9. Pohronská, M. and Krajčovič, T. 2010. "Embedded Systems with Increased Reliability Using the Multiple Watchdog Timers Approach, International Conference of Applied Electronics Proceedings. 273-276.

## **AUTHORS PROFILE**

Varsha Parekh, Bachelor of Engineering in Electronics and communication Engineering, Department of Electronics Communication Engineering, Sathyabama Institute of Science and Technology, Chennai, Tamilnadu, India. Her research interests in IOT, Embedded Systems and Wireless Sensor Network.

Pogaku Divya, Bachelor of Engineering in Electronics communication Engineering, Department of Electronics Communication Engineering, Sathyabama Institute of Science and Technology, Chennai, Tamilnadu, India. Her research and

w.ijitee.org

interests in IOT, Embedded Systems Image Processing.

# Design of the Configurable Watch Dog Timer using FPGA in Space Probe Application

Ms.K.Srilatha, graduated with Distinction in Electronics and Communication Engineering in 2002 from Madras University, Chennai, India. She completed her Post graduation with Distinction in Applied Electronics in 2005 from Sathyabama University Chennai, India. She is pursuing her Ph.D. in Medical Image Processing at Sathyabama Institute of Science and Technology. Presently she also holds a faculty position as Assistant Professor, Department of Electronics and Communication Engineering, Sathyabama Institute of Science and Technology, Chennai, Tamilnadu, India. She has 15 years of experience in teaching. She has several research publications in well known International and National journals and also conferences. Her current research interests in Machine Learning, Signal and Image Processing,, Embedded Systems and Wireless Communication. She is also a Life time Member of Indian Society for Technical Education (ISTE).

**Dr.P.Chitra**, graduated in Electronics and Communication Engineering in She completed her Post graduation in Communication Systems, India. She had done her Ph.D. in Image Processing at Sathyabama Institute of Science and Technology. Presently she also holds a faculty position as Associate professor, Department of Electronics and Communication Engineering, Sathyabama Institute of Science and Technology, Chennai, Tamilnadu, India. She has a more than one decade of xperience in teaching. She has several research publications in well known International and National journals and also conferences. Her current research interests in Digital Signal and Image Processing, Embedded Systems and Wireless Communication. She is also a Life time Member of Indian Society for Technical Education (ISTE).

Retrieval Number: J97640881019/19©BEIESP DOI: 10.35940/ijitee.J9764.0881019 Journal Website: www.ijitee.org