# Fifteen Level Cross H Bridge Multilevel Inverter Fed PMSM

B. Yogeswara Reddy, J. Srinivas Rao, T. Suresh Kumar, A. Nagarjuna

Abstract: Modeling and simulation of fifteen level cross H bridge multilevel(ML) inverter fed three-phase PMSM presented in this paper. In order to overcome the setbacks of an inverter via switching losses and harmonic disturbance, Cross H bridge MLI topology is developed. The number of switches and DC voltages considered in this model are much inferior to other inverter topologies. The topology presented in the paper has better output and lower harmonic distortion (THD). Also, Permanent Magnet Synchronous Motor (PMSM) have significant advantages over other drives. Analysis and Simulations of 5, 9 and 15 level cross H bridge MII were performed and presented.

Keywords: Multicarrier Sinusoidal PWM (MSPWM), Multilevel Inverter (MLI), PMSM, Total harmonic distortion.

## I. INTRODUCTION

Multi-level Inverters (MLI) have attained more recognition over two level(2L) and three level(3L) inverters. The basic concept of the multilevel inverters is to split the input source voltage of the inverter in between switches so that low voltage switches can be used to exercise steep voltage outputs [1]-[2]. Multi-level inverters widely used energy sector industries for reactive power compensation and drive control. The multiple levels of voltage present in the output of MLI enhance voltage output with the reduction of harmonic content and it boosts the efficiency. Among the MLI topologies, the cascaded multi-level inverters have received more attentiveness because of the simple structure and extreme modularity and no voltage balance problems. The switches demanded in cascaded multi-level(ML) inverters are more than the cross H Bridge MLI topology for same level of output voltage. Increasing the quantity of power electronic switches will escalate the cost, switching losses and decreases efficiency of the system. This cross H bridge topology has eminent edge over cascaded MLI in terms of switches used and harmonic percentage of output voltage[3]-[7]. With this topology the cost is minimized and the efficiency of system is improved. Permanent magnet synchronous motors are becoming dominant in the domain of

# Manuscript published on 30 September 2019.

\*Correspondence Author(s)

B. Yogeswara Reddy\*, PG Scholar, EEE Department, Gokaraju Rangaraju Institute of Engineering & Technology, Hyderabad, INDIA. Email: yogibadepalli@gmail.com

J. Srinivas Rao, Research Scholar, EEE Department, KLEF, Vaddeswaram, INDIA. Email: janigasrinivasrao@gmail.com

Dr. T. Suresh Kumar, Professor, EEE Department, Gokaraju Rangaraju Institute of Engineering & Technology, Hyderabad, INDIA

Nagarjuna, PG Scholar, EEE Department, Gokaraju Rangaraju Institute of Engineering & Technology, Hyderabad, INDIA.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license http://creativecommons.org/licenses/by-nc-nd/4.0/

variable speed AC drives predominantly in Electric vehicles and hybrid EV's. The usage of PMSM is to produce significant air gap magnetic flux which creates it possible to design immensely efficient PM motors. With increasing trend towards green energy in all sectors, PMSM drives seem to be ideal replacement for induction drives in coming years [8]-[9]. Evaluation of multilevel inverters in adjustable speed drives is escalated by demand of potential and improvement in MLI. The PMSM now a days becoming more popular in ASDs (Adjustable Speed Drives) due to its notable merits such as solidness, wide constant power region, higher power density, insignificant misfortunes and requirement of cheap maintenance. In recent times, the magnetic and thermal capabilities of the PM have been strengthened by employing the high-coercive PM material and thus the PM synchronous motor is oftentimes used as an effective actuator in aerospace industries to reduce the fuel consumption [9]-[12]. PMSM is exceptionally efficient due to non-existence winding in the rotor. This paper illustrates the simulation and outcome of sinusoidal PWM based fifteen level cross H bridge inverter fed PMSM drive with details. A relative assessment on 5,9 and 15 level cross H bridge inverter fed PMSM drive is also presented.

### II. CROSS H BRIDGE MULTILEVEL INVERTER

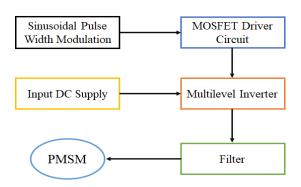

Fig.1. Block diagram of 15 level cross H bridge multilevel(ML) inverter fed PMSM

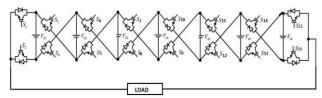

Figure (1) shows the block diagram of fifteen level cross H bridge multilevel(ML) inverter fed PMSM. Figure (2) shows the schematic line lay-out of single-phase cross H bridge multi-level(ML) inverter and it consists of seven voltage sources and sixteen switches. In the figure (2) the switches and DC voltage sources are cross connected and with appropriate switching the expected output voltage is generated. This topology can also be enhanced to 'n' number of levels and the switching sequence changes accordingly depend on the output level[1,2].

w.ijitee.org

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) 1194 © Copyright: All rights reserved.

Retrieval Number: J92950881019/19©BEIESP DOI: 10.35940/ijitee.J9295.0981119 Journal Website: www.ijitee.org

## Fifteen Level Cross H Bridge Multilevel Inverter Fed PMSM

In this topology, the equations obtained for the quantity of power electronic switches employed and number of levels is

$$N_L = 2V_{ndc} + 1 \tag{1}$$

$$S_{N} = 2(V_{ndc} + 1) \tag{2}$$

Where  $N_L$ = number of levels

$S_N = number of$

switches

$V_{ndc}$  = number of DC voltage sources

From equations (1) and (2),

$$S_N = N_L + 1 \tag{3}$$

The switching pattern for 15 level cross H bridge multilevel inverter of figure (2) is shown in table (1). With this topology the total harmonic (THD) distortion is enhanced for the same level contrast to other topologies.

Table-I: Switching sequence of 15 level cross H bridge multilevel(ML) inverter

| S.No. | Output Voltage    | On Switches                            |  |

|-------|-------------------|----------------------------------------|--|

| 1     | 0                 | S1S3S5S7S9S11S13S15                    |  |

| 2     | $V_{ m dc}$       | S2S3S6S7S10S11S14S15                   |  |

| 3     | $2v_{dc}$         | $S_2S_3S_5S_8S_9S_{12}S_{13}S_{16}$    |  |

| 4     | 3v <sub>dc</sub>  | S2S3S5S7S10S11S14S15                   |  |

| 5     | $4v_{dc}$         | S2S3S5S7S9S12S13S16                    |  |

| 6     | 5v <sub>dc</sub>  | S2S3S5S7S9S11S14S15                    |  |

| 7     | 6Vdc              | S2S3S5S7S9S11S13S16                    |  |

| 8     | $7v_{dc}$         | S2S3S5S7S9S11S13S15                    |  |

| 9     | -Vdc              | S1S4S5S8S9S12S13S16                    |  |

| 10    | -2vdc             | S1S4S6S7S10S11S14S15                   |  |

| 11    | -3vdc             | S1S4S6S8S9S12S13S16                    |  |

| 12    | -4v <sub>dc</sub> | S1S4S6S8S10S11S14S15                   |  |

| 13    | -5Vdc             | S1S4S6S8S10S12S13S16                   |  |

| 14    | -6Vdc             | $S_1S_4S_6S_8S_{10}S_{12}S_{14}S_{15}$ |  |

| 15    | -7v <sub>dc</sub> | S1S4S6S8S10S12S14S16                   |  |

Fig.2. 15 level cross H bridge MLI (Single phase)

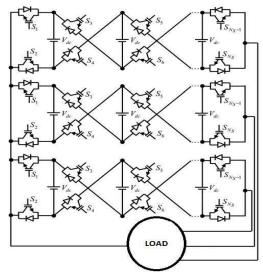

Fig.3. Three phase cross H bridge multilevel(ML) inverter

Retrieval Number: J92950881019/19©BEIESP DOI: 10.35940/ijitee.J9295.0981119 Journal Website: www.ijitee.org Figure (3) shows cross 'H' bridge multilevel(ML) inverter three phase circuit. The pattern of switching for three phase resembles as single phase but number of switches turned on for particular level will change.

## III. MATHEMATICAL CALCULATIONS

The computation of multilevel(ML) inverter output voltage from Fourier series

$$V(t) = \frac{a_0}{2} + \sum_{n=1}^{\infty} (a_n \cos nwt + b_n \sin nwt)$$

(4)

There is a existence of quarter- wave symmetry through the x-axis. So, both coefficients  $a_0$  and  $a_n$  become zero. Assume the symmetry across the y axis at  $\omega = \pi/6$ , and  $b_n$  is defined as

$$b_n = \frac{1}{\pi} \left[ \int_0^{\pi} (V_{dc}) \sin \omega t \, dwt \right]$$

(5)

The output voltage equation obtained after successive calculations is

$$V(t) = \frac{4V}{\pi} \sum_{n=1}^{\infty} [\cos n\theta_1 + \cos n\theta_2 + \cos n\theta_3]$$

$$+\cos n\theta_4 + \cos n\theta_5 + \cos n\theta_6 + \cos n\theta_7 ]\sin n\omega t$$

(6)

Switching angles of MLI can be attained by procuring Nonlinear equations from the selective harmonic elimination process[10]. From this method we can eliminate any selected harmonic from waveform. For 15 level cross MLI with 5<sup>th</sup>, 7th, 11th, 13th, 17th and 19<sup>th</sup> harmonic elimination the following equations cam be formulated.

The mathematical equations obtained to compute conduction angles are

$$Cos \theta_1 + Cos \theta_2 + Cos \theta_3 + Cos \theta_4 + Cos \theta_5 + Cos \theta_6 + Cos \theta_7$$

$$= 7m$$

$$\begin{array}{l} Cos\ 5\theta_1 +\ Cos\ 5\theta_2 +\ Cos\ 5\theta_3 +\ Cos\ 5\theta_4 +\ Cos\ 5\theta_5 +\ Cos\ 5\theta_6 \\ +\ Cos\ 5\theta_{7} =\ 0 \end{array}$$

$$Cos 7\theta_1 + Cos 7\theta_2 + Cos 7\theta_3 + Cos 7\theta_4 + Cos 7\theta_5 + Cos 7\theta_6 + Cos 7\theta_7 = 0$$

Cos

$$11\theta_1$$

+ Cos  $11\theta_2$ + Cos  $11\theta_3$ + Cos  $11\theta_4$ + Cos  $11\theta_5$ + Cos  $11\theta_6$ + Cos  $11\theta_7$ = 0

Cos

$$13\theta_1$$

+ Cos  $13\theta_2$ + Cos  $13\theta_3$ + Cos  $13\theta_4$ + Cos  $13\theta_5$ + Cos  $13\theta_6$ + Cos  $13\theta_7$ = 0

Cos

$$19\theta_1$$

+ Cos  $19\theta_2$ + Cos  $19\theta_3$ + Cos  $19\theta_4$ + Cos  $19\theta_5$ + Cos  $19\theta_6$ + Cos  $19\theta_7$ = 0

In the above equation (7), the number seven which is at the right side of the first equation indicates magnitude of Fourier series fundamental component and 'm' specifies the modulation index. Conduction angles can be procured by iterating repeatedly with Newton (NR) Raphson method. The achieved conduction angles are

$$\theta_1 = 7.16, \ \theta_1 = 17.02, \ \theta_1 = 25.74, \ \theta_1 = 39.93, \ \theta_1 = 52.36$$

$\theta_1 = 58.28, \ \theta_1 = 67.30$

The THD output can be obtained from the below mentioned equation

$$%THD = \frac{\sqrt{\sum_{n=5,7,11...}^{\infty} v_n^2}}{v_n} \times 100$$

(9)

# IV. SPWM TECHNIQUE

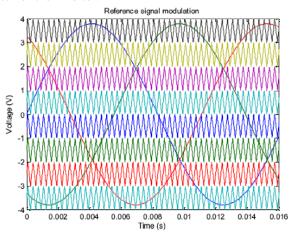

In sinusoidal PWM technique we will compare carrier wave triangular signal with sine signal. The gate pulses for switches are generated with comparator with comparison between two t reference and carrier signals. Multicarrier sine PWM used in this paper and figure (4) signify the modulating signals for nine level. For nine level inverters there will be eight carrier signals with four positive and four negative with respect to magnitude. The positive carrier signals compared with positive part and negative signals with negative part. The width of gating signals for inverter can be managed by controlling the magnitude of sine wave[11]-[12].

The crossing positions determine the changing switching times between states. In three phase, voltages  $V_a$ ,  $V_b$ , and  $V_c$ are phase displaced by 120 degrees with respect to each other is compared with a carrier triangular voltage waveform originates the gating signal for each phase and for relative switch of the inverter.

Fig.4. Modulating signals of nine level SPWM

# V. SIMULATION RESULTS

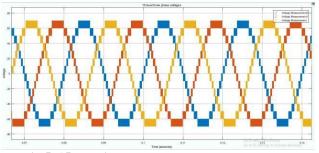

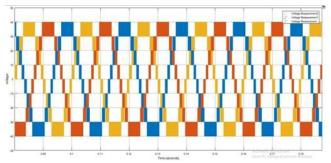

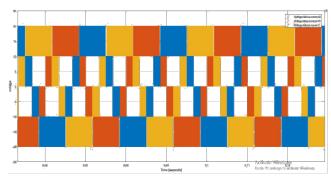

The simulations of cross H bridge multilevel inverter were performed in MATLAB/SIMULINK domain. Figure (1) shows schematic diagram of presented topology and the combination used in the simulation and experimental results are mentioned in table (1). But one can select the switching combinations that reduce the number of switching transitions. As shown in the table (1), for zero voltage level two switching pattern combination can be used. Select the switching combination where minimum switching transitions takes place to change from one (10) voltage level to next (20) voltage level. Figures (4),(5)&(6) shows the three phase output voltages of 5,9 and 15 level multilevel inverter.

Fig.5. 15 level inverter three phase output voltages

Fig.6. 9 level inverter three phase output voltages

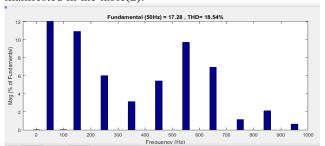

Fig.7. 5 level inverter three phase output voltages Figures (5), (6) and (7) shows output voltages of 15,9,5 level multilevel inverter. And the obtained distinct THD values are manifested in the table(2).

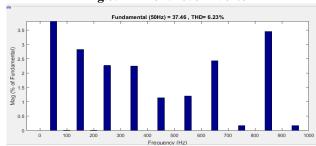

Fig.8. THD of 5 level inverter

Fig.9. THD of 9 level inverter

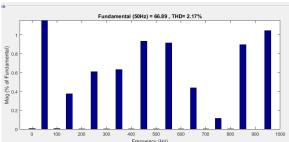

Figures (8), (9) and (10) show the THD of 5, 9 and 15 level inverters. There is decrease in THD with increasing levels with fewer switches.

Fig.10. THD of 15 level inverter

Table (2): THD of 5, 9 and 15 multilevel inverter

| S.no | Number   |       | THD          | THD          |

|------|----------|-------|--------------|--------------|

|      | of       | Level | (simulation) | (calculated) |

|      | switches |       |              |              |

| 1    | 6        | 5     |              | 20.34%       |

|      |          |       | 18.54%       |              |

| 2    | 10       | 9     | 6.23%        | 9.23%        |

| 3    | 16       | 15    | 2.17%        | 5.69%        |

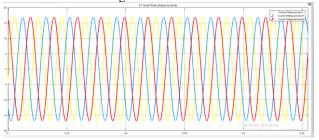

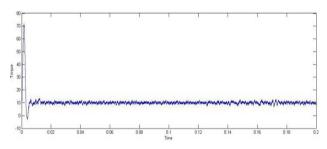

The three phase currents, speed and toque of PMSM are shown in the below figures.

Fig.11. Three phase output currents

Fig.12. Torque of PMSM

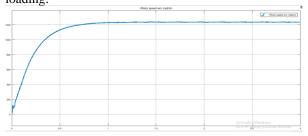

Figures (11) and (12) show three-phase output current and torque of PMSM. The stability of PMSM is verified by loading.

Fig.13. Speed of PMSM

Fig (13) shows the speed of PMSM and stabilty is verified with load.

Retrieval Number: J92950881019/19©BEIESP DOI: 10.35940/ijitee.J9295.0981119 Journal Website: www.ijitee.org

### VI. CONCLUSION

This paper presents a topology which uses reduced quantity of power electronic switches, number of voltage sources and does not use high voltage switches unlike other typical MLI topologies. This topology lessens the cost, switching losses and increases output efficiency. For 15 level MLI this topology requires 16 number of switches i.e., for 'n' level inverter it requires 'n+1' switches. The Stability of PMSM is validated with different loading points.

### REFERENCES

- 1. Patil Swapnil Sanjay, Patil Rupali Anaji, Patil S.K, "Symmetrical Multilevel Cascaded H Bridge Inverter Using Multicarrier SPWM Technique," 2018, 3rd International Conference for Convergence Technology.

- J. Srinivas Rao, P. Srinivasa Varma, T. Suresh Kumar, "Novel Switching Design Structure for Three Phase 21-Level Multilevel Inverter Fed BLDC Drive Application", International Journal of Power Electronics and Drive System, Vol. 9, No. 3, Sept 2018, pp. 1202~1213, ISSN: 2088-8694, DOI: 10.11591/ijpeds.v9n3.pp1202-1213

- Nikhil Agarwal, Praveen Bhansal "A new 21 level asymmetric multilevel inverter with different PWM techniques," RDCAPE, 2017

- B. Phani Teja, V. Srikanth Babu, T. Suresh Kumar. "Modelling of Static VAR Compensator employing a cascaded H-Bridged Multilevel Converter" International Journal of Applied Engineering Research, Vol. 10, No. 16, 2015, pp: 37057-37062.

- C Dhanamjayalu, S Meikandasivam "Performance of Symmetric Hybridized Cascaded multilevel(ML) inverter with reduced number of switches "I-PACT, 2017.

- S.Satish Kumar, M.sasikumar " An approach of hybrid modulation in fusion seven-level cascaded multilevel inverter accomplishment to IM drive system" ICONSEM, 2016.

- Basem Alamri, Saeed Alsharani, Mohamed Darwish "Losses Investigation in SPWM controlled cascaded H bridge Multilevel inverters" UPEC, 2015.

- Purnima Purohit, Menka Dubey, "Analysis and Design of Hysteresis Current and Industrial Applications of Multilevel Inverter fed PMSM drive"978-1-4799-2526-1/14,2014 IEEE.

- Mohammad Farhadi Kangarlu, Ebrahim Babaei "Cross-switched Multilevel(ML) Inverter: an Innovative Topology," IET Power Electro.,

- 10. Mohammad Farhadi Kangarlu, Ebrahim Babaei, Mehran Sarabhi "Cascaded Cross-switched Multilevel Inverter in Asymmetric and Symmetric conditions" IET Power Electro., 2013

- T.Tarezewski, L.M.Grzesiale "PMSM fed by 3-level NPC Sinusodial Inverter With Discrete State Feedback Controllers" EPE, 2013

- 12. Carlos Alberto, Lozano Espinosa, IEEE member, Porocarrero, and Mauricio Izquierdo "Minimization of THD and Angle Calculation for Multilvel Inverters" 1211905-9282-IJET, October 2012 IJWNS.

- 13. Kouro, S.Malinowski, M.Gopakumar.,et al: "Recent Advances and Industrial Applications of Multilevel Converters." IEEE Trans.,Ind .Electron.,2010,57,(8),pp.2533-2580

- 14. S.Thelemans, F.De Belie and J.mclkebeek, "A Sensorless PMSM Drive Using Test Signals Generated by a Multilevel Inverters" in proc. ICEMS Conf., Nov. 2009, pp. 1-6.

## **AUTHORS PROFILE**

B. Yogeswara Reddy received B.Tech degree from Sir Vishveshwaraiah Institute of Science and Technology in Electrical and Electronics Engineering. He is right now Pursuing M.Tech degree from Gokaraju Rangaraju Institute of Engineering and Technology in power Electronics. His subject of interest is Power Electronics

and Drives(PED).

Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) 1197 © Copyright: All rights reserved.

J. Srinivas Rao received his Bachelor's and Master's degree in Electrical & Electronics Engineering from Jawaharlal Nehru Technological University, Hyd. in 2003 and 2008 respectively. Presently he is a research scholar at KLEF, Vaddeswaram, Guntur, Andhra Pradesh, India and working as an Assistant professor at Anurag Engineering

College, Suryapet, Telangana, India. His areas of interests include Power Electronics, Drives and Electrical Machines.

**Dr. T. Suresh Kumar** received his Doctorate degree (Ph.D.) in Electrical Engineering from JNTU, Anantapur. Presently working as Professor, EEE Department, Gokaraju Rangaraju Institute of Engineering and Technology, Hyderabad. His areas of interest are Power Electronics(PE), Power System(PS), Reliability and

(AI)Artificial Intelligence. He is also senior member of different professional societies like IEEE,IAENG,ISEEE,ISES,ISTE and EDAS.

A. Nagarjuna, received B.Tech degree from Madhira Institute of Technology and Sciences in EEE stream, kodad. Currently he is a PG scholar at Gokaraju Rangaraju Institute of Engineering and Technology in power Electronics. His field of interest is Power Electronics.

Retrieval Number: J92950881019/19©BEIESP DOI: 10.35940/ijitee.J9295.0981119 Journal Website: www.ijitee.org