# Telescopic Ota Based Cmos Design of High Gain, High Cmrr, Larger Bandwidth Instrumentation Amplifier

### Arvind Singh Rawat, Arti Rana, Jagadheswaran Rajendran

Abstract: Instrumentation amplifiers (IA) play a crucial role wherever small differential voltages need to be amplified precisely in the occurrence of a any voltage at the input. It must therefore attribute high input-impedance, small input-referred noise and offset voltage, large differential-voltage gain without feedback and significantly cast-off deviations on power-supply and common mode voltages. In this paper efficient instrumentation amplifier with high gain, high CMRR and larger bandwidth is implemented. The proposed differential amplifier may be used for various control systems as well as small signal conditioning circuits; instrumentation amplifier having larger product of gain and bandwidth would encounter maximum application in these desires.

Keywords: CMRR, Telescopic OTA, GBW.

### I. INTRODUCTION

Instrumentation amplifiers, usually known as differential amplifier are significant blocks which are used for signal in many instrumentation Instrumentation Amplifier van be design with Op-amp, differential difference amplifier (DDA), Constant Current draw amplifier (CCDA), operational transconductance amplifier (OTA) [3]. Basically instrumentation amplifier (IA) is a class of differential amplifier which is set with the input buffer amplifiers, which get rid of the require matching of I/P impedance and therefore design amplifier predominantly appropriate for application in measurement in the control system. Additional description consist of, reduced noise, large open-loop gain, small DC offset, low drift, high common-mode rejection ratio and large input impedances.[6

### A. Instrumentation amplifier Vs Op-amp

In comparison with an op amp, an instrumentation amplifier is a closed-loop amplifier with single ended respect to the reference terminal and having differential I/P and O/P. Generally, impedances seen in 2 – terminals of the instrumentation amplifier are very high on average,  $10^9\Omega$ , or larger. Consequently, for high input impedance, the input biasing current must be very low and in the range of average 1 nA to 50 nA. The output impedance of op- amp is usually very low which is practically,

### Manuscript published on 30 September 2019.

\*Correspondence Author(s)

**Arvind Singh Rawat,** Assistant Professor Department of Electronics & Communication Engineering, Uttaranchal University, Dehradun.

Arti Rana, Assistant Professor Department of Computer Science & Engineering, Uttaranchal University, Dehradun

**Jagadheswaran Rajendran**, Senior Lecturer with Collaborative Microelectronic Design Excellence Centre (CEDEC) and School of Electrical and Electronic Engineering, Universiti Sains Malaysia

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license <a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>

in few milliohms if the frequencies are low. When comparison is done between the two, the op-amp require a an external resistance in its feedback path for the calculation of closed loop gain whereas in an instrumentation amplifier a network of internal feedback resistance is connected. [1]

### B. Signal Amplification and Common-Mode Rejection

It is the virtue of an instrumentation amplifier that it amplifies the difference between the two signals given at its input and along with amplification it tries to nullify the common signal between them. The common signal between the two input terminals is rejected by the amplifier and it is very important characteristic of an IA. The instrumentation amplifiers can boost the weak signal coming from any transducer or any other sources. Common-mode rejection Ratio (CMRR), the quality of cancelling the common signal between the two differential input and it plays a crucial role while analyzing the response of the instrumentation amplifier. CMRR is quite important specification of IA for both DC & AC signals. A good quality instrumentation amplifier can shortened any error due to dc common mode voltage 80dB to 120dB. Today's IA have outstanding CMRR for both dc & ac input signals.

Mathematically, common-mode rejection of differential amplifier can be calculated as:

$$CMRR = 20 \text{ Log } \frac{A_d}{A_c}$$

Where  $A_d$  is the differential gain;  $A_c$  is the common-mode gain of amplifier. [1]

## II. CHARACTERISTICS OF HIGH QUALITY INSTRUMENTATION AMPLIFIER

For larger common mode rejection ratio, an instrumentation amplifier needs the following properties:

- 1. High AC as well as DC Common-Mode Rejection(CMRR)

- 2. Low Offset Voltage and Offset Voltage Drift

- 3. Low Noise

- 4. Low Nonlinearity

- 5. Adequate Bandwidth

### Telescopic Ota Based Cmos Design of High Gain, High Cmrr, Larger Bandwidth Instrumentation Amplifier

### III. DESIGN OF OTA BASED INSTRUMENTATION AMPLIFIER

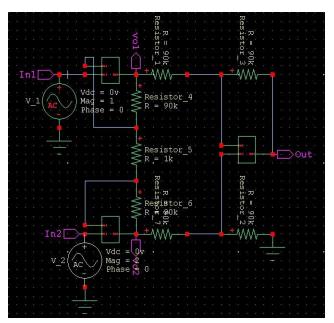

In this project work instrumentation amplifier is designed which is based on telescopic operational transconductance amplifier. As we know that amplifier is an essential building block in any system. The schematic of OTA based Instrumentation Amplifier is shown below:

Fig.1 Schematic of OTA based Instrumentation

Amplifier

# A. Gain and CMRR calculations of designed Instrumentation Amplifier

Taking,

$$R_1$$

=  $R_3$  =  $R_4$  =  $R_5$  =  $R_6$  =  $R_7$  = 90 K $\Omega$ ,  $R_2$  = 1 K $\Omega$

From Equation (2.19) output voltage of first Non-inverting OTA can be calculated as:

$$V_{OI} = \frac{g_m(R_1 + R_2)}{1 + g_m R_2} .Vi$$

(1)

Where

$$g_m = 7.505 \text{ mS}$$

Putting the values of  $R_1$ ,  $R_3$ ,  $R_4$ ,  $R_5$ ,  $R_6$ ,  $R_7$ ,  $R_2$  &  $g_m$  in equation (4.1)

$$V_{01} = 89.80 \text{ V}$$

Similarly,

$$V_{O2} = 179.60 \text{ V}$$

Now,

$$V_{O} = \frac{(1 - g_{m}R_{6})}{(1 + g_{m}R_{4})}. V_{O1} + \frac{V_{O2}.R_{7}}{R_{5} + R_{7}}. \frac{g_{m}(R_{4} + R_{6})}{1 + g_{m}R_{4}}$$

(2)

Putting the values we get:

$$V_0 = 89.8 \text{ V}$$

Retrieval Number: K17470981119/19©BEIESP DOI: 10.35940/ijitee.K1747.0981119 Journal Website: <u>www.ijitee.org</u>

Gain (dB) =

$$20 \operatorname{Log} \frac{Vo}{V_i}$$

(3)

### **Common Mode Rejection ratio:**

Common Mode rejection Ratio is the capability of Differential amplifier to nullify the output when both the inputs are equal. In designed instrumentation Amplifier CMRR can be calculated as follows:

$$CMRR = 20 \operatorname{Log} \frac{A_d}{A_c}$$

(4)

### IV. SIMULATION RESULTS

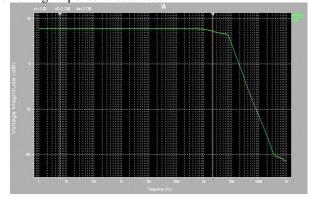

On simulating the circuit designed above on Tanner Spice following response is obtained:

Fig.2 Response of OTA based Instrumentation Amplifier designed in fig.1

### V. ANALYSIS OF SIMULATION RESULTS

It can clearly be observed from response shown in fig no.2 that differential gain of Instrumentation Amplifier designed in fig. no. 1, is 39.30dB which is almost equals to as calculated mathematically by equation (3)

### Gain= 39.30

And CMRR of designed amplifier is observed as 97 dB which is almost equals to as calculated mathematically by equation (4).

Since;

$A_d$ = differential gain =92.30;

$A_c = \text{common mode gain} = 0.00131$

Putting these values in Equation (4) we get

### CMRR = 96.72 dB

Bandwidth of designed Instrumentation Amplifier is observed as 2.13MHz

### VI. CONCLUSION

For any instrumentation amplifier it is necessary that it has lowest offset. Regardless of offset voltages, the specific concern of this paper is to improve gain, bandwidth, CMRR and gain bandwidth product.

For schematic design of instrumentation amplifier 13.0 version of Tanner EDA is used and all the values are verified mathematically.

Published By:

Blue Eyes Intelligence Engineering

and Sciences Publication (BEIESP)

710 © Copyright: All rights reserved.

#### REFERENCES

- A. Bakker, K.Thiele and J. H. Huijsing, "A CMOS Nested-Chopper Instrumentation Amplifier with 100-nV Offset", IEEE Journal of Solid-State Circuits, vol. 35, December, 2000.

- A. Veeravalli, E. Sanchez-Sinencio, and J. Silva-Martinez, "Transconductance amplifier structures with very small transconductances: A comparative design approach," IEEE J. Solid-State Circuits, vol. 37, no. 6, pp. 770–775, Jun. 2002.

- C. Kitchin, L Counts, "A Designer's guide of Instrumentation Amplifier", USA, Ana log Devices, Inc (2002).

- Anil Kavala, Kondekar P. N, and Yang Sun, "A low voltage, low power linear pseudo Differential OTA for ultra-high frequency applications", IEEE, International workshop on Antenna Technology, 2009

- Chunbiao Wu, Meng Zhang, Jianhui Wu, Zhenchang Du, "Design of A Gain-Boosted OTA for High-Speed and Low-Voltage Applications," Electronic Technology, 2009.

- Milad Razzaghpour & Abbas Golmakani, "An ultra-low-voltage ultra-low-power OTA with Improved gain-bandwidth product", IEEE International Conference on microelectronics, 2008.

- Neha Gupta, Meenakshi Suthar, Sapna Singh, Priyanka Soni "Active Filter Design Using Two OTA based Floating Inductance Simulator" International Journal of VLSI & Signal Processing Applications, Vol.2, Issue 1, Feb 2012.

- Saksit Summart, Chanchai Thongsopa, Winai Jaikla "OTA Based Current-mode Sinusoidal Quadrature Oscillator with Non-interactive Control", PRZEGLĄD ELEKTROTECHNICZNY (Electrical Review), ISSN 0033-2097, R. 88 NR 7a/2012.

- Deyasini Majumdar, "Comparative Study of Low Voltage OTA Designs", vlsid, pp.47, 17th International Conference on VLSI Design, 2004

- E.S.Sinencio and J.S.Martinez, "CMOS transconductance amplifiers, architectures and active filters: a tutorial", IEEE Proc.-Circuits Devices System, vol. 147, no. 1, February 2000.

### **AUTHORS PROFILE**

Arvind Singh Rawat received his B.Tech degree in Instrumentation Engineering from USIC, HNB Garhwal University (Central University) in 2009. He received his M.Tech (Hons) degree in VLSI Design from Faculty of Technology, Uttarakhand Technical University in 2013.

From 2013, he is working as Assistant Professor in the Department of Electronics & Communication

Engineering, Uttaranchal University, Dehradun. He has published many research articles in reputed international journals in the field of microelectronics & VLSI Design. His research interests include VLSI, Analog Integrated Circuit, Microelectronics.

Arti Rana is working as Assistant Professor In the Department of Computer Science & Engineering, Uttaranchal University, Dehradun. She has published many research articles in the reputed journals. She received the B.Tech (Hons) degree in Information Technology from Uttarakhand Technical University. She received the M.Tech (Hons) degree in Computer Science & Engineering from Uttarakhand Technical University. Her

research interests include Artificial Intelligence, Data mining, Cryptography and Network Security.

Jagadheswaran Rajendran received the B.Eng (Hons) degree in electronic engineering from Universiti Sains Malaysia in 2004, M.Eng degree in telecommunication engineering from Multimedia University, Malaysia in 2010 and Ph.D. degree in microelectronic engineering from University of Malaya in 2015.

From 2004 to 2005, he was with Laird

Technologies as an antenna designer followed by serving Motorola Technology. From 2005 to 2007 as RnD engineer, working on mobile phone receiver system. In 2008, he joined Broadcom as MMIC designer, working mainly on GaAs based Power Amplifier, LNA and gain blocks, where he was elevated to the rank of principal engineer later. In 2015, he joined Silterra Malaysia, working on CMOS RFIC Design and device modelling. Since 2016, he has been a Senior Lecturer with Collaborative

Retrieval Number: K17470981119/19©BEIESP DOI: 10.35940/ijitee.K1747.0981119 Journal Website: www.ijitee.org Microelectronic Design Excellence Centre (CEDEC) and School of Electrical and Electronic Engineering, Universiti Sains Malaysia. He is a co-author of one book, more than 30 articles and hold one US patent. His research interests include CMOS Analog IC Design, CMOS Radio Frequency (RF) IC Design and Monolithic Microwave Integrated Circuit (MMIC) Design.

Dr. Jagadheswaran was the recipient of the IEEE Circuit and System Outstanding Doctoral Dissertation Award in 2015. He served as the chairman of IEEE EDS/MTT/SSC Penang Chapter in 2011 and 2018. He is also a Senior Member of IEEE. This work was supported by CEDEC Universiti Sains Malaysia under Grant RUI 1001/PCEDEC/8014079 and Short Term, Grant 304/PCEDEC/6315056