# CSHM Multiplier and Radix-256 Algorithm using Fir Filter Design

# Anusha B, B.Annapurna, Arulananth T S, T.Nagarjuna

Abstract— The Rredundant Binary (RB) systems are wellliked for the reason that of its distinctive carry broadcast free addition. Thus a specific filter called as Finite Impulse Response filter computes its yield exploitation multiply& accumulation process. At intervals the reward work, a FIR filter supported to higher radix-256 and chemical element arithmetic is implemented. The employment of radix-256 booth secret writing cut down the amount of partial product rows in any multiplication by eight fold. Present work inputs and coefficients unit of measurement thought-about of 16-bit. Hence, entirely two partial product rows unit of quantity obtained in Redundant Binary (RB) kind for both input and constant multiplications. These two partial product rows unit measurement added exploitation carry free element addition. The final output is converted back to Natural Binary (NB). The planned number technique for FIR filter is compared with Computation Sharing Multiplier (CSHM) implementation.

Keywords— Redundant Binary, Computation Sharing Multiplier, Finite Impulse Response, FPGAs, ASICs.

#### I. INTRODUCTION

Thus the DSP functions are implemented recently using victimization Field Programmable Gate Arrays. Whereas Application Specific Integrated Circuits (ASICs) area quality answer to far above the ground of applications, thus the high development costs and delay of marketing factors compel the preparation of such solutions for certain cases. Filter structures that area unit widely utilized in purpose like vocalizations, picture & video scheme and communications to decision variety of area of unit unremarkably enforced victimization FPGAs.

# II. OBJECTIVES OF THIS WORK

Advanced FIR channels unit of estimation same to be limited as a consequences of they're doing not have any input. Accordingly, on the off chance that you send relate motivation through the framework, the yield will constantly end up zero when an after effect of the drive goes through the channel. Once VLSI idea is applied in DSP application then its main goal is to cut back 3 constraints these square

Revised Manuscript Received on September 10, 2019.

**Anusha B,** Assistant Professor, Department of Electronics and Communication Engineering, MLR Institute of Technology, Hyderabad-43, Telangana, India.

(E-mail: anusha.badepalli@gmail.com)

**B.Annapurna,** Assistant Professor , Department of Electronics and Communication Engineering, MLR Institute of Technology, Hyderabad, India.

**Arulananth T S,** Professor, Department of Electronics and Communication Engineering, MLR Institute of Technology, Hyderabad-43, Telangana, India.

(E-mail: arulanandh.ts@gmail.com)

**T.Nagarjuna,** Assistant professor, Department of Electronics and Communication Engineering, Institute of Aeronautical Engineering, Hyderabad, India.

measure power consumption of circuit, space of circuit becomes less and speed become high.

# III. MOTIVATION OF THIS WORK

Multiplication is a kev operation and multiplier factor plays a crucial role digital in signal process. Sadly, the most important supply of power dissipation in digital signal processors is multipliers. Within the previous decade specialists created multipliers with the help of CMOS rationale that has every one of the detriments as referenced before. The planning of multipliers for digital signal processing claim ought to be economical whereas motionless having the ability to knob low-power purpose.

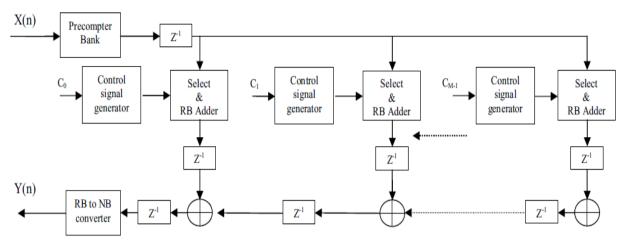

# IV. COMPUTATIONAL SHARING MULTIPLIER

The Computational Sharing Multiplier (CSHM) style & execution, that depends on the formula is given. It made of recomputed Select Units& Adders unit (S&A). Thus the precomputer produce the multiplication of alphabets with input 'x' and thus the Select & Add unit execute the addition and shift operations necessary to induce the last word yield. The prime benefit of this algorithm is that the productivity of pre-computer unit of measurement mutual by all the select units. Therefore, that process is carry out by choose units are usually dead in parallel whereas not introducing any choose unit delay.

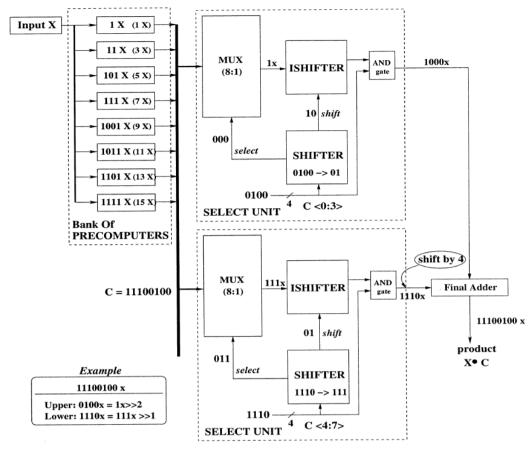

Figure 1: Computation Sharing Multiplier (CSHM) architecture

# V. OPERATION OF CSHM ARCHITECTURE

CSHM design relies on the formula explained in Figure:1 shows the CSHM design. CSHM made up of a precomputer; choose component and last adders (S&A). The pre-PC plays out the increase of letter sets with info. Since letters in order square measure modest piece successions, the increase with info X and letters in order are regularly maintained a strategic distance from truly bargaining the execution. S&A execute suitable select/shift and addition operations required to induce the multiplication response. The select unit made up of MUX (8:1), SHIFTER, AND gate and ISHIFTER to go looking out the right alphabet and SHIFTERs perform the right shift operation awaiting they encounter one AND send a suitable select signal to MUX (8:1). SHIFTERs put together send the precise shifted values (shift signal) to ISHIFTERs. The MUX (8:1) select the right answer among the eight pre-computer outputs, ISHIFTERs just inverse the operation performed by SHIFTERs. Once the constant input is 0000, we have a tendency to tend to cannot get a zero output with shifted value of the pre-computer outputs. A simple AND gates unit of measurement accustomed trot out the zero (0000)stable enter. The last word adder the select units output to induce the last 16 bit multiplication give up. The digital FIR filter style depends on a CSHM that purposely deed addition and shifting process and put together objective computation use again in vector-scalar products.

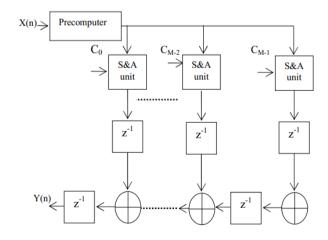

5.1 CSHM in FIR Filter Design

FIR filter design depends on computation sharing multiplier that particularly performing addition and shifting process and together targets computation re-use in vector and scalar operation. A convolution operation is known by

$$Y(n) = \sum_{k=0}^{M-1} C_k X(n-k)$$

(1)

Where, "Ck" is the coefficients of the filter and X (n-k) is delayed Input by "k" units.

Figure: 2 CSHM Algorithm used for FIR Filter

#### 5.2 Process to obtain C\*X

Initially the constant is split into cluster of little bit series and name as an alphabet. The multiplication of the input with the every alphabet is gain by choosing from the outputs of a pre-computer therefore shifting is required. In conclusion a multiplication result of a relentless with input is obtained by adding the alphabet multiplication results with required shifting.

For explaining the use of CSHM method, consider a 16-bit constant  $C0 = 1010 \ 1101 \ 1011 \ 0110$  are usually divided as follows.

a3=1010, a2=1101, a1=1011 and a0 = 0110. Then the output C\*X = 212(a3\*X) + 28(a2\*X) + 24(a1\*X) + (a0\*X)

An element adder has a distinctive feature of carry broadcast free addition. First the two DMPP's gained in element kind. The selector unit results added with victimization adder and barred within register units. Second, the multiplication results of one faucet purpose and therefore the previous faucet purpose square measure value-added victimisation metallic element adders.

#### VI. RADIX-256 MULTIPLIER & RESULTS

This algorithm reduces the number of partial product rows 8 fold time by any multiplication. At intervals, the experimental effort inputs & coefficients are sixteen bit size. product Therefore, 2 rows unit obtained partial in element kind for each input and constant multiplications. product Partial chain unit added exploitation carries free element addition. At last the element yield binary is changed rear to natural device. kind exploitation element to NB

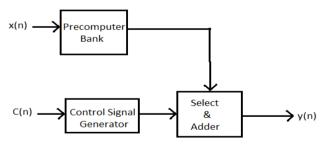

Figure: 3 Radix-256 multiplier

# 6.1. Radix-256 multiplier algorithm

Control signal generator generates the correct S-DIGIT, T-DIGIT victimisation formula. The subsequent is that the formula to search out the basic T-group and S-group digits to represent a digit Di. Suppose the Digit D0 is created by lower eight bits of constant AND an overlapping bit C7C6C5C4C3C2C1C0C-1.

Thus the digit measures the ultimate digits S - group = 4\*C2+2\*C1+1\*C0+1\*C-1 T- group = 16\*(4\*C6+2\*C5+1\*C4+1\*C3)

6.2 A sample Multiplication using radix-256

here inputs square measure X and Y,

Where

Y=4302=0001000011001110.

This constant are often sorted into four digits with

D0= -50, D1= 2,

then

$$Y = \text{twenty eight. D1+ D0}$$

and

$Y.X = 28.(\text{D1.X}) + (\text{D0.X})$

This SGDMPP are often gained by shifting X 1-bit position. Equally the TGDMPP are often obtained by shifting -3X by 4 bit position. Likewise D1.X to be able to attained with X SGDMPP with X TGDMPP.

This SGDMPP are often obtained by taking X worth from pre-computer. Equally the TGDMPP are repeatedly obtained by taking X value from pre-computer. Ultimately the bits D0.X and D1.X are shifted 8-bit location.

# 6.3 Redundant Binary Adder

The addition operation altogether RBs is carry-free, which implies that the carry doesn't have to be compelled to propagate through all the dimension of the addition unit. In effect, the addition altogether RBs may be a constant-time operation. The addition can continually take an equivalent quantity of your time freelance of the bit dimension of the operands.

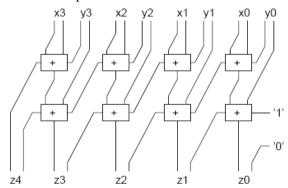

Figure: 4 Redundant Binary Adders

In metallic element Adder every binary bit represents 2 bits in metallic element.'0' is painted as "00" and '1' is painted as "10". These reborn values given to the complete adders during this adder 2 cluster of Full adders needed. first cluster full adder inputs is metallic element numbers and output total and carry is given to the ordinal cluster full adder inputs the carry is propagate to next stage full adders in ordinal cluster full adder, the ordinal stage full adder output is ours final output.

### 6.4 FIR Filter design supported by NPGHB

In this experimental job, a singular partial product generation radix-256 booth coding is utilized. Make help of this new concept partial product string is reduced remarkably. The addition of T- group& S-groups is used to generate the partial product rows every times.

Figure: 5 FIR filter design using RB Adder and NPGHP

The distinctive characteristic of a RB adder carry propagation free addition has achieved. Rubidium adders are utilized in 2 places of FIR filter design.

# VII. CONCLUSION

FIR filter design supported by **NPGHB** & metal calculation is intended. In every multiplication, the partial product rows are reduced by radix-256 algorithm is 8 fold times. Like, the multiplication of 16-bit input results completely a pair of partial product rows. Thus the gained partial merchandise in metal kind unit added mistreatment metal adder, that's way faster than other propagation. Thus the planned multiplication technique supported NPGHRB for designing the FIR filter is faster additional or less by forty second as compared to CSHM implementation, however with zero.5% and eleventh increase in area and power severally.

# VIII. REFERENCES

- Y. C. Lim, S. R. Parker, and A. G. Constantinides, "Finite word length FIR filter design using integer programming over a discrete coefficient space," Aug. 1982.

- Y. C. Lim and S. R. Parker, "FIR filter design over a discrete power-of two coefficient space," IEEE Trans. Acoustics, Speech Signal Processing, June 1983.

- H. Samueli, "An improved search algorithm for the design of multiplier less FIR filter with powers-of-two coefficients," July 1989.

- Hai Huyen Dam, Cantoni A., Kok Lay Teo, Nordholm S., "FIR Variable Digital Filter With Signed Power-of-Two Coefficients," June 2007.

- Mustafa Aktan, Arda Yurdakul, and Günhan Dündar. "An Algorithm for the Design of Low-Power Hardware-Efficient FIR Filters," JULY 2008.

- Vinod A.P., Singla A., Chang C.H., "Low-power differential coefficients-based FIR filters using hardwareoptimised multipliers, "February 2007.

Dong Shi, Ya Jun Yu, "Design of Discrete-Valued Linear

- Phase FIR Filters in Cascade Form," July 2011.

- Jongsun Park, Woopyo Jeong, Hamid Mahmoodi-Meimand, Yongtao Wang, Hunsoo Choo, Kaushik Roy., Computation sharing programmable fir filter for lowpower and high- performance applications.

- Hiroshi Makino, Yasunobu Nakase, Hiroaki Suzuki, Hiroyuki Morinaka, Hirofumi Shinohara, and Koichiro Mashiko, "An 8.8-ns 54 x 54-Bit multiplier with high speed redundant binary architecture," June 1996.

- 10. N. Takagi, H. Yasura and S.Yajima., "High-speed VLSI multiplication algorithm with a redundant binary addition tree" Sept.1985.

- Yum Kim, Bang-Sup Song, John Grosspietsch, and Steven F. Gilling, "A carry-free 54b x 54b multiplier using equivalent bit conversion algorithm, "Oct. 2001.