# SEU Performance Enhancement in BPJLT Devices by Channel Doping and Film Thickness

# N. Vinodhkumar, C.Raja, Satish Addanki

Abstract: The bulk planar junctionless transistor (BPJLT) is a potential candidate for future CMOS technologies due to its CMOS compatibility and scalability. In this paper, the impact of silicon film thickness and channel doping on single-event upset (SEU) radiation performance of BPJLT based SRAMs is studied using TCAD simulations. The simulation results show that BPJLT devices having higher channel doping and smaller film thickness provides the better SEU performance.

Keywords: BPJLT, SRAM, Threshold LET, SEU, TCAD.

#### I. INTRODUCTION

Since its introduction in 2010, various structures of Junctionless transistors (JLTs) have been explored in the literature [1-8]. Among these structures, single gate bulk planar JLT (BPJLT) is the most attractive structure because of the CMOS process compatibility and reduced fabrication costs. SOI based JLT devices can also be considered for planar structures but a film thickness of 5 nm or below is needed, for a work function of 5.5 eV at 20 nm channel length. The BPJLT devices relax this tight constraint on film thickness due to their P-N junction present between the film/epi/channel and substrate. So it's becoming a popular technology to replace the existing CMOS technologies.

BPJLT device is a single-gate device with the same type of doping throughout the entire active silicon layer, including source, channel and drain regions. It has no junctions along the channel direction, but it has junctions in the vertical direction for isolation purposes. It leads to the two additional control parameters (substrate bias ( $V_{sub}$ ) and substrate doping ( $N_{sub}$ )) for tuning the device performance. These two control parameters define the effective thickness of the device layer. For example, the BPJLT with 10 nm device layer thickness has an effective device layer thickness of about 5 nm since the bottom 5 nm device layer is depleted by the built-in junction potential in the vertical junction.

#### Revised Manuscript Received on October 30, 2019.

\* Correspondence Author

**N.Vinodhkumar**, Department of Electronics and Communication Engineering, Vel Tech Rangarajan Dr. Sagunthala R&D Institute of Science and Technology, Chennai, India. Email: vinodhkumar.cc@gmail.com

**C.Raja**, Professor, Department of Electronics and Communication Engineering, Koneru Lakshmaiah Education Foundation, Vaddeswaram, A.P., India, Email: rajachandru82@yahoo.co.in

Satish Addanki\*, Department of Electronics and Communication Engineering, Sasi Institute of Technology and Engineering, Aerodrome Road, Tadepalligudem – 534101, AP, India, Email: addankisatish1@gmail.com

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license <a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>

So the device layer can be controlled effectively [9]. Soft errors, one of the problems due to single event effects (SEE) have been a most important reliability concern in the technological advancement of memories, especially SRAMs, in radiation prone environments. The sensitivity of SRAMs to radiation has gone up with CMOS scaling [10].

Several studies on soft error performance of various JLT devices are available in the literature [11-14]. All these studies are done only in SOI based JLT devices. Only few studies are reported in bulk JLT devices in comparison with SOI JLT devices [15, 16]. In this work, we explore the SEU performance of the bulk planar junctionless devices with various channel doping ( $N_{ch}$ ) and silicon film thickness ( $T_{Si}$ ). The paper is organized as follows: section 2 provides the device structure and calibration, section 3 provides the simulation results and discussions. Finally, section 4 gives the conclusion.

### II. DEVICE STRUCTURE AND CALIBRATION

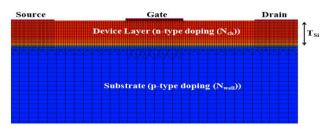

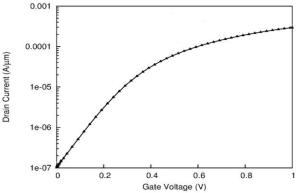

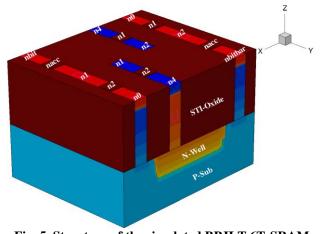

Sentaurus TCAD simulator from Synopsys is used in this study [17]. Fig. 1 shows the structure of BPJLT device generated from SDE. The device parameters used in this study are given in Table I. The models used in the device simulation include SRH and Auger recombination models, mobility model with doping and field dependence. Quantum corrections are also taken into account. This BPJLT device is calibrated against the published results [9] using  $I_D\text{-}V_G$  simulations and is shown in Fig. 2.

**Table-I: BPJLT Device parameters**

| Parameter                                                  | Value                               |

|------------------------------------------------------------|-------------------------------------|

| Gate length (Lg)                                           | 20 nm                               |

| Gate oxide thickness (Tox)                                 | 1 nm                                |

| Junction depth (X <sub>j</sub> ) or Device layer thickness | 12 nm                               |

| Gate work function ( $\phi_m$ )                            | 5.1 eV                              |

| Donor doping in device layer (N <sub>d</sub> )             | 2x10 <sup>19</sup> cm <sup>-3</sup> |

| Substrate doping (N <sub>well</sub> )                      | 5x10 <sup>18</sup> cm <sup>-3</sup> |

| Supply voltage (V <sub>DD</sub> )                          | 1 V                                 |

Fig .1. 2D-Structure of the BPJLT device with meshing

Journal Website: www.ijitee.org

Fig. 2.  $I_{D\_}V_G$  characteristics of the N-Type BPJLT device

## III. RESULTS AND DISCUSSION

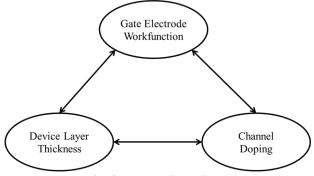

The design of JLT involves three critical design parameters channel doping ( $N_{ch}$ ), silicon film thickness ( $T_{Si}$ ) and gate electrode work function (WF) (refer Figure 3). Among these two important parameters (channel doping ( $N_{ch}$ ), silicon film thickness ( $T_{Si}$ )), which influences the radiation performance has been taken and the effect of these two parameters on BPJLT device SEU performance are studied using TCAD simulations in this section.

Fig .3. JLT design triangle

Before doing the radiation study, the impact of silicon film thickness  $(T_{Si})$  and channel doping  $(N_{ch})$  on the DC performance parameters (i.e. ON Current  $(I_{ON})$  and OFF Current  $(I_{OFF}))$  of BPJLT device are studied and is given in Table II & III respectively.

Table II:  $I_{\rm ON}$  and  $I_{\rm OFF}$  of BPJLT devices with various

| $1_{\mathbf{Si}}$ |                                           |                      |                             |  |  |  |

|-------------------|-------------------------------------------|----------------------|-----------------------------|--|--|--|

| S.No              | Silicon<br>film<br>thickness<br>(TSi)(nm) | ON current (ION)(µA) | OFF<br>current<br>(IOFF)(A) |  |  |  |

| 1                 | 6                                         | 3.22                 | 2.45E-16                    |  |  |  |

| 2                 | 8                                         | 60.5                 | 1.00E-13                    |  |  |  |

| 3                 | 10                                        | 163                  | 1.10E-10                    |  |  |  |

| 4                 | 12                                        | 295                  | 1.02E-07                    |  |  |  |

| 5                 | 14                                        | 445                  | 1.80E-05                    |  |  |  |

| 6                 | 16                                        | 605                  | 1.21E-04                    |  |  |  |

Table-III: I<sub>ON</sub> and I<sub>OFF</sub> of BPJLT devices with various

|   | $N_{ m ch}$ |                      |                   |                |  |  |

|---|-------------|----------------------|-------------------|----------------|--|--|

|   | S.No        | Channel doping (Nch) | ON current        | OFF            |  |  |

|   |             | (per cm3)            | $(I_{ON})(\mu A)$ | current        |  |  |

|   |             |                      |                   | $(I_{OFF})(A)$ |  |  |

|   | 1           | 1e19                 | 8.69              | 4.28e-15       |  |  |

| į | 2           | 1.5e19               | 120               | 4.88e-11       |  |  |

|   | 3           | 2e19                 | 295               | 1.02e-7        |  |  |

|   | 4           | 2.5e19               | 496               | 1.688e-7       |  |  |

|   | 5           | 3e19                 | 709               | 116e-6         |  |  |

From Table II, it can be observed that as the silicon film thickness increases, both the ON and the OFF state currents are increases. The practical values of the film thicknesses are highlighted in Table II. Beyond this range, either the  $I_{\rm ON}$  is too low or the  $I_{\rm OFF}$  is too high. Similarly the increase in the channel doping increases both  $I_{\rm ON}$  and  $I_{\rm OFF}$ . Once again the practical values of doping values are highlighted in Table III. Beyond this range, either the  $I_{\rm ON}$  is too low or the  $I_{\rm OFF}$  is too high. Either the increase in the film thickness for the given channel doping or the increase in the channel doping for the given film thickness increases  $I_{\rm OFF}$  due to the reduced electrostatic control resulting from poor depletion of the channel in the OFF state.

Since the  $I_{OFF}$  is affected drastically (Table II & III) when the film thickness or channel doping is changed, for the fair comparison  $I_{OFF}$  is maintained constant (i.e.  $I_{OFF}$  is constrained to 100 nA/µm which is the  $I_{OFF}$  of reference device). For the subsequent study carried out  $I_{OFF}$  is maintained constant. This constraint is met by changing the two other parameters as one parameter is not sufficient to achieve this constraint. Following cases are explored to study the impact of  $T_{\rm Si}$  and  $N_{\rm ch}$  on BPJLT DC performance.

- Case 1: Vary  $T_{si}$  and adjust WF and  $N_{ch}$  to constraint  $I_{OFF}$

- Case 2: Vary  $N_{ch}$  and adjust WF and  $T_{si}$  to constraint  $I_{OFF}$  In the Case 1, we have studied three different  $T_{Si}$  (12, 15, and 20 nm), and WF and  $N_{ch}$  are adjusted to achieve the  $I_{OFF}$  of 100 nA/ $\mu$ m.

In the Case 2, three different  $N_{ch}$  (2e19, 2.5e19, 3e19 (per cm<sup>3</sup>)) are studied, and  $T_{Si}$  and WF are tuned to meet the  $I_{OFF}$  constraint (i.e. 100 nA/ $\mu$ m).

Table IV presents the ON to OFF current ratios of case 1 and case 2. It can be noticed that  $I_{ON}/I_{OFF}$  ratio gets degraded with the increase in film thickness while it improves with the increase

in channel doping. Reduced  $T_{Si}$  improves the electrostatic control of the channel in the OFF state whereas increased  $N_{ch}$  enhances the conductivity in the ON state. So the devices with increased  $N_{ch}$  and reduced  $T_{Si}$  (i.e. Case 2 devices) yields better  $I_{ON}/I_{OFF}$  ratio in the BPJLT devices. The access pulse (V(nacc)) of 10 ps of rise and fall times, and a pulse width of 250 ps is used to verify the SRAM functionality. After SRAM functionality verification, the soft error simulation is done by using heavy ion models in SDEVICE simulator. The heavy ion radiation model is

Journal Website: www.ijitee.org

| Table-1v: 10N/10FF ratio of various DFJL1 devices used in this study |                           |                 |                           |         |                    |

|----------------------------------------------------------------------|---------------------------|-----------------|---------------------------|---------|--------------------|

| Name                                                                 | Varying                   | Silicon film    | 1 1 1 8                   |         | $I_{ON}/^*I_{OFF}$ |

|                                                                      | Parameter                 | thickness (TSi) |                           |         | ratio              |

| Case 1                                                               | Film                      | 12 nm           | 2e19 cm <sup>-3</sup>     | 5.1 eV  | 2894               |

|                                                                      | Thickness                 | 15 nm           | 1.715e19 cm <sup>-3</sup> | 5.4 eV  | 2180               |

|                                                                      | $(T_{Si})$                | 20 nm           | 1.15e19 cm <sup>-3</sup>  | 5.4 eV  | 1501               |

| Case 2                                                               | Channel                   | 12 nm           | 2e19 cm <sup>-3</sup>     | 5.1 eV  | 2894               |

|                                                                      | Doping (N <sub>ch</sub> ) | 10 nm           | 2.5e19 cm <sup>-3</sup>   | 5.04 eV | 3316               |

|                                                                      |                           | 0 nm            | 2a10 am <sup>-3</sup>     | 4.09 aV | 2729               |

Table-IV: I<sub>ON</sub>/I<sub>OFF</sub> ratio of various BPJLT devices used in this study

For further study (radiation study) on BPJLT devices we have taken only the devices with better  $I_{ON}/I_{OFF}$  ratio (i.e. Case 2 devices in Table IV).

## A. SEU study on BPJLT based 6T-SRAMs

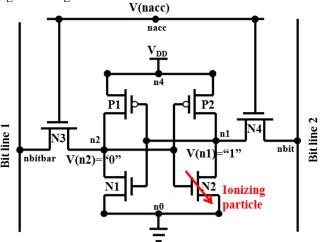

The SEU study is carried out using TCAD simulations. The 6T-SRAM cell used in this SEU study is shown in Fig. 4. The BPJLT devices with better  $I_{ON}/I_{OFF}$  ratio are used for creating SRAMs. The 3D structure of the simulated BPJLT 6T-SRAM is given in Fig. 5.

Fig. 4. 6T-SRAM cell schematic structure used in this SEU study

Fig. 5. Structure of the simulated BPJLT 6T-SRAM

characterized by the particle direction (perpendicular to the device), characteristic radius (20 nm), dose value or Linear Energy Transfer (LET in pC/ $\mu$ m or MeV/(mg/cm²)), location

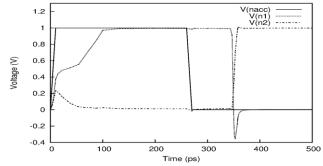

of the strike, length of the ion track, temporal and spatial variation of generation rate (Gaussian function is used in this study) [17]. The radiation strikes at the sensitive node (the node which stores logic 1) of SRAM cell when the access pulse is zero (V(nacc) in Fig. 6).

Fig. 6. Variation of node voltages with respect to time (Heavy ion strikes at 350 ps with the LET value of 0.137

MeV/(mg/cm<sup>2</sup>)

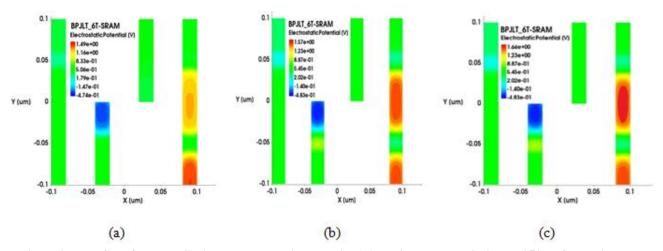

Figure 6 illustrates the node voltages (V(n1) and V(n2)) of the BPJLT SRAM cell for the LET value (0.137 MeV/(mg/cm<sup>2</sup>)) which flips the SRAM cell. The SEU threshold LET (LETth -The minimum LET value needed to flip the SRAM cell) is obtained by varying the ion strike LET until the SRAM cell flips. It is done for all the cases considered in this study and its LET<sub>th</sub> values are given in Table V. It can be observed from Table V that the BPJLT devices with the higher doping and smaller film thickness show better SEU performance i.e. higher LETth. The LETth of SRAM is decided by the drive current of PMOS (I<sub>PMOS</sub>) and collected charge at the strike node [12]. On one hand devices with smaller film thickness provides the better electrostatic control which results in smaller collected charge. It is clearly depicted in Fig. 7. Figure 7 shows the 2-D profile of electrostatic potential across the BPJLT SRAMs during the peak radiation for a LET value of 0.1 MeV/(mg/cm<sup>2</sup>), this LET value does not flip the BPJLT SRAM structures. The electrostatic potential at the strike location for various BPJLT SRAMs ( $T_{Si} = 12 \text{ nm}$ , 10nm, 8nm and  $N_{ch} = 2e19 \text{ cm}^{-3}$

Published By:

<sup>\*</sup>  $I_{OFF} = 100 \text{ nA/um}$

## Table-V: LET<sub>th</sub> of various BPJLT based SRAMs

| S.N | Gate work | Silicon film                | Channel doping                   | Collected   | $I_{PMOS}$ | $LET_{th}$        |

|-----|-----------|-----------------------------|----------------------------------|-------------|------------|-------------------|

| О   | function  | thickness (T <sub>Si)</sub> | concentration (N <sub>ch</sub> ) | Charge (fC) | (µA)       | $(MeV/(mg/cm^2))$ |

|     | (WF)      |                             |                                  |             |            |                   |

| 1   | 5.1 eV    | 12 nm                       | 2e19 cm <sup>-3</sup>            | 1.027       | 229        | 0.137             |

| 2   | 5.04 eV   | 10 nm                       | 2.5e19 cm <sup>-3</sup>          | 0.958       | 263        | 0.365             |

| 3   | 4.98 eV   | 8 nm                        | 3e19 cm <sup>-3</sup>            | 0.919       | 297        | 0.546             |

Fig. 7. 2-D profile of BPJLT SRAMs electrostatic potential (V) during peak radiation at 350 ps for various cases considered in this study i.e.  $T_{Si}$  = 12 nm, 10 nm, 8 nm and  $N_{ch}$  = 2e19 cm<sup>-3</sup>, 2.5e19 cm<sup>-3</sup>, 3e19 cm<sup>-3</sup> respectively for a LET value of 0.1 MeV/(mg/cm<sup>2</sup>)

$2.5e19~cm^{-3}$ ,  $3e19~cm^{-3}$ ) considered in this study is 1.49~V, 1.57~V and 1.64~V respectively. On the other hand increased  $N_{ch}$  helps in improving the PMOS drive current. These improvements resulting in the SEU performance enhancement of the SRAM cells i.e. higher LET<sub>th</sub> for BPJLT SRAM which is having smaller film thickness and the higher doping.

#### IV. CONCLUSION

The impact of silicon film thickness and channel doping on SEU radiation performance of bulk planar Junctionless devices based SRAMs have been studied using TCAD simulations. Simulation results reveal that the BPJLT devices having higher doping and smaller film thickness provides the better SEU performance.

# REFERENCES

- C.-W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, and J. P. Colinge, "Junctionless multigate field-effect transistor," Appl. Phys. Lett., vol. 94, p. 053511, 2009.

- J. P. Colinge, C.-W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O'Neill, A. Blake, M. White, A.-M. Kelleher, B. Mc-Carthy, and R. Murphy, "Nanowire transistors without junctions," Nature Nanotechnol., vol. 5, pp. 225–229, 2010.

- C.-W. Lee, A. Borne, I. Ferain, A. Afzalian, R. Yan, N. D. Akhavan, P. Razavi, and J. P. Colinge, "High temperature performance of silicon junctionless MOSFETs," IEEE Trans. Electron Devices, vol. 53, no. 3, pp. 620–625, Mar. 2010.

- A. Kranti, R. Yan, C.-W. Lee, I. Ferain, R. Yu, N. D. Akhavan, P. Razavi, and J. P. Colinge, "Junctionless Nanowire Transistor (JNT): Properties and design guidelines," in Proc. Euro. Solid-State Device Res. Conf. (ESSDERC), 2010, pp. 357–360.

- Ming-Hung Han, Chun-Yen Chang, Hung-Bin Chen, Jia- Jiun Wu, Ya-Chi Cheng, and Yung-Chun Wu, "Performance Comparison

- between Bulk and SOI Junctionless Transistors," IEEE Electron Device letters, vol. 34, no. 2, pp. 169-171, February 2013.

- Su, C.-J., Tsai, T.-I., Liou, Y.-L., Lin, Z.-M., Lin, H.-C., Chao, T.-S.: Gate-all-around junctionless transistors with heavily doped polysilicon nanowire channels. IEEE Electron. Device Lett. 32(4), 521–523 (2011).

- Han, Ming-Hung, Chang, Chun-Yen, Chen, Hung-Bin, Jia-Jiun, Wu, Cheng, Ya-Chi, Yung-Chun, Wu: Performance comparison between bulk and SOI junctionless transistors. IEEE Electron. Device Lett. 34(2), 169–171 (2013).

- S.Gundapaneni, S.Ganguly, A.Kottantharayil, "Enhanced electrostatic integrity of short channel Junctionless transistor with high-k spacers", IEEE Electron Device Letters, vol.32, no.10, pp.1325-1327, 2011.

- Gundapaneni, S, Ganguly, S & Kottantharayil, A 2011a, 'Bulk Planar Junctionless Transistor (BPJLT): An Attractive Device Alternative for Scaling', IEEE Electron Device Letters, vol. 32, no. 3, pp. 261-263.

- P.K. Saxena, N. Bhat, "SEU Reliability improvement due to source-side charge collection in the deep-submicron SRAM cell," *IEEE Trans. on Device and Materials Reliability*, Vol. 3, No.1, pp. 14-17, 2003.

- D. Munteanu, J.L. Autran "3-D Numerical simulation of bipolar amplification in junctionless double-gate MOSFETs under heavy- ion irradiation," IEEE Trans. On nuclear science, vol. 59, no. 4, pp. 773-780, Aug. 2012.

- D. Munteanu, J. L. Autran, "Radiation sensitivity of Junctionless double-gate 6T SRAM cells investigated by 3-D numerical simulations," Microelectronics Reliability, vol. 54, pp. 2284–2288, 2014

- D.Munteanu, J.L. Autran, SEU sensitivity of Junctionless Single-Gate SOI MOSFETs-based 6T SRAM cells investigated by 3D TCAD simulation, Microelectronics Reliability, vol. 55, pp. 1501–1505, 2015.

- 14. N.Vinodhkumar and R.Srinivasan, "SET and SEU Performance of Single, Double, Triple and Quadruple-Gate JunctionlessFETs and SRAMs using Numerical Simulations", Microelectronics, Vol. 67, No. 10, September 2017, pp.38-42.

- N.Vinodhkumar, Y.V. Bhuvaneshwari, K.K. Nagarajan, R.Srinivasan, "Heavy-Ion Irradiation Study in SOI-based and Bulk-based Junctionless FinFETs using 3D-TCAD Simulation," Microelectronics Reliability, vol. 55, pp. 2647-2653, 2015.

- N.Vinodhkumar and Dr.R.Srinivasan, "Radiation performance of planar junctionless devices and junctionless SRAMs", Journal of Computational Electronics, Vol. 15, No. 1, March 2016, pp. 61-66.

- Synopsys Sentaurus TCAD tools, Available online http://www.synopsys.com/products/tcad/tcad.html.

## **AUTHORS PROFILE**

N.Vinodhkumar, received B.E in Electronics and Communication Engineering, M.E in Computer and Communication and Ph.D in Nanoelectronics from Anna University, Chennai in 2007, 2010 and 2017 respectively. After his Ph.D, he had been associated with Centre for Reliability Sciences and Technology, Chang Gung University, Taiwan as Post Doctoral

Fellow for the period of one year. Now he is currently working as an Assistant Professor in ECE department, Vel Tech Rangarajan Dr.Sagunthala R&D Institute of Science and Technology, Chennai. His research interests include Semiconductor device modeling, Radiation effects in CMOS devices and circuits.

C.Raja, received PhD degree from Anna University, Chennai in the faculty of Information & Communication Engineering in 2016, specialized in Medical image processing; He received his M.Tech. Degree in Biomedical Signal Processing and Instrumentation in 2005 from SASTRA University & B.E. Degree in Electronics and Communication Engineering in 2003

from Bharathidasan University. From 2005 to till date he has been working as Assistant and Associate Professor in Engineering colleges in India. His present affiliation is with KL University, Vijayawada designated as Professor in ECE. To his credit he has published 6 research papers in SCI, 6 research papers in Scopus indexed international journals and international —level conferences. His research interests are digital image processing, wavelets, optimization (swarm intelligence) and deep learning.

Satish Addanki, is working as Associate Professor in the Department of Electronics and Communication Engineering, Sasi Institute of Engineering and Technology, Andhra Pradesh, India. Previously he worked as Assistant Professor, Department of Railroad Integrated Systems, Woosong University, Deajeon, South Korea. He obtained Ph.D. from University of Madras, Chennai in 2017 and M.E degree in Embedded

System technologies and B.E degree in Electronics and Communication Engineering from Anna University, Chennai, India in 2007 and 2009. He has five years of teaching, four years of research and industry experience. His areas of interest are MEMS, Embedded System Technologies, Communication Systems and Instrumentation.

Published By: