# Design of Hybrid LUT/MUX FPGA Logic Architecture for size Reduction and Performance Improvement in FPGA

V.Aruna, Ch.Srigiri

Abstract: Hybrid configurable logic block architectures for field-programmable gate arrays that contain a blend of LUT's and solidified multiplexers that are assessed towards the objective of higher rationale thickness and diminished region. Innovation mapping advancements that focus on the proposed models are likewise perform inside Xilinx programming. Both for complex rationale square and steering territory while keeping up mapping profundity, the named engineering of this paper examine the rationale size, region and power utilization utilizing Xilinx 14.5.

Index Terms: FPGA, CLB's, and Look up Tables, Multiplexers, and Fracturable Architectures.

#### I. INTRODUCTION

Half and half configurable rationale square structures for field-programmable door exhibits that contain a blend of query tables and solidified multiplexers are assessed toward the objective of higher rationale thickness and zone decrease. Innovation mapping improvements that focus on the proposed structures are likewise actualized inside ABC. Both representing complex rationale square and directing territory while keeping up mapping profundity. For factorable structures, the proposed design of this paper investigation the rationale size, zone and power utilization utilizing Xilinx 14.2. Since the commencement of fieldprogrammable entryway exhibits (FPGAs), query tables (LUTs) have been the essential rationale component (LE) used to acknowledge combinational rationale. A K-input LUT is conventional and entirely adaptable—ready to actualize any K-input Boolean capacity. The utilization of LUTs streamlines innovation mapping as the issue is decreased to a diagram covering issue. Notwithstanding, an exponential zone cost is paid as bigger LUTs are considered. The estimation of K somewhere in the range of 4 and 6 is commonly found in industry and the scholarly world, and has been shown to offer a decent this range territory/execution bargain. As of late, various different works have investigated elective FPGA LE models for execution improvement to close the enormous hole among FPGAs and application-explicit incorporated circuits (ASICs). The MUX based rationale hinders for the FPGAs have seen accomplishment in early business designs, for example,

Revised Manuscript Received on October 30, 2019.

\* Correspondence Author

V.Aruna\*, M.Tech (Vlsi And Es) Godavari Institute Of Engineering And Technology, Rajahmundry, A. P. India.

**Ch.Srigiri,** Asst.Professor, Dept. Of Electronics & Communication Engg In Godavari Institute Of Engineering And Technology, Rajahmundry, A. P. India.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license <a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>

the Actel ACT-1/2/3 models, and productive mapping to these structures has been examined in the mid 1990s. Be that as it may, their utilization in business chips has disappeared, Maybe mostly because of the simplicity with which rationale capacities can be mapped into LUTs, rearranging the whole PC supported structure (CAD) stream. By the by, it is generally comprehended that the LUTs are wasteful at actualizing MUXs, and that MUXs are as often as possible utilized in rationale circuits. To underscore the wastefulness of LUTs executing MUXs, think about that a six info LUT (6-LUT) is basically a 64-to-1 MUX (to choose 1 of 64 truth-table lines) and 64-SRAM arrangement cells, yet it can just understand a 4-to-1 MUX (4 information + 2 select = 6 data sources).

#### II. LOOKUP TABLES

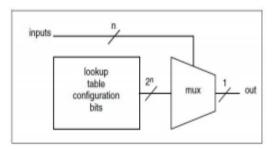

The basic system used to make a combinational method of reasoning square (CLB) furthermore called a justification segment in a SRAM-based FPGA is the inquiry table (LUT). As indicated by the underneath Fig, the inquiry table is a Static Random Access Memory and is used to execute a reality table. Each address in the SRAM addresses a combinational commitments to the method of reasoning part. The regard set away in the location addresses the estimation of the limit with respect to that data mix. A n-input work requires a SRAM with regions.

Since a fundamental SRAM isn't timed, the query table rationale component works much as some other rationale entryway as its sources of info changes, its yield changes after some deferral.

Figure - 1Lookup Tables

### III. PROGRAMMING A LOOKUP TABLE

Dissimilar to a run of the mill rationale entryway, the capacity spoken to by the rationale component can be changed by changing the estimations of the bits spared in the SRAM. Subsequently, the n-input rationale component can speak to capacities.

A reason part has four wellsprings of data.

The delay in the inquiry table is free of the bits taken care of in the SRAM, so the deferral through the justification segment is the equivalent for all limits. Hugeness of this is, for example, a question table based reason segment will demonstrate a comparable deferment for a 4-input XOR and a 4-input NAND. In contrast, a 4-input XOR worked with static CMOS method of reasoning is much more slow than a 4-input NAND. Clearly, the static method of reasoning gateway is commonly quick than the basis segment. Basis segments contain registers, flip-droops and bolts and furthermore combinational method of reasoning. A fliptumble or snare is little appeared differently in relation to the combinational basis segment, so it has noteworthiness to add it to the combinational method of reasoning segment. Using a substitute cell for the memory part would basically take up coordinating resources. The memory segment is associated with the yield, paying little mind to whether it stores a given regard is constrained by its clock and engage inputs. In this paper, we propose joining (a couple) hardened multiplexers (MUXs) in the FPGA justification blocks that surmise growing silicon domain capability and basis thickness. The MUX based reason thwarts for the FPGAs have seen triumph in early plans of action, for instance, the Actel, ACT1/2/3 plans, and beneficial mapping to these structures has been inspected in the mid 1990s. Regardless, their use in business chips has slowed down, possibly deficiently due to the straightforwardness with which method of reasoning limits can be mapped into LUTs, restricting the entire PC helped plan (CAD) stream. Regardless, it is extensively understood that the LUTs are inefficient at completing MUXs, and that MUXs are once in a while used as a piece of method of reasoning circuits. To underscore the inefficiency of LUTs realizing MUXs, consider that a six data LUT (6-LUT) is essentially a 64-to-1 MUX (to pick 1 of 64 truth-table lines) and 64-SRAM plan cells, yet it can simply comprehend a 4-to-1 MUX (4 data+2 select=6 inputs). In this endeavor, we show a six-input LE in light of a 4-to-1 MUX, MUX4, that can comprehend a subset of six-input Boolean justification limits, and another crossbreed complex method of reasoning piece (CLB) that has a mix of MUX4s and 6-LUTs. The proposed MUX4s are little differentiated and a 6-LUT (15% of 6-LUT region), and can capably plot {2,3}-data and some {4,5,6}-input limits.

#### IV. OBJECTIVE:

Numerous half breed configurable rationale square models, both nonfracturable and fracturable with fluctuating MUX:LUT rationale component proportions are assessed in yosys combination device utilizing a custom device stream comprising of verilog coding, yosys front-end union, ABC rationale blend and innovation mapping, and plan ahead Xilinx instrument for pressing, arrangement, directing, and design investigation. Innovation mapping enhancements that focus on the proposed structures are likewise actualized inside ABC. In this paper, we present a six-input LE dependent on a 4-to-1 MUX, MUX4, that can understand a subset of six-input Boolean rationale capacities, and another half and half complex rationale square (CLB) that contains a blend of MUX4s and 6-LUTs. The proposed MUX4s are little contrasted and a 6-LUT (15% of 6-LUT region), and can effectively outline {2, 3}-input capacities and some {4, 6}-input capacities. Moreover, we investigate factorability of LEs—the capacity to part the LEs into different littler components—in both LUTs and MUX4s to expand rationale thickness. The proportion of LEs that ought to be LUTs versus MUX4s is additionally investigated toward enhancing rationale thickness for both nonfracturable and fracturable.

#### V. LITERATURE REVIEW

Late Practices have exhibited that the heterogeneous models and amalgamation techniques can profoundly influence improving reason thickness and deferment, narrowing the ASIC-FPGA gap. Works by Anderson and Wang with gated LUTs, by then with uneven LUT LEs, exhibit that the LUT segments present in business FPGAs give unnecessary flexibility. So as to get the improved delay and domain, the macrocellbased FPGA structures have been proposed. These assessments unveil basic changes to the traditional FPGA plans, while the movements proposed here develop structures used as a piece of industry and the insightful world. So additionally, and-inverter cones have been proposed as swaps for the LUTs, charged by and-inverter outlines (AIGs). This paper presents preliminary estimations of the complexities between the no.of segments used as a piece of terms of method of reasoning thickness, circuit speed, and power use for focus basis. We are influenced to make these estimations to engage system originators to choose better taught choices between these two media and to offer information to FPGA makers on the insufficiencies to strike and, thusly, upgrade FPGAs. We depict the method by which the estimations were procured and exhibit that, for circuits containing simply investigate table-based justification and flip-flops, the extent of silicon district required to execute them in FPGAs and ASICs is all things considered . Present day FPGAs in like manner contain "hard" pieces, for instance, multiplier/authorities and square memories. We find that these squares decline this ordinary area cleft basically to as small as 18 for our benchmarks, and we assess that expansive usage of these hard pieces could possibly cut down the gap to underneath five. The extent of fundamental path delay, from FPGA to ASIC, is around three to four with less effect from square memory and hard multipliers. In this paper the new building proposals are routinely created in both insightful world and industry. For all FPGA's on developing, it is imperative that these new building musings are acceptably and correctly evaluated, with the objective that those honorable considerations can be fused into future chips. Usually, this appraisal is done using experimentation. Regardless, the use of experimentation is unsafe, since it requires causing suppositions with respect to the contraptions and structure of the device being alluded to. In case these assumptions are not exact, the ends from the investigations may not be huge. In this paper, we investigate the affectability of FPGA compositional ends to preliminary assortments. To make our assessment strong, we evaluate the affectability of four previously appropriated and without a doubt comprehended FPGA auxiliary results: inquiry table size, switch piece topology, bundle size, and memory measure. It is shown that these preliminaries are inside and out affected by the suppositions, devices, and methods used as a piece of the tests.

#### VI. RELEGATED WORK EXISTING SYSTEM

Late works have demonstrated that the heterogeneous models and union systems could sizably affect upgrading rationale thickness and defer, narrowing the ASIC-FPGA hole. Works by utilizing Anderson and Wang with -gated LUTs, at that point with lopsided LUT LEs, demonstrate that the LUT components found in business FPGAs offer futile adaptability. Toward ventured forward put off and district, the microcell-based absolutely FPGA designs have been proposed. [3] These examinations depict broad changes to the conventional FPGA models, while the modifications proposed directly here expand on structures utilized in industry and the scholarly community. Correspondingly, and-inverter cones had been proposed as substitutes for the LUTs, animated by utilizing and-inverter diagrams (AIGs) .Purnaprajna and Ienne investigated the chance of repurposing the predominant MUXs contained inside the Xilinx Logic Slices. Like this work, they utilize the ABC need slice mapper notwithstanding VPR for pressing, district, and bearing. Nonetheless, their works of art is for the most part defer based thoroughly demonstrating a middle speedup of 16% the utilization of best ten of nineteen VTR7 benchmarks

#### VII. PROPOSED ARCHITECTURES

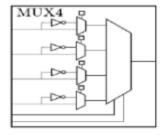

#### A. MUX4: 4-to-1 Multiplexer Logic Element

The MUX4 LE appeared in Fig2 comprises of a 4-to-1 MUX with discretionary reversal on its information sources that permit the acknowledgment of any {2, 3}-input work, some {4, 5}-input capacities, and one 6-input work a 4-to-1 MUX itself with discretionary reversal on the information inputs. A 4-to-1 MUX matches the information stick check of a 6-LUT, taking into account reasonable examinations as for the availability and intra group steering. Normally, any two-input Boolean capacity can be effectively executed in the MUX4: the two capacity sources of info can be attached to the select lines and reality table qualities (rationale 0 or rationale 1) can be directed to the information inputs appropriately. Or on the other hand on the other hand, a Shannon disintegration can be performed around one of the two factors the variable would then be able to nourish a select info.

The Shannon cofactors will contain all things considered one variable and can, subsequently, be bolstered to the information inputs (the discretionary reversal might be required). For three-input capacities, think about that a Shannon decay around one variable produces cofactors with at most two factors. A second decay of the cofactors around one of their two outstanding factors produces cofactors with at most one variable. Such single-variable cofactors can be sustained to the information inputs (the discretionary reversal might be required), with the disintegration factors bolstering the select data sources.

Fig 2. MUX4 LE depicting optional data input inversions.

A second decomposition of the cofactors about one of their two remaining variables produces cofactors with at most one variable. Such single variable cofactors can be fed to the data inputs (the optional inversion may be needed), with the decomposition variables feeding the select inputs. Likewise, functions of more than four inputs can be implemented in

the MUX4 as long as Shannon decomposition with respect to any two inputs produces cofactors with at most one input.

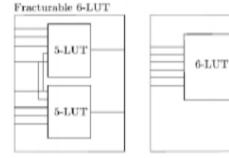

## B. Logic Elements, Factorability, and MUX4-Based Variants

Two groups of designs were made: 1) without factorable Les and2) with factorable Les. In this paper the factorable Les allude to a structural component on which at least one rationale capacities can be alternatively mepped.

Fig3. Factorable 6-LUT that can be fractured into two 5- LUTs with two shared inputs.

Non factorable LEs allude to a structural component on which just a single rationale capacity is mapped. In the non-factorable structures, the MUX4 component appeared in Fig. 2 is utilized together with non-factorable 6-LUTs. This component has indistinguishable number of contributions from a 6-LUT loaning for reasonable examination as for the

information network. For the factorable engineering, we think about an eight-input LE, firmly coordinated with the versatile rationale module in late Altera Stratix FPGA families. A 6-LUT that can be cracked into two 5-LUTs utilizing eight sources of info is appeared in Fig. 3.

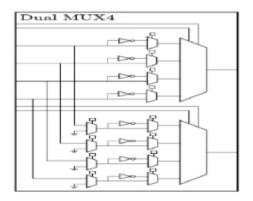

Fig4. Dual MUX4 LE that utilizes dedicated select inputs and shared data inputs.

Two five-input functions can be mapped into this LE if two inputs are shared between the two functions

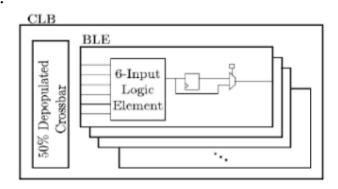

Fig5. Hybrid CLB with a 50% depopulated intra-CLB crossbar depicting BLE internals for a nonfactorable (one optional register and one output) architecture.

On the off chance that no data sources are shared, two four-input capacities can be mapped to every 5-LUT. For the MUX4 variation, Dual MUX4, we utilize two MUX4s inside a solitary eight-input LE. In the design, appeared in Fig. 4, the two MUX4s are wired to have committed select sources of info and shared information inputs. This

arrangement enables this structure to delineate free (no mutual data sources) three-input capacities, while bigger capacities might be mapped reliant on the common contributions between the two capacities. A design wherein a 4-to-1 MUX (MUX4) is broken into two littler 2-to-1 MUXs was first considered.

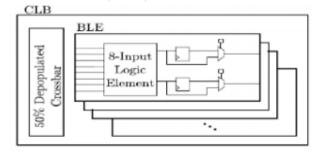

Fig6. Hybrid CLB with a 50% depopulated intra-CLB crossbar depicting BLE internals for a factorable (two optional registers and two outputs) architecture.

#### C. Hybrid Complex Logic Block

A wide range of models were viewed as the first being a non-factorable engineering. In the non-factorable design, the CLB has 40 sources of info and ten essential LEs (BLEs), with each BLE having six information sources and one yield following observational information in earlier work [4]. Fig. 5 demonstrates this non factorable CLB design with BLEs that contain a discretionary register. We shift the proportion of MUX4s to LUTs inside the ten component CLB from 1:9 to 5:5 MUX4s:6-LUTs. The MUX4 component is proposed to work related to 6-LUTs, making a half and half CLB with a blend of 6-LUTs and MUX4s (or MUX4 variants).Fig5 demonstrates the association of our CLB and interior BLEs. For factorable structures, the CLB has 80 sources of info and ten BLEs, with each BLE having eight data sources and two yields imitating an Altera Stratix Adaptive-LUT.

A similar compass of MUX4 to LUT proportions was additionally performed. Fig6 demonstrates the factorable design with eight contributions to each BLE that contains two discretionary registers. We assess factorability of LEs versus non factorable Les with regards to MUX4 components since factorable LUTs are basic in business designs. The crossbar for factorable designs are bigger than

the non-factorable structures for two reasons. Because of the virtual increment of LEs, a bigger number of CLB information sources are required, which builds crossbar size. Since there are currently twice the same number of yields from the LEs, these extra yields need to likewise be encouraged once more into the crossbar, additionally expanding its size. Because of this divergence in crossbar size, reasonable examinations can't be made among factorable and non-factorable structures.

Along these lines, in this paper, we contrast non factorable crossover CLB structures with a gauge LUT just non-factorable design and we contrast factorable half and half CLB models with a pattern LUT-just factorable engineering. we model a half eliminated crossbar inside the CLB for intra bunch steering for both non factorable and factorable designs as contrasted and the fundamental production [15] that solitary displayed a full information crossbar.

VIII. RESULTS

PROPOSED RESULT:

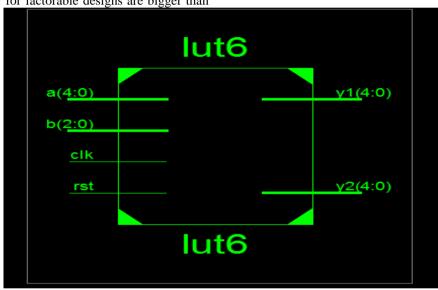

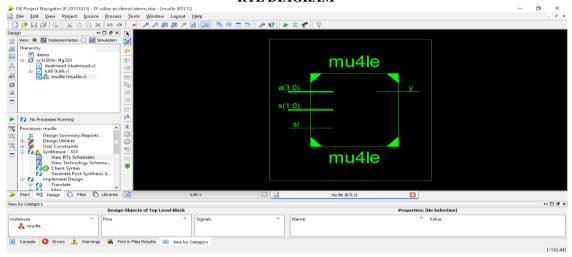

RTL

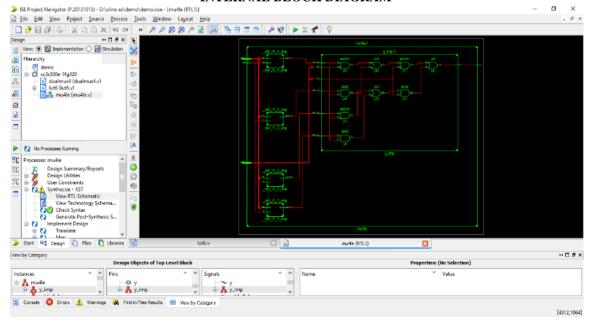

Internal block diagram

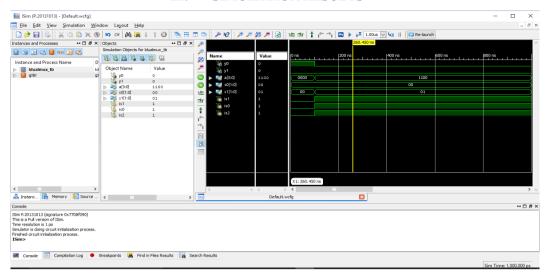

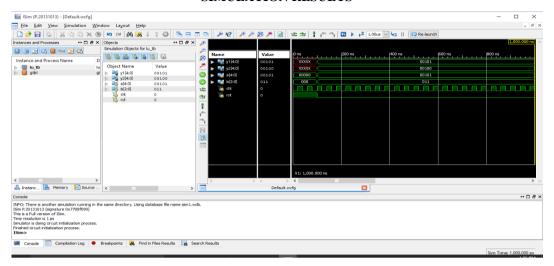

#### IX. SIMULATION RESULTS

#### RTL DIAGRAM

#### INTERNAL BLOCK DIAGRAM

#### SIMULATION RESULTS

#### Comparison Table.

|          | AREA   |      |       | DELAY(ns)  |

|----------|--------|------|-------|------------|

| SYSTEM   | SLICES | LUTS | IOB's | DELAT(IIS) |

| EXISTING | 112    | 202  | 27    | 20.11ns    |

| PROPOSED | 2      | 4    | 8     | 5.895ns    |

#### X. **CONCLUSION**

The Propose incipient hybrid CLB architecture containing MUX and logical elements and display the techniques for efficiently mapping to these architectures. Operation of LUT payoff more power preserving and area preserving nature with monetary value benefits. A coalescence of MUX: LUT engenders prosperous power consumption and size reductions schemas in single unit.

#### **FUTURE SCOPE**

Proposed scheme guarantees the size and nature of the LUT MUX in more efficient manner, however in future this work is elongated to interconnect many features, which are increasingly the ascendant contributor to delay, area and energy consumption in CMOS digital circuits. The implementation surmounts several inhibitions found in precedent implementations published so far, such as the desideratum for special features in the CMOS process or magnate-hungry present mode cells.

#### REFERENCES

- J. Rose et al., "The VTR project: Architecture and CAD for FPGAs from verilog to routing," in Proc. ACM/SIGDA FPGA, 2012, pp. 77-

- Y. Hara, H. Tomiyama, S. Honda, and H. Takada, "Proposal and quantitative analysis of the CHStone benchmark program suite for practical Cbased High-level synthesis," J. Inf. Process., vol. 17, pp. 242-254, Oct. 2009.

- A. Canis et al., "LegUp: High-level synthesis for FPGA-based processor/accelerator systems," in Proc. ACM/SIGDA FPGA, 2011,

- E. Ahmed and J. Rose, "The effect of LUT and cluster size on deepsubmicron FPGA performance and density," IEEE Trans. Very  $Large\ Scale\ Integr.\ (VLSI),\ vol.\ 12,\ no.\ 3,\ pp.\ 288-298,\ Mar.\ 2004.$

- J. Rose, R. Francis, D. Lewis, and P. Chow, "Architecture of fieldprogrammable gate arrays: The effect of logic block functionality

- on area efficiency," IEEE J. Solid-State Circuits, vol. 25, no. 5, pp. 1217-1225, Oct. 1990.

- H. Parandeh-Afshar, H. Benbihi, D. Novo, and P. Ienne, "Rethinking 6. FPGAs: Elude the flexibility excess of LUTs with and-inverter cones," in Proc. ACM/SIGDA FPGA, 2012, pp. 119-128.

- J. Anderson and Q. Wang, "Improving logic density through synthesisinspired architecture," in Proc. IEEE FPL, Aug. /Sep. 2009, pp. 105-111.

- 8. J. Anderson and Q. Wang, "Area-efficient FPGA logic elements:

- rchitecture and synthesis," in Proc. ASP DAC, 2011, pp. 369–375. J. Cong, H. Huang, and X. Yuan, "Technology mapping and architecture evalution for k/m-macrocell-based FPGAs," ACM Trans. Design Autom. Electron. Syst., vol. 10, no. 1, pp. 3-23, Jan. 2005.

- Y. Hu, S. Das, S. Trimberger, and L. He, "Design, synthesis and evaluation of heterogeneous FPGA with mixed LUTs and macrogates," in Proc. IEEE ICCAD, Nov. 2007, pp. 188-193

- 11. I. Kuon and J. Rose, "Measuring the gap between FPGAs and ASICs," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 26, no. 2, pp. 203-215, Feb. 2007.

- K. Karplus, "Amap: A technology mapper for selector-based fieldprogrammable gate arrays," in Proc. 28th ACM/IEE DAC, Jun. 1991, pp. 244-247.