T. Hemalatha, B.N.Manjubhargavi, G.Naganjali

Abstract: The bit size of the data length process depends on the clock speed operation .the clock speed increases with the bit size of the data length .but this increases deal in the circuit to overcome this pipeline and parallel processing is used. This will increase the performance of the circuit with the advancement of the high speed technology the data length process per clock is increasing rapidly from Intel 1 intel20 to Intel series. Adder is an important adder structure design which uses parallel and pipelining scheme are RCA and SFA. To design these adders we need high speed processing digital electronic circuit which must be high speed and low power. There are various types of logic families which we are discuss in this paper.

From static to dynamic circuit design why dynamic is faster than static. and various types of dynamic circuit design structure this paper basically focus on constant delay logic style and why it is superior to other dynamic structures such as domino logic dynamic logic np CMOS logic, C2MOS logic ,NORA CMOS logic design, Zipper CMOS, FTL logic.

#### I. INTRODUCTION

A machines performance of the product and its IPC commands in step with cycle and clock frequency. A nuclear activity is done b contemporary machines of dynamic training booking rationale giving up IPC b pipelining this trustworthiness we will execute subordinate directions in back to back cycles by method for disposing of its capacity.

Pipelining isn't b relinquishing clock recurrence to perform nuclear activity in a solitary clock cycle. Processors are being worked with more profound pipelines to accomplish more elevated amounts of execution. From the previous two many years of the quantity of pipeline stages has developed from 1(intel286) to 5(Intel 486)to 10 (Intel Pentium pro), to 20(Intel Willamette).

As processors endeavor to abuse more parallelism, this development in pipeline profundity will increment ceaselessly. A Deeper pipeline will increase latency with ever additional level latency is the time required for a sign to propagate thru the stages of the pipeline from start to finish. Typically a pipelined device requires extra sources (circuits factors, processing devices, pc memory and so forth.,) than one which executes one batch at a time, due to the fact its levels cannot reuse the sources of a preceding stage. Moreover pipelining ma increases the time it takes for an instruction to finish.

#### II. PIPELINING & PARALLEL PROCESSING

By sending the water proceed without holding up the water in the pipe to be out, it will prompts a decrease in the basic way, either its Will build the clock velocity(or inspecting speed) or diminishes the quality admission at indistinguishable term in a DSP framework

more than one O/P are enlisted in parallel in a clock length the staggering testing pace is improved by the degree of parallelism the degree of parallelism increments by utilizing the incredible inspecting pace and furthermore can used to diminish the quality admission if some continuous programming requires a faster info expense (design charge) at that point this immediate structure can't be used in this circumstance the basic way might be diminished by both pipe covering or parallel handling

PIPELINING: lessens the incredible significant course by presenting channel covering locks close by the basic records way , which diminishes the ground-breaking significant bearing.

PARALLEL PROCESSING: by reproducing hard product the testing cost will increment with the goal that various information sources might be prepared in parallel and various yields can be created at the indistinguishable time through the parallel handling.

Parallel handling and pipe lining procedures duals each extraordinary them two exploit simultaneousness accessible in the calculation in remarkable strategies.

## III. PIPE LINING AND PARALLEL PROCESSING FOR LOW POWER

We have basic points of interest of the use of pipe covering and parallel preparing - higher speed and lower vitality utilization

- \* this procedures can be utilized for bringing down the power utilization, while example speed does now not have any desire to be improved

- \* two significant recipes: registering the engendering delay Tpd of CMOS circuit

delay Tpd of CMOS circuit

$$T_{pd} = \frac{C_{charge}V_o}{k(V_O - V_c)^2}$$

#### Revised Manuscript Received on September 14, 2019.

T. Hemalatha, Anurag group of institutions, Hyderbad, Telangana, India.(Email: hemathalla@gmail.com)

**B.N.Manjubhargavi**, Anurag group of institutions, Hyderbad, Telangana, India.(Email: manjubhargaviece@cvsr.ac.in)

**G.Naganjali**, Anurag group of institutions, Hyderbad, Telangana, India.(Email: gnaganjali@gmail.com)

$\mathcal{C}_{charge}$ : The capacitance to be charged or discharged in a unmarried clock cycle. Computing the strength consumption in CMOS circuit.

$P_{CMOS} = C_{total}.V_0^2.f$

$C_{charge}$ : The total capacitance of the CMOS circuit PIP.

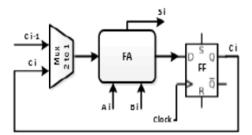

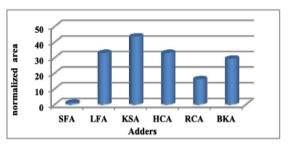

Overhead. Han-Carlson viper (HCA) is a total of BKA and KSA to diminish the unpredictability and make a tradeoff among region and deferral with log2N +1 practical insight stages. Another prefix viper which has negligible good judgment force (log2N) is alluded to as Lander-Fisher snake (LFA). In this engineering, a couple of hubs have exceptionally high fan-outs (up to N/2) to decrease the area and this could debase the performance. Serial full snake (SFA) is an essential full viper that is mixed with a flip-failure to use the viper unit at various check cycles in time-serialized swell convey way (Fig. 1) and the quantity of clock cycles that it takes is indistinguishable from the assortment of bits [5].

Fig. 1. Single-bit full adder in combination with a flip-flop to do *n*-bit addition sequentially at different clock cycles.

TABLE I

PERFORMANCE MEASUREMENT OF DIFFERENT

CONFIGURATIONS AT 0.3 V

| Configuration               | RCA     | SFA16  | Pipelined  | Parallel  |

|-----------------------------|---------|--------|------------|-----------|

|                             |         |        | RCA        | SFA16     |

|                             |         |        | (16stages) | (16units) |

| Area (um²)                  | 179     | 11.2   | 179        | 179       |

| Energy(10 <sup>-18</sup> J) | 15727.3 | 6128.6 | 98057.6    | 98057.6   |

| Throughput(MOPS)            | 4       | 7.1    | 114        | 114       |

| Frequency(MHz)              | 4       | 114    | 114        | 114       |

| Latency(ns)                 | 246.3   | 140.5  | 140.5      | 140.5     |

| Energy/Throughput           | 3932    | 863    | 860        | 860       |

Fig. 2. Area results normalized to SFA in 90-nm CMOS.

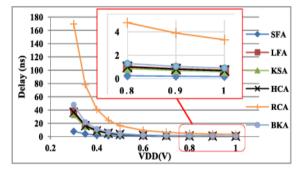

Fig. 3. Critical path delay of different adder structures in 90-nm CMOS.

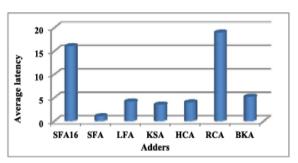

Fig. 4. Average of maximum latency at different voltages to do 16-bit addition for different voltages normalized to SFA.

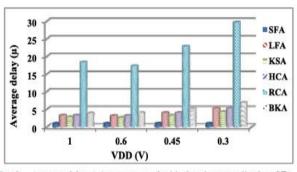

Fig. 6. Average delay  $(\mu)$  parameter of critical paths normalized to SFA.

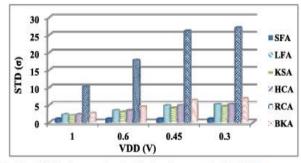

Fig. 7. STD  $(\sigma)$  parameter of critical paths normalized to SFA.

Simulation effects and analysis affirm that, SFA has smaller region, much less timing fluctuations, and the highest operating frequency, and its throughput is much like RCA. Utilizing SFA in parallel architecture or pipelined model of RCA improves the throughput except the power performance and version resistance. Therefore, so as to decrease the variant outcomes and to growth the throughput/performance of design, we want to apply deeper pipelines consisting of systolic arrays or massively parallel designs together with pics processing unit systems with less difficult constructing blocks. Increasing the pipeline depth in a design causes to break the paths into shorter sections to increase the throughput and decrease variations. Simpler computational building blocks consume lower energy and observe lower performance variations too. Finally, we conclude that utilizing such blocks in a massively parallel architecture is another way to compensate the process variation effects and lower the frequency uncertainty plus lowering timing fluctuations due to process variations [5].

#### IV. DYNAMIC LOGIC STRUCTURE

Dynamic presence of mind is impermanent (brief) in that yield levels will keep on being substantial best for a positive timeframe, static rationale keeps its yield arrange inasmuch as power is connected • Dynamic practical insight is regularly accomplished with charging and specifically releasing capacitance (i.e., Capacitive circuit hubs) -Precharge clock to expense the capacitance – Evaluate clock to release the capacitance depending on state of sound judgment inputs.

- Advantages over static rationale:

- Avoids copying rationale multiple times as every N-tree and P-tree, as a rule CMOS.

- Typically might be used in exceptionally exorbitant in general execution applications.

- Very simple consecutive memory circuits; amiable to synchronous sound judgment.

- High density viable Consumes less electricity (in a few instances).

- Disadvantages as compared to static common sense:

- Problems with clock synchronization and timing.

- Design is extra tough

High overall performance, power- green common sense style has continually been a popular studies topic inside the subject of very massive scale included (VLSI) circuits due to the non-stop demand of ever increasing circuit operating frequency. Reduction of power in compromise with performance of the circuit is the great interest of area for analog and digital electronics engineer. There are various designing techniques for digital circuits are proposed in the last two decades which optimizes static and dynamic losses of the electronic circuits either using dual threshold transistor or dual voltage supply[6].

There Are many exclusive logic circuit design techniques as CMOS, Bi CMOS, NMOS, Pseudo NMOS, differential cascade voltage swing common sense(CVSL), pass transistor common sense, dynamic CMOS common sense, Domino logic e.T.C [7,8]. High in general execution, control green rationale design has consistently been a famous examinations point inside the region of exceptionally huge scale joined (VLSI) circuits due to the relentless interest of regularly expanding circuit working recurrence. The development of the dynamic sound judgment in 80s is one of the answers for this solicitation since it enables architects to uphold over the top execution circuit square, i.e., arithmetic rationale unit (ALU), at a working recurrence that conventional static and sidestep transistor CMOS rationale examples are hard to achieve. In any case, the general execution upgrade accompanies various costs, including marked down commotion edge, value sharing clamor, and higher quality scattering on account of higher realities action.

In all of above Domino logic normally used for excessive performance included circuits the blessings are rail-to-rail common sense swing, the small silicon vicinity, a small parasitic capacitance, system faults free operation and the good judgment will layout with a small wide variety of transistor counts compared CMOS logic layout. This advantage of Domino good judgment circuits are noise in circuit because of leakage modern-day and price sharing & fee distribution problem. Only non-inverting structures are feasible due to presence of inverting buffer and huge energy consumption as compared to CMOS good judgment layout. To lower the electricity consumption of Domino CMOS common sense a new logic family named as feed thru good judgment (FTL) is proposed.

In this approach the output is evaluated earlier than all of the inputs are legitimate (active) the use of Domino good judgment. This feed through increases the performance of Domino logic, both it'll be combinational or sequential, are the risks of Domino good judgment are completely diminished using this good judgment. The dynamic common sense uses high voltage deliver for logic assessment and low deliver voltage for clocking dynamic circuit. This will increases static power loss in dynamic circuit.

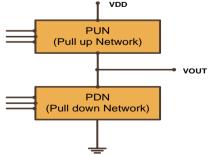

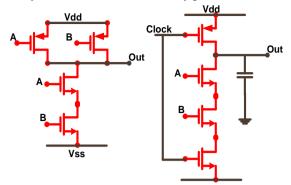

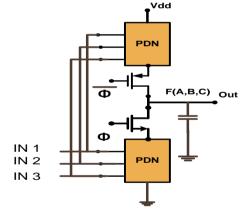

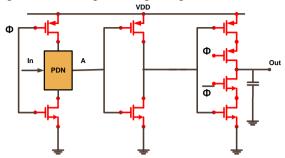

#### STATIC LOGIC: A.

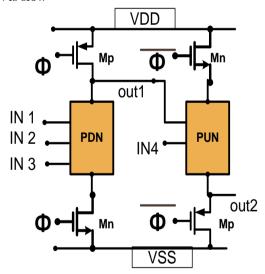

Static reliability is the most extraordinary for the most part used sound judgment style in CMOS age and its chief structure as showed up in Figure 1. It includes a NMOS pull-down system (PDN) and a PMOS pull-up framework (PUN). The central matters of enthusiasm of static basic leadership capacity are healthiness, low control dissipating unequivocally at uninformed interest issue, and adequate all things considered execution without a static imperativeness dispersal. Its most specific limit is that at some irregular time, the entryway yield is related with both VDD and GND by methods for a low-check way.

Figure 2. Static Logic structure

While this one of a kind guarantees good judgment's power, it's

& Sciences Publication

Published By:

likewise a top notch downside in light of the fact that static CMOS requires each NMOS and PMOS transistors on each enter. During a falling yield progress, PMOS transistors do never again make commitments to the draw down change forefront anyway handiest include sizable capacitance. Thus, static CMOS has an exceedingly huge intelligent exertion and spot punishment and is drowsy when upholding muddled rationale articulation which incorporates four-input XOR.

The PDN and PUN are completed the utilization of NMOS and PMOS gadgets because of the reality they can skirt strong rationale "0" and "1" separately. PMOS contraptions are regularly evaluated occasions bigger than NMOS devices to give same upward push and fall defer because of abatement opening versatility.

A. Subsequently, PMOS transistors must be up evaluated 4 cases greater than NMOS transistors to get comparable upward push and fall delay for the two-input NOR gateway. The up-sized PMOS transistors make duties input capacitance for the two advances, while simply helping the upward drive put off. In such way, PMOS contraptions neither ascent as the region bottleneck for static CMOS sound judgment style while realizing NOR gateway (PMOS gadgets in social affair). In addition, the upestimating approach offers obscured rising put off headway because of self-stacking sway, for the reason that additional channel capacitance brought by up-assessing typically balances general execution update contributed by better pull-up present day as a result of tremendous width device.

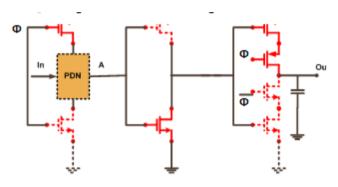

#### A. DYNAMIC LOGIC

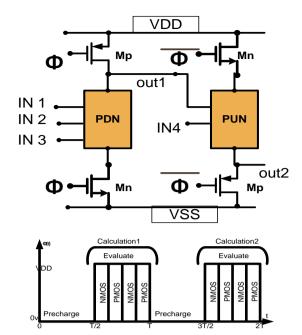

In coordinated circuit format, dynamic rationale (or every so often timed decision making ability) is a design philosophy in combinatory presence of mind circuits, specifically the ones actualized in MOS time. It is noticeable from the alleged static decision making ability by methods for misusing impermanent carport of records in stray and entryway capacitances It ended up prevalent in the Seventies and has obvious a most recent resurgence inside the format intemperate speed virtual hardware, workstation CPUs. Dynamic decision making ability circuits are regularly faster than static inverse numbers, and require less floor district, yet are more prominent hard to format. Dynamic trustworthiness has a higher switch cost than static rationale however the capacitive hundreds being flipped are littler so the general vitality admission of dynamic rationale might be better or lower contingent upon various tradeoffs. Dynamic sound judgment is noticeable from so-alluded to as static decision making ability in that unique trustworthiness utilizes a check sign in its execution of combinational presence of mind circuits. The common utilization of a clock sign is to synchronize changes in consecutive rationale circuits. N dynamic rationale, there isn't constantly a system utilizing the yield high or low. In the greatest ordinary model of this thought, the yield is pushed high or low sooner or later of marvelous components of the clock cycle. During the time spans while the yield isn't by and large effectively pushed, its impedance makes it keep up a phase inside a couple of resistance assortment of the determined stage. Dynamic rationale requires a base clock rate quick adequate that the yield kingdom of every powerful door is utilized or invigorated before the rate inside the yield capacitance holes out adequate to reason the advanced country of the yield to substitute, sooner or later of the a piece of the clock cycle that the yield isn't as a rule effectively pushed.

Figure 3. Dynamic Logic structure

The dynamic trustworthiness circuit calls for two phases. The principal segment, while Clock is low, is known as the arrangement fragment or the precharge segment and the subsequent stage, when Clock is intemperate, is known as the assessment portion. In the arrangement stage, the yield is driven exorbitant genuinely (independent of the estimations of the information sources An and B). The capacitor, which speaks to the heap capacitance of this entryway, ends up charged. Since the transistor at the most minimal is killed, it's far unrealistic for the yield to be pushed low sooner or later of this stage. During the assessment stage, Clock is over the top. In the event that An and B are additionally exorbitant, the yield will be pulled low. Something else, the high (because of remains the capacitance). Dynamic sound judgment has some limit inconveniences that static presence of mind does not. For example, if the clock pace is basically excessively continuous, the yield will rot too fast to even consider being useful. Likewise, the yield is legitimate for part of each clock cycle, so the gadget connected to it should design it synchronously at some phase in the time that it's far substantial. Likewise, while each An and B are extreme, so the yield is low, the circuit will siphon one capacitor-heap of charge from Vdd to floor for each clock cycle, with the guide of first charging after which releasing the capacitor in each clock cycle. This makes the circuit (with its yield identified with an inordinate impedance) less green than the static rendition (which hypothetically should now not allow any present day to stream other than through the yield), and while the An and B information sources are ordinary and both high, the dynamic NAND entryway utilizes quality in rate to the clock charge, as extensive on the grounds that it abilities effectively. The power scattering can be limited by methods for keeping up the heap capacitance low, anyway this in flip diminishes the most process duration, requiring a higher least clock recurrence; the better recurrence at that point will expand power consumption by utilizing the connection simply noted. In this manner, it's miles impractical to diminish the inactive quality admission (while the two sources of info are intemperate) underneath a

specific limitation which gets from a balance among clock pace and burden capacitance [11].

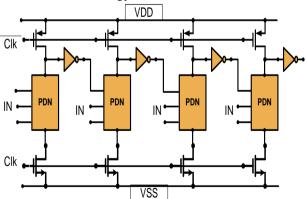

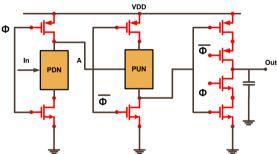

#### V. DOMINO LOGIC STRUCTURE

Domino presence of mind is a CMOS-based advancement of the dynamic ordinary experience strategies principally dependent on both PMOS and NMOS transistors. It lets in a rail-to-rail practical insight swing. It ended up better than pick up the pace circuits. In powerful sound judgment, an issue emerges while falling one entryway to the consequent. The precharge "1" United States of America of the essential door may furthermore also in light of the fact that the subsequent one entryway to release forthright, sooner than the essential door has arrived at its right state. This utilizes up the "precharge" of the subsequent door, which can't be reestablished till the resulting clock cycle, so there might be no recovery from this blunder In request to course powerful rationale entryways, one arrangement is Domino Logic, which fits a typical static inverter among reaches. While this may appear to vanquish the component of dynamic sound judgment, because of the reality the inverter has a pFET (one of the crucial dreams of Dynamic Logic is to avoid pFETs wherein feasible, because of pace), there are thought processes it without a doubt functions admirably. To begin with, there might be no fanout to more than one pFETs; the dynamic door associates with precisely one inverter, so the entryway remains extremely quick. Moreover, for the thought process that inverter interfaces with least complex nFETs in unique typical sense doors, it also can be quick. Second, the pFET in an inverter can be made littler than in a couple of styles of regular feel doors.

In Domino practical insight course state of a few levels, the appraisal of every degree swells the accompanying stage assessment, much the same as a domino falling in a steady progression. When fallen, the hub states can't return to "1" (till the resulting clock cycle) basically as dominos, when fallen, can't ascend, defending the call Domino CMOS Logic. It stands out from various answers for the course inconvenience in which falling is hindered by utilizing tickers or other methodology.

Figure 4. Domino Logic structure structure

Logic capabilities of domino common sense: They have littler regions than customary CMOS rationale (as does all Dynamic Logic). Parasitic capacitances are littler with the goal that better working velocities are conceivable. Activity is liberated from glitches as each door could make best one change. Just non-rearranging frameworks are doable due to

the nearness of altering support. Charge conveyance can be a problem.

Advantage: PUN networks are fast

Disadvantage: Domino gates are non-inverting we need inversion for logical completeness

Figure 5. Domino Logic structure structure

Solution 2 np-CMOS

Disadvantages: NMh=Vtp and NMl=Vtn

Two phase clock PUN is slow

Figure 6. NP-CMOS Logic structure structure

Ripple in logic chains Calculations ripple down a logic chain np-CMOS Domino

We need to insert latches

Figure 7. NP-CMOS precharge/evaluation phase Logic structure structure

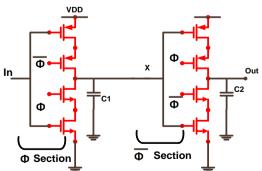

Inserting C2 MOS latches [13]:

Figure 8. C<sup>2</sup> MOS Logic structure

Review: C2 MOS master-slave flip-flop Dynamic flip flop with 2 clock phases

$\Phi$ =1: Evaluation mode

$\Phi$  section acts as an inverter,  $\overline{\Phi}$  section is off

Φ=0: Hold mode

$\overline{\Phi}$  Section acts as an inverter,  $\Phi$  section is off

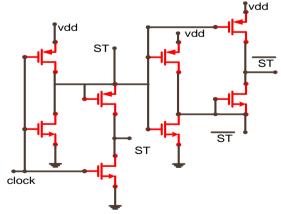

Figure 9. MOS Logic structure

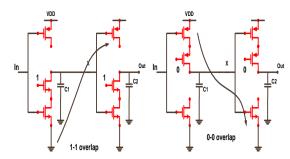

Review: C2 MOS is race free

C2MOS is insensitive to clock overlap

Cases: () or ()

No signal path between in and D for either case

Figure 10. MOS Logic structure

Preserving race free operation

To ensure that C2MOS is race free

Inter-latch static logic block must be non-inverting

Single inversion between master and slave causes

potential race

Figure 11. MOS Logic structure

Alternative: Embed the logic into the latch [13]

**Figure 12.**  $\mathbb{Z}^2$ MOS Logic structure C2MOS embedded latch/logic examples

Figure 13. C<sup>2</sup> MOS Logic structure

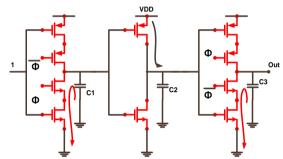

Dynamic logic between C2MOS latches [13] How do we add dynamic logic between master/slave stages?

Static logic blocks must still be non-inverting? What are the rules for dynamic logic block?

Single non-inverting static logic stage will cause race.

Figure 14. C<sup>2</sup>MOS Logic structure

Figure 15. C^2MOS Logic structure

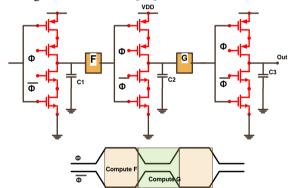

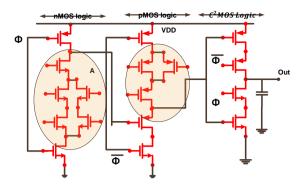

NO-Race CMOS:NORA CMOS [14]

\*Block comprises combinational logic and a C2MOS latch.

Logic is typically np-CMOS (dynamic)

Logic can be static or dynamic or both

Logic and latch are both in precharge or evaluation mode  $\Phi$ -module in NORA CMOS

Figure 16. MOS Logic structure

Figure 17.  $C^2$ MOS Logic structure NORA CMOS -module example

Figure 18. C<sup>2</sup>MOS Logic structure

NORA-CMOS design rules [14]

- Inputs to a dynamic  $\Phi n(\Phi p)$  block can only make a single 0 (1) transition during evaluation

- Use a fair quantity of static inversions between latch ranges

- ❖ The wide variety of static inversions between a latch and a dynamic logic block need to be even

- ❖ The wide variety of static inversions among dynamic common sense block and a latch ought to be even

- B. Dynamic and Compound Domino Logic: The advancement of the dynamic authentic judgment inside the 80s is one of the responses for the sales of reliably creating IC working pace since it empowers fashioners to put in power over the top execution circuit square, i.e., math reason unit (ALU), at a working repeat that the standard static and pass transistor CMOS regular feel styles are difficult to accumulate.

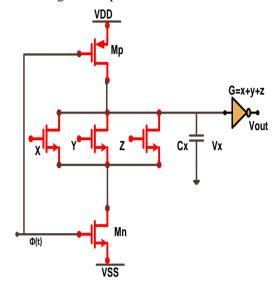

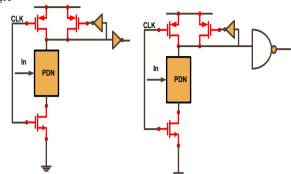

A summed up schematic of an incredible passage with footer CLK transistor is approved in Figure.

Figure 19. Schematic of (a) dynamic domino logic with a footer transistor and (b) FTL

The activity of dynamic fitting judgment is as per the going with: When CLK is low (precharge period), transistor M1 is on, and NMOS PDN is off an aftereffect of reality M2 is off. X is charged to VDD by techniques for transistor M1 and Out is kept up at GND.

Dynamic right judgment enters evaluation period while CLK moves to high.

In this condition, depending at the information plans reachable outcomes can take locale. In the event that NMOS PDN is off, X can be skimmed in light of the way that both M1 and PDN are off. Along these lines, a little PMOS escort (M3) is depended upon to battle contrary to the spillage and to help holding the voltage of focus point X at VDD. On the elective hand, in the event that NMOS PDN is on, by then X is quick released to GND and Out is invigorated to VDD through the inverter.

Dynamic premise doesn't have the issue of static quality dissipating because of reality while X is at GND (Out is at VDD), PMOS escort M3 will undoubtedly be off. Right when Out is released, it can't be charged again until the going with precharge length starts off front line. As necessities be the duties to the entryway of NMOS PDN could make everything thought about unbelievable one change at some phase in assessment. Positive, the particular attributes of dynamic practical learning are:

- 1. The basis trademark is associated with NMOS transistors best.

- 2. The amount of transistors for tangled common sense verbalization associated with dynamic decision making ability is basically lower than the static case.

- 3. Dynamic trustworthiness has faster exchanging pace since substantially less amount of transistors (particularly with no PMOS decision making ability transistors) adds to less stack capacitance.

- 4. It best devours dynamic vitality in light of the fact that no static contemporary course ever exists among VDD and GND. Be that as it may, the general vitality utilization might be generously higher than the static format due to the higher exchanging movement.

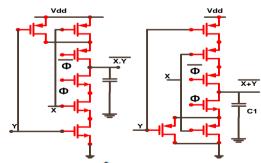

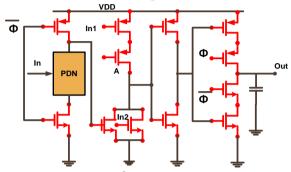

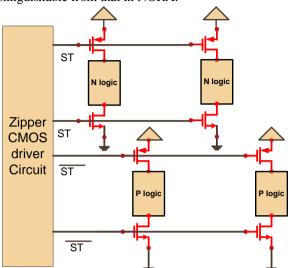

#### Zipper CMOS Structure

In Domino CMOS, each one of a kind stage is made out of Logic, and inside race conditions are emptied by strategy for use of a pad on the yield of every degree. On account of this progressively significant support, just non-changing sign can be gotten. NORA circuits clear up the race trouble by techniques for using a pipelined shape close by And CMOS and planned CMOS locks. Since there is no inverter on the yield of each stage, NORA circuits are commonly made out of less transistors than Domino CMOS circuits. It in like manner gives progressively conspicuous method of reasoning flexibility in the experience that each improving and non irritating sign can be gotten. Like most dominant plots, Domino CMOS and NORA circuits Be upset by sign corruption coming about in light of spillage current and worth redistribution. Various courses of action had been proposed to clear up the charge sharing issue in Domino CMOS circuits. These choices incorporate complex planning plans, extra transistors, or greater backings. The issue with uncertainty in view of fuss and spillage has not been tended to.

Zipper CMOS while it fuses every one of the upsides of Domino CMOS and NORA (as far as basic effortlessness and execution),

Zipper CMOS is naturally safe to the issues of frailty and charge-sharing. Area utilization is broadly better than in Domino CMOS and for all intents and purposes indistinguishable from that in NORA.

Figure 20. Zipper CMOS Structure

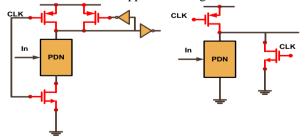

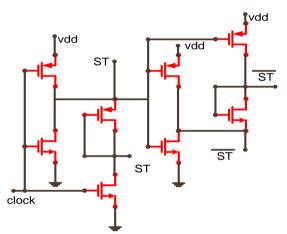

Figure 21. Zipper CMOS driver circuit 1

Figure 22. Zipper CMOS driver circuit 1

The fundamental Zipper CMOS structure is depicted in Fig. 1. It has two essential included substances: the Zipper Driver and exchange ? Furthermore, ? Dynamic basic leadership capacity squares. The Zipper Driver is constrained by methods for an unmarried territory clock, and it produces 4 strobe alerts, which drive all next N-P squares. During precharge, the yield of each? Square is over the top and that of each? Square is low. This guarantees the transistors Pushed through the yield of each groundbreaking affirmation may be off. During evaluation, the yield of each? Degree can encounter unprecedented one change from over the top to low and the yield of each? Level can experience best one advancement from low to over the top. This "astounded" style wherein markers multiply down every level of the circuit offers upward push to the call "Zipper CMOS." One head issue with this kind of circuit structure is that, inside each? Square and? Square, the inner centers may in addition rate blame for the yield center, achieving fake yield regards in explicit conditions

The general execution improvement accompanies various charges be that as it may, together with marked down commotion edge, value sharing clamor, and better vitality dissemination due to higher insights leisure activity. In a customary powerful rationale, a yield inverter is required between unique rationales to meet the realities monotonicity necessity and to guarantee right rationale evaluation. This not handiest will build the general postponement but rather the power consumption too. Two varieties of the dynamic sound judgment have been proposed to alleviate this inconvenience. NP domino, or otherwise called NORA domino, replaces this inverter with pre-released dynamic doors the utilization of PMOS sound judgment. In any case, NORA is exceptionally in danger of commotion and has never again been utilized impressively. Zipper domino attempts to obtain a similar target with the guide of a scarcely particular execution, however is never gigantic inside the VLSI venture. Moreover, dynamic rationale has normally lost its exhibition increase over static practical insight in view of the quickened self-stacking proportion in profound submicron age (65nm and under) because of the extra NMOS CLK footer transistor (Figure 1.12). This wonders has been exhibited in , which infers that at techniques comprehensive of 180nm and 130nm, the most helpful snake engineering is radix-four (5 transistors in arrangement, together with the footer transistor); in any case, radix-2 (3 transistors in gathering, for example, the footer transistor) setup transforms into extreme at 65nm age and past because of the reality the expanded self-stacking proportion has made radix-4 design more slow than radix-2, despite the fact that radix-2 design requires progressively number of reaches to complete the expansion.

Compound domino decision making ability (CDL) wherein dynamic and static CMOS entryways switching back and forth between one another mitigates the 2 previously mentioned issues and has end up being the most extreme mainstream sound judgment design in intemperate in general execution circuit square, i.E., sixty four-piece viper in front line essential preparing unit (CPU) . In this structure, the yield inverter is changed with a progressively confused altering static CMOS entryways (Figure 1.13),

i.E., NAND or NOR, to such an extent that the monotonicity necessity is fulfilled simultaneously as attempted complex decision making ability tasks without squandering the main inverter delay . Also, all the dynamic degrees other than the essential degree can be footless (the footer transistor is expelled) in CDL, as a result reduce the whole stack top with the guide of one. Be that as it may, this execution comes at the cost of duplicated.

Schematic of Dynamic Logic Vs. Compound Domino Logic

Figure 23. schematic of Dynamic Logic vs. Compound

Power utilization because of the immediate bearing current from VDD to GND at some point or another of the energize term. While CDL offers better typical execution and diminished quality utilization over natural static and dynamic not irregular sense style individually, its commotion edge is considerably debased as in a CDL structure, the yield of the dynamic not abnormal sense with no bluer is expected to drive the accompanying level through an all-inclusive interconnect and with various sign wires walking around parallel. The crosstalk of the abutting line can most likely ip the condition of the dynamic rationale, and results in false rationale evaluation. As a final product, more separation among wires by walking in parallel should be implemented in spreading out this kind of format at the cost of quickened wellknown line length. In the extraordinary case, control rails are set in among nearby wires to remove the crosstalk issue. This technique however, reasons huge execution debasement and quickened control consumption as a result of quickened parasitic capacitance. On account of this dependability issue, CDL is showed up as a less solid genuine judgment design and isn't mulled over.

#### VI. EVOLUTION OF CD LOGIC

A FTL Logic FTL regular feel Fig. 1(b) in CMOS time changed into first included a fundamental activity is as per the following: when CLK is over the top, the pre-release length starts and Out is dismantled right down to GND through M2. At the point when CLK transforms into low, M1 is on, M2 is off, and the door enters the appraisal length. In the event that contributions (IN) are appropriate judgment "1," Out enters the challenge mode wherein M1 and transistors in the NMOS pull-down network (PDN) are adventure present day simultaneously. In the event that PDN

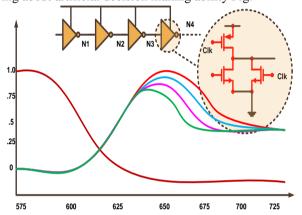

is off, at that point the yield quick ascents to ordinary experience "1." In this circumstance, FTL's basic course is ceaselessly a solitary pMOS transistor. In spite of its general execution advantage, FTL experiences diminished clamor edge, extra direct course present day, and nonzero ostensible low yield voltage, which are all by virtue of the conflict among M1 and nMOS PDN for the term of the assessment length. Besides, falling more than one FTL levels together to perform complex breathtaking judgment evaluates isn't sensible. Consider a chain of inverters finished in FTL fell all in all and pushed with the helpful asset of the utilization of the equivalent clock, as demonstrated in Fig.2. \_ When CLK is low, M1 of each confirmation actuates, and the yield of every degree starts offevolved to upward push. This will bring about artificial decision making ability Fig.

Figure 24. Simulated unwanted glitch at different logic depths in a chain of inverters implemented with FTL.

When CLK is low, M1 of every level activates,

Simulated undesirable glitch at one-of-a-kind common enjoy depths in a chain of inverters carried out with FTL. Opinions at even numbered (i.E., 2, four, 6, and so on.,) tiers thinking about that initially there may be no opposition between M1 and nMOS PDN due to the truth all inputs to nMOS transistors are reset to appropriate judgment "zero" in the course of the reset duration.

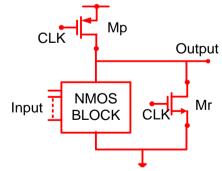

#### II. Conventional layout of FTL

Figure 25. Conventional design of FTL circuit

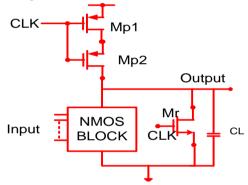

The essential structure of FTL is confirmed inside the above parent.1 wherein NMOS Mr is used for the reset the output to low degree paintings as pull-down and a PMOS Mp for pull-up the output node to high functionality Vdd. The Mp & Mr transistors is managed by using clock sign. As clk=1(reset phase) Mr flip ON and the output is

connected and the inverter is used to take away the circuit with exclusive consultative circuit, while clk=zero(evaluation section) Mr is have become OFF and the output node conditionally arrange as output steady with input NMOS block .

## VII. LOW ELECTRICITY MODIFIED FTL (LP-FTL)

The changed low electricity FTL circuit is shown in Figure 2 This circuit reduces VOL (output low voltage) thru the usage of a in addition PMOS pull up transistor MP2 in collection with MP1. The circuit operation is much like that of FTL. During reset segment i.E. When CLK = excessive, output node is pulled to floor (GND) through Mr as in FTL operation. But within the course of During evaluation phase output node costs thru Mp1 and Mp2. When CLK goes low (assessment phase) Mr is grew to become off and the output node evaluates in step with input block, to proper judgment high (VOH) or low (VOL). The use of Mp2 is to reduce the VOL, as in the path of evaluation phase at the same time as enter evaluated the output to common sense low, because of drain of Mp1 that's an awful lot less than VDD, the output node is going low compared to FTL circuit, this may reduce dynamic strength intake of circuit.

Figure. 26 NAND gate design using LP-FTL

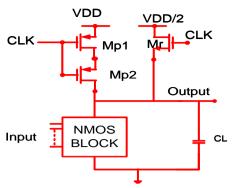

## VIII. HIGH TEMPO PROPOSED CHANGED FTL (HS-FTL) & RESULTS

To improve the speed of activity of LP-FTL circuit the reset transistor Mr is associated with VDD/2 as affirmed in Fig. . The activity of this circuit is as per the following, simultaneously as CLK =immoderate, the yield hub (OUT) will costs to the edge voltage VTH of Mr transistor. During assessment fragment with regards to enter hinder the yield hub just makes halfway progress from VTH to VOH or VOL due to Vth it is direct to travel to VOH or VOL. Since all through assessment section the yield hub (OUT) best makes fractional changes, this improves engendering discard. An inverter structured with the valuable asset of the utilization of HS-FTL is demonstrated in Figure.3

Figure. 27 NAND gate design using LP-FTL

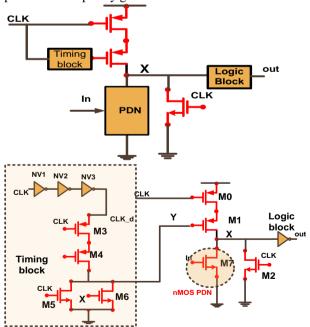

CD Logic To mitigate the above-referred to problems, CD not unusual experience is proposed with a schematic shown in Fig. 2.1(a). Timing block (TB) creates an adjustable window duration to reduce the static energy dissipation. Logic Block (LB) allows to reduce the undesirable glitch and additionally makes cascading CD logic viable. A buffer carried out in CD precise judgment with schematics of TB and LB is installed in Fig. 2.1(b). 1) CD Logic Operation: Fig. 2.2 depicts the corresponding CD suitable judgment timing diagram and flowchart. For simplicity, we count on that IN come from dynamic domino common feel gates. When CLK is immoderate, CD logic pre-discharges every X and Y to GND. When CLK is low, CD appropriate judgment enters the assessment period and three conditions can take location: particularly, the opposition, C-Q put off, and D-Q take away modes. The contention mode occurs even as CLK is low while IN stay at properly judgment "1." In this case, X is at a nonzero voltage degree which reasons Out to revel in a quick glitch. Experience a temporary glitch

Figure. 27 CD logic (a) block diagram and (b) buffer.

The time of this glitch is resolved through the area window width, this is resolved with the guide of the defer among CLK and CLK\_d. At the point when CLK\_d winds up unbalanced, and in the event that X remains low, at that point Y ascends to reasonable judgment "1," and turns off

M1. Thus the challenge term Is finished, and the transient glitch at Out is dispensed with. C-Q put off mode takes areas even as IN make a progress from unbalanced to low sooner than CLK turns out to be low. At the point when CLK transforms into low, X ascends to not surprising feel "1" and Y stays at not strange feel "zero" for the whole evaluation cycle. The push off is estimated by method for utilizing the falling edge of each CLK and Out: thusly the call C-Q delay. D-Q discard mode utilizes the pre-assessed normal for CD rationale to allow high-general execution activities. In this mode, CLK tumbles from over the top to low progress of time than IN travel, hence X at first ascents to a nonzero voltage arrange. As quick as IN end up basic feel "0," simultaneously as Y stays low, at that point X fast ascents to ordinary sense "1." A race situation exists for this situation among X and Y. In the event that CLK d rises a first rate bargain sooner than X and Y will go to right judgment "1," flip off M1, and result in a bogus top judgment evaluation. On the off chance that CLK d rises scarcely lesser than X, at that point Y will above all else upward push (along these lines scarcely turns off M1) anyway hence settle back to decision making ability "zero." CD practical insight can in any case play out the correct good judgment activity in this circumstance; in any case, its general execution is debased in light of M1's diminished advanced drivability.

Accordingly, it's miles fundamental to keep up an enough window width underneath procedure voltage-temperature (PVT) adaptations. Table I gives an abridgement of CD presence of mind's activities. Contrasted with FTL, wherein the challenge goes on for the whole evaluation time frame, TB strongly decreases CD decision making ability's quality admission over the span of the challenge mode. The nearby window technique in the proposed CD entryway lets in originators to customize the window width for explicit practical insight articulations to obtain least quality scattering while now not giving up the exhibition. For instance, a several information NAND entryway will require a more drawn out window width than a NOR door as a result of the bigger internal capacitance due to the stacked Nmos transistors. Another increase of CD sound judgment is that the inward hub (X) is constantly connected to both VDD or GND, as a result making the heartiness of CD practical insight much the same as static decision making ability, other than during the dispute mode.CD presence of mind disposes of the issue of phony rationale assessment related with fell FTL. Consider a fell CD rationale framework, wherein the contributions to NMOS PDN are consistently at rationale "1" when initially getting into the assessment time frame, because of the reality X and Out are consistently pre-released and precharged to decision making ability "0" and "1," separately. Accordingly, while CLK is low, CD doors will typically first enter the contention mode and restrictively make a low-to-high change depending at the data sources. This isn't the situation for the main degree CD entryway, be that as it may, as there is no certification that the sources of info will ceaselessly be at rationale "1."

In various expressions, creators need to guarantee that the information sign to the essential CD door arrive sooner than the clock sign, for example work in C–Q defer mode handiest.

#### REFERENCES

- Keshab K. Parhi "VLSI Digital Signal Processing Systems: Design and Implementation" willy publication 1999.

- Jared Stark ,Mary D. Brown Yale N. Patt "On Pipelining Dynamic Instruction Scheduling Logic" Intel® Technology Journal | Volume 14, Issue 3, 2010.

- 3. M. Talsania and E. John, "A comparative analysis of parallel prefix adders," in Proc. Int. Conf. Comput. Design, Las Vegas, NV, USA, Jul. 2013, pp. 29-36.

- 4. B. Parhami, Computer Arithmetic: Algorithms and Hardware Designs. London, U.K.: Oxford Univ. Press, 2009

- Hamed Dorosti, Ali Teymouri, Sied Mehdi Fakhraie, and Mostafa E. Salehi "Ultralow-Energy Variation-Aware Design: Adder Architecture Study" IEEE Transactions On Very Large Scale Integration (VLSI) Systems, pp1063-8210 © 2015 IEEE.

- S. Vangal, Y. Hoskote, D. Somasekhar, V Erraguntla, J. Howard, G. Ruhl, V. Veeramachaneni, D. Finan, S. Mathew, and N. Borkar, "A 5-Ghzfloating point multiply-accumulator in 90-nm dual VT CMOS,"in Proc. IEEE Int. Solid-State Circuits Conf., San Francisco, CA, Feb.2003, pp.334-335.

- S. Mathew, M. Anders, R. Krishnamurthy, S. Borkar, "A 4 GHz 130 nm address generation unit with 32-bit sparse-tree adder core,"IEEE VLSI Circuits Symp., Honolulu, Hi, jun 2002, pp. 126-127.

- 8. R.K. Krishnamurthy, S. Hsu, M. Anders, B. Bloechel, B. Chatterjee, M. Sachdev, S. Borkar, "Dual Supply voltage clocking for 5GHz 130nm integer execution core," Proceedings of IEEE VLSI Circuits Symposium, Honolulu Jun. 2002, pp. 128-129.

- Y. Jiang, A.Al-sheraidah, Y. Wang, E.sha, J. Chung, A novel multiplexer based low-power full adder, IEEE Trans. Circuits Syst.-II,vol. 52, 2004, pp. 345-348.

- R. Zimmermann and W. Fichtner, "Low-power logic styles: CMOS versus pass-transistor logic," IEEE J. Solid-State Circuits, vol. 32, no. 7,pp. 1079-1090, Jul. 1997.

- R.Vijay & M. Damodhar rao "A Low Power 32-Bit Ripple Carry Adder Using Dynamic DML CMOS Logic Gates" nternational Journal of Research Volume 03 Issue 10 June 2016

- Ankita Sharma, .Divyanshu Rao and Ravi Mohan "Design and Implementation of Domino Logic Circuit in CMOS" Journal of Network Communications and Emerging Technologies (JNCET) Volume 6, Issue 12, December (2016)

- CMOS-Logic-Structure research eductaion research.unm.edu/jimp/vlsi/slides/chap5

- N. Goncalves and H. De Man, "NORA: A racefree dynamic CMOS technique for pipelined logic structures," IEEE J. Solid-State Circuits, vol. 18, no. 3, pp. 261-266, Jun. 1983.

- 15. C. Lee and E. Szeto, "Zipper CMOS," IEEE Circuits Syst. Mag., vol. 2,no. 3, pp. 10-16, May 1986.