# Design of Low Power Transceiver on Spartan-3 and Spartan-6 FPGA

Keshav Kumar, BishwajeetPandey, Amit Kant Pandit, Yousef A. Baker El-Ebiary, Salameh A. Mjlae, SamerBamansoor

Abstract—In this research work, a low power transceiver is designed using Spartan-3 and Spartan-6 Field-Programmable Gate Array (FPGA). In this work, a Universal Asynchronous Receiver Transmitter (UART) device is used as a transceiver. The implementation of UART is possible with EDA tools called Xilinx 14.1 and the results of the power analysis are targeted on Spartan-3 and Spartan-6 FPGA. The variation of different power of chips that are fabricated on FPGA for e.g., Input/Output (I/O) power consumption, Leakage power dissipation, Signal power utilization, Logic power usage, and the use of Total power, is observed by changing the voltage supply. This research work shows how the change in voltage influence the power consumption of UART on Spartan-3 and Spartan-6 FPGA devices. It is observed that Spartan-6 is found to be more power-efficient as voltage supply increases.

Keywords— Spartan-3, Spartan-6, Power, Voltage, Field-Programmable Gate Array (FPGA), Universal Asynchronous Receiver Transmitter (UART)

### I. INTRODUCTION

In the current scenario of the world, energy crisis across the globe accounts a very major significant problem. And the energy crisis and the shortage of natural resources like crude oil, coal, etc. in India affects the economy of the country [1]. Population growth and industrial development have led the global demand for a huge amount of energy. So in order to reduce the energy consumption, we are making a UART using FPGAs which consumes less amount of power. UART stands for Universal Asynchronous Receiver Transmitter which is used for serial communication of data. In UART only two wires are required for data transmission. Not only that no clock signals are required to drive UART. When the value of voltage is at the extreme, the UART produces less noise and interference and signal can travel a longer distance [2-3]. The voltage applied to UART plays a vital role in determining the chip's power that is fabricated on FPGA. From the universal power voltage equation  $P \propto$ V and P = VI, it is observed that power is based on voltage. Hence, in case of UART also, if the voltage supply is changed, then the input voltage (vccint) and thermal properties will change but the effective thermal resistance to air also known as ( $\Theta$ JA ( $^{\circ}$ C/W)) and Voltage supply for auxiliary logic (vccaux) and Voltage supply for I/O banks 25 (vcco25) remains same. Similarly, when the supply voltage is increased, then the maximum ambient temperature increases but the junction temperature decreases.

# II. RELATED RESEARCH DONE BY OTHER RESEARCHERS & METHODOLOGY

In [4], there is a UART based on asynchronous technology which consumes low power. In [5] authors by varying the frequency of FPGA designed an energy-efficient Arithmetic Logic Unit (ALU) which reduces clock and dynamic power consumption. In [6] authors using 45nm and 28nm FPGA designed an electron inducing single event upset at a nominal voltage value. In [7] authors have designed a method for analyzing the high-level utilization of FPGA power dissipation. In [8] an energy-efficient counter was designed by scaling voltage value on different FPGAs technology. In [9] authors have designed a modular feedback PID controllers system using FPGA technology. PID controllers help in saving power consumption. In [10] researchers designed an energy-efficient instruction register for green communication on FPGA. In [11] a low power frequency scaled and thermal-aware control unit design is implemented on FPGA. But in this project, we are making a UART which usage low power using Spartan-3 and 45nm Spartan-6 FPGA family.

### III. EXPERIMENTAL SECTION

The UART design was implemented on Xilinx14.1 ISE design Suite using Spartan-3 and Spartan-6 FPGA. The UART module is coded in Verilog HDL (Hardware Description Language). The voltage varies from 1.1*V* to 1.5 *V* in both FPGA and power variation is analyzed using X Power Analyzer tool. This implementation is done at a frequency of 1GHz. The ambient temperature of both FPGA is 25(°C) having the airflow of zero Linear Feet per Minute (LFM). Spartan-3 and 45nm Spartan-6 FPGA runs on speed grade of -5 and -3 respectively.

# IV. THERMAL BEHAVIOR OF SPARTAN-3 AND SPARTAN-6 FPGA.

Effective Thermal Resistance to air  $(\Theta JA (^{\circ}C/W))$  remains constant for both Spartan-3 and Spartan-6 FPGA as voltage rises from 1.1V to 1.5V. For Spartan-3 FPGA

**Keshav Kumar,** Gyancity Research Consultancy Pvt Ltd,Motihari, Bihar, India. (Email: thekeshavkumar1993@gmail.com)

**BishwajeetPandey**, Gyancity Research Consultancy Pvt Ltd,Motihari, Bihar, India. (Email: gyancity@gyancity.com)

Amit Kant Pandit,Shri Mata Vaishno Devi University (SMVDU), Katra, Jammu and Kashmir, India. (Email:amit.pandit@smvdu.ac.in)

Yousef A. Baker El-Ebiary, Faculty of Informatics and Computing, UniSZA, Malaysia. (Email: yousefelebiary@unisza.edu.my)

Salameh A. Mjlae, Balqa Applied University, Salt, Jordan. (Email: dr.s-mjlae@bau.edu.jo)

SamerBamansoor, Al-Madinah International University, Kuala Lumpur, Malaysia. (Email: samer.ali@mediu.edu.my)

Retrieval Number: L100610812S219/2019©BEIESP DOI: 10.35940/ijitee.L1006.10812S219

Revised Manuscript Received on 14 September, 2019.

effective thermal resistance to air is 37.0 (ΘJA (°C/W)) and for Spartan-6 FPGA effective thermal resistance to air is 38.4 (ΘJA (°C/W)). Maximum ambient temperature (MAT) decreases and junction temperature increases for both FPGA when the voltage gets raised from 1.1V to 1.5V. Table 1 and Table 2 represents the change in thermal properties of FPGA due to the change in voltage supply.

Table 1. Thermal properties of Spartan-3 FPGA as voltage raises from 1.1V to 1.5V.

| Voltage      | Effective  | MAT (°C) | Junction     |

|--------------|------------|----------|--------------|

| Source       | Thermal    |          | Temperature. |

| (vccint) (V) | Resistance |          | (°C)         |

|              | (ΘJA       |          |              |

|              | (°C/W))    |          |              |

| 1.1          | 37.0       | 82.8     | 27.2         |

| 1.2          | 37.0       | 82.7     | 27.3         |

| 1.3          | 37.0       | 82.5     | 27.5         |

| 1.4          | 37.0       | 82.3     | 27.5         |

| 1.5          | 37.0       | 82.0     | 28.0         |

Table 2. Thermal properties of Spartan-6 FPGA as voltage raises from 1.1V to 1.5V.

| , oronge runses from 111 , to 110 , t |            |          |              |  |

|---------------------------------------|------------|----------|--------------|--|

| Voltage                               | Effective  | MAT (°C) | Junction     |  |

| Source                                | Thermal    |          | Temperature. |  |

| (vccint) (V)                          | Resistance |          | (°C)         |  |

|                                       | (ΘJA       |          |              |  |

|                                       | (°C/W))    |          |              |  |

| 1.1                                   | 38.4       | 83.0     | 27.0         |  |

| 1.2                                   | 38.4       | 82.9     | 27.1         |  |

| 1.3                                   | 38.4       | 82.7     | 27.3         |  |

| 1.4                                   | 38.4       | 82.5     | 27.5         |  |

| 1.5                                   | 38.4       | 82.3     | 27.7         |  |

# V. POWER ANALYSIS

# A. Power Dissipation at Spartan-3 FPGA.

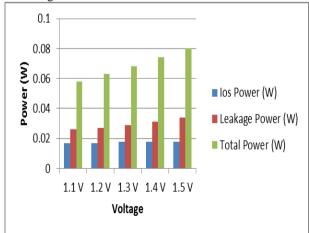

For voltage 1.1V and 1.2V, I/O power dissipation is 0.017W and for 1.3V, 1.4V and 1.5V I/O power consumption is 0.018W. Leakage power increases as 0.026W, 0.027W, 0.029W, 0.031W and 0.034W respectively as voltage is raised from 1.1V to 1.5V. Therefore, the total power consumption also gets increased as 0.058W, 0.063W, 0.068W, 0.074W and 0.080W respectively for increment in voltage from 1.1 V with a step size of 0.1 V to 1.5 V. The voltage and power variation are shown in figure 1.

Figure 1. Power Consumption at Spartan-3 FPGA.

B. Power Utilization at Spartan-6 FPGA.

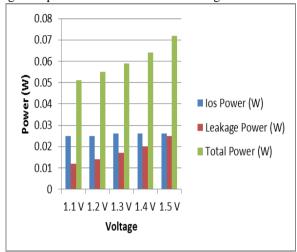

For voltage 1.1V and 1.2V, I/O power utilization is 0.025W and for 1.3V, 1.4V and 1.5V I/O power usage is 0.026W. Leakage power increases as 0.012W, 0.014W, 0.017W, 0.020W and 0.025W respectively as voltage is increased from 1.1V to 1.5V. Therefore, the total power consumption also gets increased as 0.051W, 0.055W, 0.059W, 0.064W and 0.072W respectively for increment in voltage from 1.1V with a step size of 0.1 V to 1.5V. The voltage and power variation are shown in figure 2.

Figure 2. Power Usage at Spartan-6 FPGA.

# VI. RESULTS

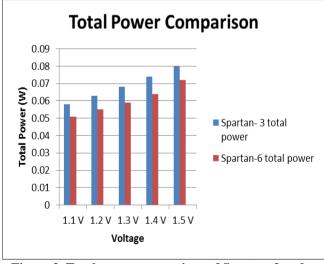

As compared to Spartan-6 FPGA, there is a rise of 116.667% of the total power usage for Spartan-3 FPGA when the voltage supply is at 1.1V. The increment in total power consumption for Spartan-3 FPGA at voltage 1.2V, 1.3V and 1.4V is 14.545%, 15.254%, and 15.625% respectively. For 1.5V voltage the increment in the total power consumption of Spartan-3 FPGA is 11.111% as compared to 45nm Spartan-6 FPGA. Figure 3 shows the total power comparison of the older Spartan-3 and the newer Spartan-6 FPGA.

Figure 3. Total power comparison of Spartan-3 and Spartan-6 FPGA.

#### VII. CONCLUSION

The implementation of UART is done on Xilinx 14.1 ISE EDA tool and the results are targeted on Spartan-3 and Spartan-6 FPGA devices. The UART module is coded in Verilog HDL. In this work power consumption of the device is analyzed at a different value of voltage ranging from 1.1V to 1.5V. It is observed that as voltage increases the total power consumption of both FPGA also increases. The device consumes low power if the supply voltage is low, therefore it is concluded that Spartan-6 FPGA is most power-efficient device for UART as compared to Spartan-3 FPGA.

#### REFERENCES

- 1. D. Nandy, "Energy Crisis of India: In Search of New Alternatives." *Journal of Buisness and Financial Affairs* 5, no. 4 (2016): 1-6.

- K. Kumar, et.al "Effect of Different Nano Meter Technology-Based FPGA on Energy Efficient UART Design." In 2018 8th International Conference on Communication Systems and Network Technologies (CSNT), pp. 1-4. IEEE, 2018.

- K. Kumar, et.al. "Low Power UART Design Using Different Nanometer Technology-Based FPGA." In 2018 8th International Conference on Communication Systems and Network Technologies (CSNT), pp. 1-3. IEEE, 2018.

- D. Bhadra, V. S. Vij, and K. S. Stevens. "A low power UART design based on asynchronous techniques." In Circuits and Systems (MWSCAS), 2013 IEEE 56th International Midwest Symposium on, pp. 21-24. IEEE, 2013

- B. Pandey, J. Yadav, M. Pattanaik, and N. Rajoria.

"Clock gating based energy efficient ALU design and implementation on FPGA." In Energy Efficient Technologies for Sustainability (ICEETS), 2013 International Conference on, pp. 93-97. IEEE, 2013.

- M.J. Gadlage, et.al. "Electron-induced single-event upsets in 45-nm and 28-nm bulk CMOS SRAM-based FPGAs operating at nominal voltage." *IEEE Transactions on Nuclear Science* 62, no. 6 (2015): 2717-2724.

- V. Degalahal, and T. Tuan. "Methodology for high-level estimation of FPGA power consumption." In Proceedings of the 2005 Asia and South Pacific Design Automation Conference, pp. 657-660. ACM, 2005.

- 8. T. Gupta, G. Verma, A. Kaur, B. Pandey, A. Singh, and T. Kaur. "Energy-Efficient Counter Design Using Voltage Scaling On FPGA." In Communication Systems and Network Technologies (CSNT), 2015 Fifth International Conference on, pp. 816-819. IEEE, 2015.

- 9. Y. F. Chan, M. Moallem, and W. Wang. "Design and implementation of modular FPGA-based PID controllers." *IEEE transactions on Industrial Electronics* 54, no. 4 (2007): 1898-1906.

- S. M T. Siddiquee, K. Kumar, B. Pandey, A. Kumar," Energy Efficient Instruction Register for Green Communication", International Journal of Engineering and Advanced Technology (IJEAT), Volume-8, Issue-2S2, January 2019.

- K. Kumar, et.al. "Power Efficient Frequency Scaled and Thermal-Aware Control Unit Design on FPGA", International Journal of Innovative Technology and Exploring Engineering (IJITEE), Vol. 8, Issue-9S2, July 2019.

#### AUTHORS PROFILE

Keshav Kumar is pursuing his Master of Engineering in the field of Cyber Security and FPGA from Chitkara University, Punjab, India. He did his B.Tech in Electronics and

Communication Engineering from Rajasthan Technical University, Kota, India. His area of interest is the implementation of security algorithms on FPGA, power-efficient device on FPGA and green communication. He has worked with researchers of three different countries in the field of Low Power VLSI design on FPGA and Energy Efficient devices for Green Communication.

**BishwajeetPandey** is a cofounder of Gyancity Research Lab. Gyancity Research Lab organizes three conferences (ICGCET.ORG, RTCSE.ORG, IMCES.TECH) across the globe.

He has completed his PhD in CSE from GSSI, Italy. He has worked as Asst. Professor in Department of Research at Chitkara University, Junior Research Fellow (JRF) at South Asian University. He has completed Master of (IIIT Gwalior) in CSE with Technology Specialization in VLSI, Master of Computer Application, R&D Project in CDAC-Noida. He has authored and coauthored over 135 paper available Profile:https:// his Scopus www.scopus.com/authid/detail.uri?authorId=57203 239026. He has 1345 Citation according to his Profile: Scholar https://scholar.google.co.in/citations?user=UZ\_8yA MAAAAJ&hl=ens.

Dr. AMIT KANT PANDITIS an Associate Professor in Department of Electronics and Communication Engineering at Shri Mata Vaishno Devi University Katra, India. He has teaching experience of approx.

17 years. His area of interest are Multimedia Technology, Digital Signal Processing and VDTN.

# Design of Low Power Transceiver on Spartan-3 and Spartan-6 Fpga

Associate Professor Doctor

Yousef El-EbiaryWork at

Al-Madinah International

University, Malaysia.

Deputy of Faculty for

Postgraduate and

Scientific Research. Has over 9 years' experience as a senior lecturer in both the IT (Hons) and MIS (Hons) for degree and postgraduate levels. This role involved the writing design and validation of the programs and as they developed. In addition included extensive experience conferences organization, administrative works and some membership in several committees. He also serves as Dean of student affairs, working with students during their work based learning and developing, plus preparing and organize some community development services with them in local community. In terms of supervision he supervise both Ph.D.'s and Master Students, alongside working as a manager for research journal and reviewer as well. And has good experience scientific publication and international conferences.

Salameh A. Mjlae, works at Al-Balqa Applied University, Salt, Jordan. He has a deep interest in researching cloud computing, IT Effectiveness, IT Flexibility and information security aspect.

Samer Ali Bamansoor was born in Aden (Yemen) in 1983. He is a PhD student in the Faculty of Informatics and Computing at University

Sultan ZainalAbidin (UniSZA). His research centers on the effect of social commerce factors on user purchase behavior. He received B.S. in Information Technology at University of Aden, Yemen in 2007 and obtained M.S degree in 2015 from Asia Pacific University (APU), Malaysia. He is currently lecturer in Al Madinah International University in Malaysia. His research interests include Social Learning, E Learning, E commerce, Social Commerce and MIS.