# Impact of Mole Fraction Variation on Nanoscale SiGe Hybrid FinFET on Insulator

# Vidhya Sagar G, VijayaKumar D

Abstract: This work investigates the performance of SiGe Hybrid JunctionLess FinFET (HJLFinFET) on insulator with different mole fraction x. The band gap difference for different mole fractions are explored. Impact of electrical characteristics and SCE of HJLFinFET are analyzed with fin width 10nm and varying gate length from 5nm-40nm for different mole fraction. Synopsys Sentaurus TCAD tool(sprocess and sdevice) are used in Device modelling and device simulation. Simulation results shows improvement in On current, DIBL and SS. For high performance application SiGe with mole fraction less than 0.3 at channel length less than 10nm are suitable because of the bandgap value is similar to silicon.

Keywords: SiGe, HJLFinFET, Subthreshold Slope (SS) and Drain Induced Barrier Lowering (DIBL), Short channel effects (SCE).

## I. INTRODUCTION

Performance limitations due to scaling has become more challenging in nanoscale regime. Due to which carrier velocity saturation, high field effects, short channel effects (SCE) of electrostatic origin such as DIBL, threshold voltage shift, subthreshold degradations are given more importance. Promising devices like FinFETs, Junction less transistors, HEMT devic shows better gate control which overcomes the effect of short channel effects compared to conventional MOSFETs[1]. Moreover various materials with strained silicon, compound materials and high k dielectric for gate stack are used on few pictorializations like gate all around and Silicon on Insulator for high carrier mobility and reduced SCE. Using high-K materials reduction in leakage current across junction is achieved due to large bandgap [2,3]. Materials like strained silicon increases mobility with increase in strain and also limits mobility enhancement due to lattice dislocation. Compound materials are defined with Mole fraction x which defines the amount of composition present in mixture of compound materials with a dimensionless quantity [4]. SiGe is a material used as an alternative to Si because of its compatibility with standard Si technology. The band structure of SiGe is strongly impacted by strain, dependency of Ge mole fraction on SiGe for high mobility due to high stress is studied [6]. Hetero-structure models and super lattice buried channel investigation are studied [7-9]. SOI technology is employed to reduce SCE as oxide layer isolates the channel from the bulk. The device is grown on oxide layer for better electrostatics. Moreover the

#### Revised Manuscript Received on September 14, 2019.

Vidhya Sagar, School of Electrical Engineering, VIT, Vellore, India Email: vidhyasagar.g@vit.ac.in

**Vijayakumar D,** School of Electrical Engineering, VIT, Vellore, India Email: vijayakumar.d@vit.ac.in

advantage of SiGe as device material, it equals the bandgap value with Si due to bandgap variation caused by the mole fraction x [4]. The lattice constant of Si is  $x=5.431^{0}$ A, Ge is  $x=5.658^{0}$ A and SiGe has 4.2% of lattice mismatch respectively [19, 20]. The mole fraction x value includes lattice match and lattice constant.

## II. MATERIAL AND METHOD & METHODOLOGY

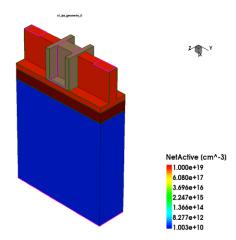

Fig. 1 depicts the 3D-schematic of n-type SiGe HJLfinFET on insulator with high-K spacer. Silicon material is used as substrate with boron doping and buried oxide material with SiO2 is deposited. SiGe is grown as an epitaxial layer on top of the oxide forming source and drain regions [10]. Uniform doping with zero doping gradient over the device represents junctionless transistor [5]. Junctionless transistors conducts with high φm that denotes the difference between the gate metal and channel material fully depletes the channel region [11-15]. To enhance better gate control over the channel and mobility, high-K spacer HfO2 is deposited. The device parameters of HJLFinFET are listed in table 1.

Fig. 1 SiGe Hybrid Junctionless FinFET with gate length 20nm and width 10nm.

Three dimensional (3D) device simulation are performed using Sentaurus device. For device simulation old-slotboom bandgap narrowing models are used due to high doping of the channel. Mobility degradation models such as doping dependency, high field saturation to account velocity saturation of charge carriers are included.[16-19]

Table 1. Device parameters and doping profiles

| Parameter                     | HJLFinFET                             |

|-------------------------------|---------------------------------------|

| Gate length(Lg)               | 20nm                                  |

| Fin height(H <sub>fin</sub> ) | 30nm                                  |

| Fin width(W <sub>fin</sub> )  | 10nm                                  |

| Equivalent oxide thickness    | 0.9nm(HfO <sub>2</sub> )              |

| Ultra-thin body thickness     | 6nm                                   |

| Spacer length                 | 10nm(HfO <sub>2</sub> )               |

| BOX thickness                 | 10nm                                  |

| Fin dopants(Arsenic)          | 1 X 10 <sup>19</sup> cm <sup>-3</sup> |

| Substrate dopants(Boron)      | 1 X 10 <sup>15</sup> cm <sup>-3</sup> |

| Gate metal work function      | 4.6eV-4.7eV                           |

### III. RESULT AND DISCUSSION

# A. Comparison of Transfer Characteristics

In this section, the DC performance of SiGe HJLFinFET is

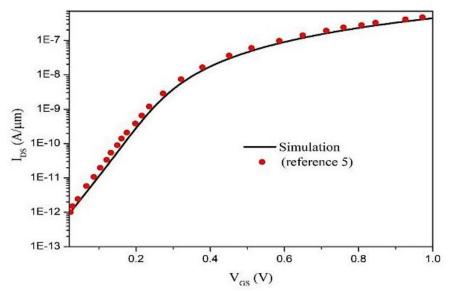

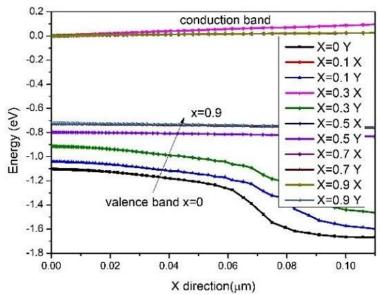

analyzed with varying channel length and temperature. Fig.2 represents the calibrated simulation of SOI junctionless FinFET and Hybrid FinFET at  $V_{TH} \approx 325 \text{mV}$  and the result are matched [5] Fig.3 exhibits the energy band gap over the device with mole fraction x=0, 0.1, 0.3, 0.5, 0.7 and 0.9 at threshold voltage of 300mV and channel length of 20nm. It is observed that band gap value decreases with increase in mole fraction. The energy band gap varies from 1.1eV to 0.6eV due to the germanium mole fraction in SiGe material. The difference between the conduction band and valence band of Si is EG=1.1eV. EG=1eV with mole fraction of x=0.1 and EG=0.6eV for mole fraction x=0.9, which indicates the composition of germanium in SiGe at 10% and 90%. The fermi energy is zero due to high doping concentration which is close to the conduction band an added advantage for the SiGe junctionless transistor.

Fig.2. IDS-VGS of Junctionless transistor calibrated at VDS=1V and Lg=1µm.

Fig.3 Energy band gap over the device for variation mole fraction.

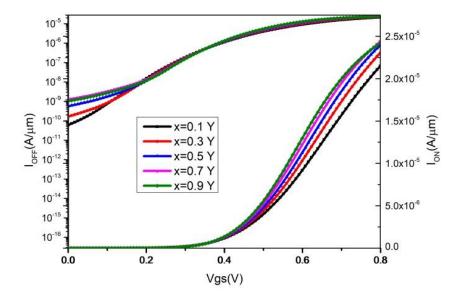

Fig.4 shows the influence of mole fraction variations on  $I_{ON}$  and  $I_{OFF}$  with gate voltage at channel length  $L_{\rm g}=20$ nm. The on current increases with increase in mole fraction at low gate voltage when gate voltage greater than 0.7, current

decreases with mole fraction 0.7 and 0.9. When gate voltage increases electric field tends to decrease. Off current decrease reduces the  $I_{\rm ON}/I_{\rm OFF}$  ratio.

Fig.4 On-current and Off current variation over SiGe mole fraction variations at  $L_g$ =20nm and  $V_{TH}$ =300mV.

# B. Transconductance and gate capacitance variation

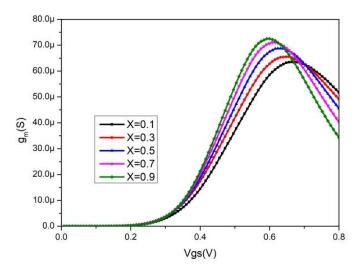

Fig. 6 shows the impact of transconductance over different mole fraction with channel length of 20nm. Transconductance which is considered as the figure of merit for analog applications decreases as the mole fraction increases. Maximum  $g_m$  of  $70\mu(S)$  is achieved with mole fraction x=0.9 with less gate voltage. As the gate

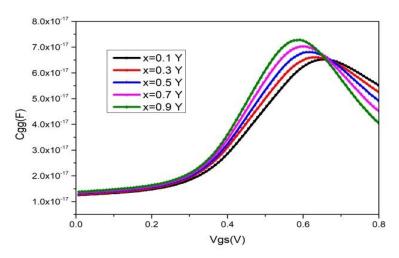

voltage increases gm decreases. Fig. 7 shows the gate capacitance impact over the mole fraction. Gate capacitance increases at low gate voltage and decreases at higher gate voltage as it directly proportional to dielectric constant. Gate capacitance decreases with increase in mole fraction.  $7x10^{-17}F$  is achieved with mole fraction 0.9 at low gate voltage.

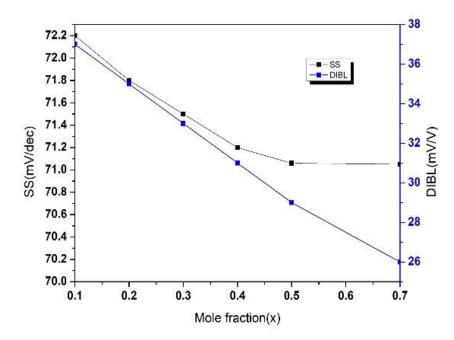

Fig.5 DIBL and SS over SiGe mole fraction variation at  $L_g$ =20nm and  $V_{TH}$ =300mV

Fig. 6 Transconductance with gate voltage for different mole fraction.

Fig.7 Gate capacitance with change in gate voltage for different mole fraction.

## C. Channel length variation

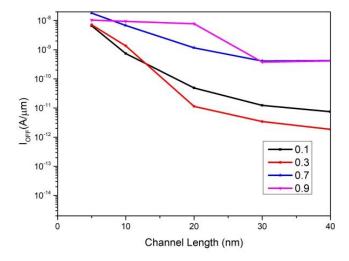

Fig. 8 shows the off current variations to different channel length with mole fraction x=0.1, 0.3, 0.7 and 0.9. It is evident that when channel length increases better off

current is achieved. Better  $I_{OFF}$  is obtained with mole fraction 0.1 when the channel length is less than 10nm. With germanium concentration of less than 30% in SiGe material better  $I_{ON}/I_{OFF}$  ratio is achieved.

Fig.8  $I_{OFF}$  variation to channel length with mole fractions x=01, 0.3, 0.7 and 0.9.

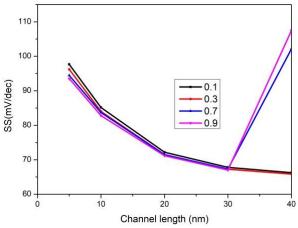

Fig.9 SS variation to channel length with varying mole fraction

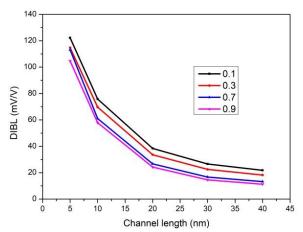

Fig.9 and 10 shows the impact of SS and DIBL of different mole fractions. SS decreases with increase in mole fraction for channel length less than 30nm. 65mV/dec is achieved at channel length of 40nm with

Fig. 10 DIBL variation over channel length with different mole fraction

mole fraction less than 0.3 DIBL decreases with increase in mole fraction, very less DIBL of 15mV/V is achieved at channel length 40nm with mole fraction 0.9.

Table- II: Computed parameters of  $Si_{1-X}Ge_X$  HJLFinFET for different mole fraction X at  $V_{D,Lin}$  =0.05 V and  $V_{D,Sat}$  = 0.8V

| Device                  | X=0.1        | X=0.3        | X=0.5        | X=0.7        | X=0.9       | X=0(Silicon) |

|-------------------------|--------------|--------------|--------------|--------------|-------------|--------------|

| V <sub>TH</sub> (mV)    | 300          | 300          | 300          | 300          | 300         | 300          |

| DIBL(mV/V)              | 37.7         | 33.04        | 29.27        | 26.24        | 23.7        | 41.8         |

| SS(mV/dec)              | 72.19        | 71.53        | 71.054       | 71.5         | 71.224      | 72.7         |

| I <sub>ON</sub> (A/μm)  | 2.15 x 10-5  | 2.3 x 10-5   | 2.39 x 10-5  | 2.43 x 10-5  | 2.42 x 10-5 | 20.3 x 10-5  |

| I <sub>OFF</sub> (Aμ/m) | 6.13 x 10-11 | 1.67 x 10-10 | 5.69 x 10-10 | 1.243 x 10-9 | 1.04 x 10-9 | 5.15 x 10-11 |

## D. Temperature Variation

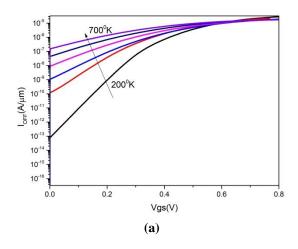

Fig.11 indicates the temperature variation upto  $700^{0}$ K on transfer characteristics of SiGe HJLFET for mole fraction 0.1 and 0.9. Temperature variations causes different scattering phenomenon which reflects in mobility variation [20]. Better off current is achieved with decrease in temperature eventually increasing  $I_{ON}/I_{OFF}$  ratio. It is observed that current improves over  $10^{3}$  times over temperature decrease from  $300^{0}$ K to  $200^{0}$ K for the mole fraction x=0.1 and  $10^{2}$  for x=0.9. This is due to carrier concentration at high temperature. Better off current is achieved at mole fraction 0.1 around  $10^{-13}$ .

10° 5 700° K 10° 6 10° 700° K 10°

Fig, 11 Temperature variation over  $I_{DS}$  - $V_{GS}$  for mole fraction (a) x=0.1 and (b) x=0.9.

## CONCLUSION

In this article we presented the DC characteristics of SiGe Hybrid Junction-less n-FinFET with different mole fractions. The impact of mole fraction for different channel length and temperature are investigated and concludes that mole fraction less than 0.3 witnesses better on current off current results when channel length is less than 20nm.

## IMPACT OF MOLE FRACTION VARIATION ON NANOSCALE SIGE HYBRID FINFET ON INSULATOR

#### REFERENCES

- Fahad, Hossain M, Chenming Hu, Muhammad M. Hussain," Simulation study of a 3-D device integrating FinFET and UTBFET" IEEE Transactions on Electron Devices 62, no. 1 (2015): 83-87

- Wu, M., Alivov, Y.I., Morkoc, H. "High-K dielectrics and advanced channel concepts for Si MOSFET" J. Mater. Sci. Mater. Electron. 19, 915–951 (2008).

- Wu, M., Alivov, Y.I., Morkoc, H. "High-K dielectrics and advanced channel concepts for Si MOSFET" J. Mater. Sci. Mater. Electron. 19, 915–951 (2008).

- Fischetti M.V, Laux, S.E.: Band structure, deformation potentials, and carrier mobility instrained Si, Ge, and SiGe alloys. J. Appl. Phys. 80, 2234–2252 (1996).

- Colinge, JP., Lee, CW., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Razavi, P., O'Neill, B., Blake, A., White, M., Kelleher, A.-M., McCarthy, B., Murphy, R.: "Nanowire transistors without junctions. Nat. Nanotechnology. 5, 225–229 (2010).

Sun, Thompson, S.E., Nishida, T. "Physics of strain effects in

- Sun, Thompson, S.E., Nishida, T. "Physics of strain effects in semiconductors and metal-oxide-semiconductor field-effect transistors" J. Appl. Phys. 101, 104503 (2007).

- Fei Ding, Yi-Ting Wu, Daniel Connelly, Wenyi Zhang and Tsu-Jae King Liu. "Simulation-Based Study of Si/Si0.9Ge0.1/Si Hetero-Channel FinFET for Enhanced Performance in Low-Power Applications" IEEE electron letters 2019; Volume 40, pp. 363–366.

- Maiti, C.K., Armstrong, G.A.: "Applications of silicon-germanium heterostructure devices" CRC Press (2001).

- Yan-Lin Li, Kuei-Shu Chang-Liao, Chen-Chien Li "Improved Electrical Characteristics of Bulk FinFETs With SiGe Super-Lattice-Like Buried channel" IEEE Electron Device Letters, Vol. 40, 2, February 2019.

- F. Y. Huang, "Theory of strain relaxation for epitaxial layers grown on substrate of a finite dimension," Phys. Rev. Lett., vol. 85, no. 4, pp. 784–787, Jul. 2000, doi: 10.1103/PhysRevLett.85. 784.

- Colinge JP, Lee CW, Afzalian A, Akhavan ND, Yan R, Ferain I, Razavi P, O'Neill B, Blake A,WhiteM, Kelleher AM, McCarthy B, Murphy R (2010) Nanowire transistors without junctions. Nat Nanotechnology 5:225–229

- 12. Ghosh D, Kranti A (2014). Semicond Sci Technol 30:015002

- Saini G, Choudhary S (2016) Analog/RF performance of sourceside only dual-k sidewall spacer trigate junctionless transistor with Parametric variations. Superlattice Microst 100:757–766

- Baruah RK, Paily RP (2013) Impact of high-k spacer on device Performance of a junctionless transistor. J Comput Electron 12:14–19

- Zhang, Weimin, Jerry G. Fossum, Leo Mathew "The ITFET: A novel FinFET-based hybrid device." IEEE Transactions on Electron Devices 53, no. 9 (2006): 2335-2343.

- Sentaurus User's Manual, Version L-2016.03, Synopsys, Mountain View, CA, USA, 2016.

- 17. Elena Gnani, Antonio Gnudi, "Physical Model of the Junctionless UTB SOI-FET".

- M. Choi, V. Moroz, L. Smith, and J. Huang, "Extending drift-diffusion paradigm into the era of FinFETs and nanowires" SISPAD, Washington, DC, USA, Sep. 2015, pp. 242–245.

- Shockley, W., Read Jr., W.T.: "Statistics of the recombination of holes and electrons" Phys. Rev. 87, 835 (1952).

- 20. Balraj Singh ,Deepti Gola.; "Temperature Sensitivity Analysis of Double Gate Junctionless Field Effect Transistor with Vertical Gaussian Doping Profile" 2016 International Conference on Micro-Electronics and Telecommunication Engineering.

### **AUTHORS PROFILE**

G VIDHYA SAGAR received the B.Tech degree in Electrical and Electronics Engineering from JNTU university and M.tech degree in VLSI systems from National Institute of Technology Trichy(NITT), Trichy, Tamil Nadu, India, in 2010 and currently working towards the Ph.D. at VIT university Vellore, Tamil Nadu, India. Since July 2010, he has been with VIT University,

Vellore, Tamil Nadu, India, working as Assistant Professor, where he is currently an Assistant Professor Senior His research topic is FinFET device modelling

VIJAYAKUMAR D received the M.E degree in Power Systems from SCSVMV, Enathur, Tamil Nadu, India, in 2005 and the Ph.D degree in Electrical Engineering from MANIT, Bhopal, India, in 2010. Since 2009, he has been with the School of Electrical Engineering (SELECT), VIT University, Vellore, India, as an Associate Professor, where he is currently a Professor.

His research interests include modeling and control of DC/DC converters, design of Renewable Energy-supplied Inverters for grid connection, and Power Systems Protection and Control.