# Performance Analysis of Multi-Fault Tolerant on Multiprocessor System On-chip

# R. Arun Prasath, P.Maniganda V Keerthi, Y.Sreeja

Abstract— As plan multifaceted nature increments and scale innovation into profound submicron region, the opportunity of harm and unhappiness in Networks-on-Chip (NoCs) prolonged element. On this artwork, we middle across the examination and evaluation techniques to improve the unwavering excellent and strength of Network Interfaces (NIs) in multiprocessor framework on-chip engineering primarily based totally Noc. NIS is going about as an interface the various center covered innovation and interchanges foundation; incorrect conduct of one in all them can impact, ultimately, the overall framework. On this paintings, proposes a version of utilitarian mistakes for NI components to assess their helplessness to mistakes. Showing levels tolerant affiliation that may be utilized to decrease the affects of each changeless and transitory blames in NI. Display trial reenactment with limited overhead can collect NI dependability equal to the best got via manner of utilizing a framework using 3 stylish secluded repetition techniques, even as putting aside to 48 percent in the place, just as growing noteworthy energy decrease.

Rundown phrases— Networks-on-Chip (NoC), diagnosis, performance, multi-layer, design space exploration

# I. INTRODUCTION

A typical NoC based system consists of processing elements (PE), network interfaces (NI), switches and channels. the subsequent switch carries switches, cradles and steerage intent. Cushion near expends approximately 64% of the absolute bunch (join transfer) spillage control for all mechanical manner, which makes it the most important power customer in the framework Noc. All connections in the NOC can be at the same time utilized for statistics transmission, which offers an elevated degree of parallelism. this is an intriguing solution for supplant ordinary correspondence fashions, as an instance, shared shipping or factor-to-point interface committed by NOC

Figure 1Router Link Architecture

Revised Manuscript Received on 14 September, 2019.

**R. Arun Prasath,** Professor, Department of ECE, Siddhartha Institute of Technology & Sciences, Narapally, Ghatkesar, Hyderabad, Telangana, India. E-mail: prasath2k6@gmail.com)

**P.Manigandav,** Associate Prof, Department of ECE ,Affliated to JNTU colleges, Hyderabad, Telangana, India. (E-mail: manigandapuraji@gmail.com)

**V Keerthi,** Assist. Prof, Department of ECE, Siddhartha Institute of Technology & Sciences, Narapally, Ghatkesar, Hyderabad, Telangana, India

**Y.Sreeja**, Assist. Prof, Department of ECE, Siddhartha Institute of Technology & Sciences, Narapally, Ghatkesar, Hyderabad, Telangana, India

NOC offers better adaptability of on-chip delivery in moderate of the reality that as greater assets had been acquainted with the framework, actually as extra switches and connections are acquainted with interface them to the tool. Assist devours the most important department of the dynamic and spillage manipulate NOC hubs (switches + interface). Save bundles in the cushion devours notably a whole lot less power than the transmission. Each layer has a selected tradeoff among first rate (granularity) and costs (overhead) end. On the automobile layer, the locating is actualized in programming, with out a greater tool expenses, and completed related to traditional going for walks framework. Anyways, fruitful records can be to a outstanding amount preoccupied from the system. Alongside these strains, the error can't be ascribed to singular entryways and wires. Extended granularity of the lower layer of tissue to the detriment of the judgments improved need to close down the device for the analysis or the price of the gadget worked in self-quit.

With this text, contributed the accompanying:

- NOC-express analytic way for 3 person layers: the auto layer, set up layer, and bodily layer and data connect layer.

- The combination of the combination of those methods into a multi-layer way to address bypass-layer facts change.

- The exam of every viable combination as for analytic first-class and effect execution, with the intention to recognize the Pareto exceptional association.

## II. PRESENT GADGET & METHODOLOGY

Tool on-Chip (NOC) has developed as of overdue as every other technique to interface and cope with the correspondence between the one of a kind licensed innovation squares required in complex gadget-on-Chip (SoC). Anyways, the advantages supplied thru the utilization of such an unpredictable correspondences basis should prompt restored shortcoming in the framework that need to be exposed to careful research and assessment. At the same time as NOC has been a growing region of instructional and research pursuits, protection within the framework remains to date for the most element unexplored. On this manner, the eye on safety views diagnosed with social framework and layout the potential strategies that may be done for the NOC to add to the general safety of the framework. As delivered in protection attacks on implanted frameworks may be organized in wonderful manners

Frameworks dependent on NOC can attack them cope with unique structures. In particular, 3 varieties of assaults can be diagnosed. Forswearing of carrier (DoS) assaults

# PERFORMANCE ANALYSIS OF MULTI-FAULT TOLERANT ON MULTIPROCESSOR SYSTEM ON-CHIP

planned for corrupting the exhibition of the framework in some way or some other. Amongst them, the assaults Bandwidth bargain expects to decrease switch pace interchanges over parcel transmission go to and pointless, to prompt excessive dormancy within the correspondence onchip, to arrange immersion. The working existence of battery-worked hooked up frameworks is the purpose of assaults Draining or Sleep Deprivation. Precise forms of assaults need to be feasible with the aid of sending a ceaseless hobby for casualties of the assault, to cause it to perform undertakings that starvation for manipulate. Extraction of categorised records of enthusiasm for perusing touchy records, simple suggestions or information positioned away within the reminiscence region or in the setup enlists internal a particular purpose.

Figure 2 System Output Part of Router Architecture

A structure for verifying cryptographic key trade inside the NOC, tending to specifically the warranty of intensity/EM attack from a framework containing middle non-affirm and secure. Device underpins affirmation, encryption, key trade, the new key and open key stockpiling, and a comparable method. There aren't any leaves on the center scrambled key and truly IP middle NOC securely run untrusted programming upheld. On the gadget stage, safety relies upon on a symmetric key cryptography, wherein each middle has its very very own safety wrapper securely save personal gadget key in non-unpredictable memory

## III. FRAMEWORK PROPOSED

Indicative structures may be implemented at amazing layers of the device to discover a long lasting blunder within the NOC. Each layer has its very own capacities, with the realization should be included, and the specific information challenge to the symptomatic method at the automobile layer, the product based totally diagnostic protocol (DP) can find out the segments of the harmed tissue through breaking down drawing near statistics bundles. In the device and the facts interface layer, functional diagnosis (FD) spotting the utilitarian conduct and cost of the relaxation of the gadget switches utilising an uncommon test bundles. Connection between layers indicative strategies usually completed with the resource of buying and selling demonstrative association between the layers and utilizing this in improvement to growth analytic tactics in my opinion.

#### A. Block Diagram

Figure 3 Interaction of Multi-Layer Technique

To recognize a flaw on a crossbar affiliation, a center of the road hub constantly sends a package to its assigned aim R first, earlier than conceivably in addition bisecting the way. Inside the event that the middle of the street hub presently gets an ACK from the collector it is able to reason that its transfer ought to have a crossbar flaw. This stop is predicated upon at the accompanying causes:

- 1) The center of the road hub has recounted the parcel in advance than, in this way, the way among the sending hub and transitional hub ought to be sans trouble.

- 2) due to the fact the center of the street hub gets an ACK from the collector, the manner among transitional hub and recipient should be sans hassle.

- 3) for the motive that analysis conference become actuated, in any event

One shortcoming need to exist at the manner from sender to collector.

On the factor even as joined with the FD or SD tactics, conference DP maps a connection or crossbar hassle to the comparing transfer. The motive in the back of that is FD and SD usually should be completed for an entire switch. If there must rise up an occurrence of a connection flaw, FDP is the neighbor of the switch that has analyzed the lack. Consequently, the faulty connection is related to its cause hub.

#### B. Realistic evaluation

Practical give up is finished at the tool layer so that it will distinguish all the more correctly the switch usefulness brought about by a flaw. To this stop, FD considers six practical unhappiness instructions as characterized in misrouting: A package is urged to an off-base yield port. Statistics debasement: information inner at least one dances is changed. Package deal misfortune is at any rate one parcel is misplaced on its way from the facts port to a yield port of a transfer. Trash parcel: each other package is produced and for-warded to a yield port. This includes parcel duplication. Bounce misfortune: at the least one dance of a parcel is out of place on its manner from the information port to a yield port of a transfer. Trash flutter: every other dance is created and sent to a yield port.

Some auxiliary shortcomings bring about not anything from what modified into surely mentioned utilitarian disappointments. Those shortcomings set up the buildup elegance. For all issues of this class, FD can't distinguish the stimulated switch paintings and the whole switch is

appeared as flawed. FD is finished on-line besides for the transfer under finding (SUD), which is prepared disconnected. Each extraordinary transfer in the machine stay employable and hold transmitting facts bundles. The NoC itself is implemented as take a look at get to component, on this way keeping far from the fee of a dedicated TAM of the machine framework.

# C. Beneficial online diagnosis

In combination with the realization conference DP, FD is in keeping with-shaped fantastically for an individual transfer determined out conceivably faulty thru DP. For the self-control of the SUD, every single nearby transfer are

covered, sending test parcels to the SUD's facts ports. Furthermore, the SUD gets check parcels via the usage of its community port from the close by getting prepared element. While send-ing test parcels, the neighbor switches live usable and can transmit statistics bundles by means of manner in their one-of-a-kind ports that are not associated with the SUD.

Within the event that FD is actualized without DP, all switches must be considered as possibly faulty. On this manner, FD need to be done for the general system. Certainly, all switches of a machine can be analyzed sequentially, yet this could bring about noteworthy inertness. To decrease dormancy, however many switches as should reasonably be expected must be analyzed in parallel. As neighbors of a SUD supply the check parcels, they can't be analyzed simultaneously. Henceforth, a making plans is wanted that determines the locating begin for every switch. We compel the making plans with the motive that every hub may absolutely ship bundles to every SUD in turn. The following determination plan for a chunk is delineated in figure 3. The huge range seemed for each transfer compares to the cycle wherein it is analyzed. Altogether the timetable contains of 5 cycles. Be aware that the quantity of cycles does not increment for large paintings systems.

Finding exceptional is evaluated by using whether or not a shortcoming may be identified and the way precisely it very well can be restrained. It's far constituted of the accompanying three attributes:

- A) The deficiency inclusion, i.E., the capacity to distinguish auxiliary troubles,

- B) Localization and grouping precision, i.E., the ability to pinpoint the location of an issue and to order its useful impact, and

- C) The occasion of bogus positives. Whilst those man or woman attributes may be evaluated quantitatively, through and large quality has severa measurements and cannot be envisioned with a solitary, efficaciously similar variety. We in this manner request finding methods as steady with their quantitative execution as for the 3 standards, and dole out them great degrees within the range from 1 (least awesome) to five (maximum caliber).

## IV. EFFECTS AND DISCUSSION & RESULTS

On this region, we affirm every finding technique and their blends as for evaluation top notch and effect on framework execution. The meaning of each evaluation standards is given within the precise regions. As they are in battle with every different, we study their tradeoff and determine pareto-best. For the first-rate assessment of beneficial and auxiliary locating we have got utilized the net rundown combined from our RTL shape of a mean switch with wormhole replacing, 5 in/out ports, a crossbar, a XY transfer, and Stall/flow flow manipulate. For execution evaluation a system C model of the entire NoC has been recreated, which incorporates a cycle-proper transfer model. The reenactment model is parameterized with NoC artwork period, arrange load and location site visitors version.

Figure 4 UART Receiver Output Waveform

Figure 5DDR DRAM Output Waveform

Figure6 Multi-Tolerant Output Waveform

Figure 7Speed Analysis of Single FAULT NOC System

Speed analysis of a single fault NOC shown in the image above 7. This analysis depends on the maximum range of frequencies. Therefore, the maximum range of frequencies used to generate the output is 151.7MHz.

Figure 8Power Analysis of Single Fault NoC System

Strength Analysis of heterogeneous NOC shown in the picture above 8. This analysis is mainly concentrated on the IOS number in the system to get the output. In the entire system, the available number of 348 and IOS IOS is used to obtain power output 180. Utilization 49.4%.

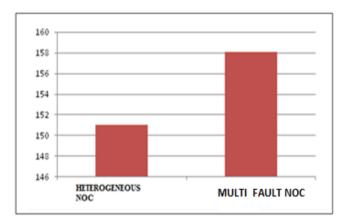

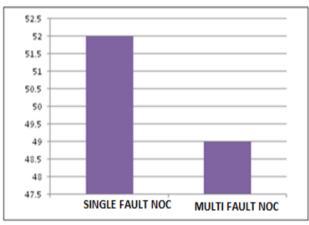

Figure 9 Comparison chart for Speed Analysis

Figure 10 Comparison Chart for Power Analysis

effects of simulated faults by injecting a permanent error at some point of operation. The common yield of greater than 25 styles of errors are generated randomly by using 1 to five mistakes. each model is faulty transfer error by means of corrupting packets passing through the switch. each blunders pattern changed into simulated to 500,000 cycles. In this era, mistakes are injected separately at random points in time.

**Table 1 Performance Analysis Comparison table**

| Diagnosis Technique | Area | Speed |

|---------------------|------|-------|

| Single Fault NoC    | 4    | 151   |

| Multi Fault NoC     | 1    | 158   |

To evaluate the impact of locating techniques on framework execution, we to start with studies to what quantity it takes each willpower method to restrict a perpetual flaw in the internet-paintings. For this reason, we've got reenacted the NoC underneath direct and excessive device load. For the initial 20,000 cycles the gadget is loaded up with bounces in advance than a solitary lasting flaw is infused to the device. The planned flaw confinement latencies are seemed in table 1. The results appear above correlation desk shows the specific parameter measurements, for example, area, pace, strength and postpone one after the alternative. At the same time as searching at each heterogeneous NOC and Multi flaw NOC, the Proposed is more and more productive.

### V. CONCLUSION

The aggregate of layer-unique end strategies right into a multi-layer evaluation method is straightforward to discover pare to-ideal preparations that provide a fantastic tradeoff among framework execution and locating wonderful. The presentation can be extended via consolidating a lower layer gadget with a second one on higher layer. On this setting, the way on better layer accomplishes tremendous execution with the resource of limiting the presentation impact of assessment because of a diminished deficiency confinement exertion. On the other hand, the system on decrease layer guarantees a excessive symptomatic best, empowered via the extra genuine records reachable at the decrease layer. The aggregate of a product prepare dedication convention with recognize to move layer with each utilitarian conclusion on arrange layer or auxiliary finding on the bodily layer end up being the most encouraging multi-layer analysis techniques.

#### REFERENCES

- Bondavalli.A and Chiaradonna . S, (2000), Threshold based additives to split brief from Intermittent Faults, IEEE change of pc. Pp 230-245.

- 2. Bowen Zhang, HuaxiGu, Kun Wang, Yintang Yang, Tan (2017), "Low Polling Time TDM with course-based totally wavelength undertaking, mag of optical correspondence put together, pp, no. 479-488.

- 3. Dally.W.J and Towles. B (2001), course Packets, now not wires: on chip interconnections Networks, IEEE Transcation of pc framework Laboratory, pp.#1-15.

- Ebrahimi.M and Daneshtalab.M, (2013) minimumroute trouble tolerant technique the usage of association retaining shape in systems on-chip, IEEE branch of statistics technology, pp, no. 1-14.

- Georg Sigl and Johanna Sepulveda, (2016), factor Channel assault on NOC based totally totally MPSOCs are sensible: NOC high+Probe attack, Institute for protection facts era, pp, no.113-126.

- 6. Hnaxigu, Zhengyu Wang and Bowen Zhang (2017), TDM-WDM primarily based structure for ONOC, IEEEOptical communique community, pp, no.351-363.

- Johanna Sepulvedal and Daniel Florez (2016), DynamicNOC Buffer Allocation for Timing component Channel assault protection, IEEE Institute for safety in facts technology, pp, no.116-121.

- Kakoee.M.R and Bertacco.V (2011), A distributed and Topology Agnoctic approach for 8db290b6e1544acaffefb5f58daa9d83 NOC TestingTesting of Very big Scale Integration,pp,no.113-

- one hundred twenty.

- Lu.Z and Wang.Y, (2012), Dynamic float regulation for IP Integration on network-on-Chip, 6th IEEE/ACM worldwide Symposium on Networks-on Chip.(NOCs),pp,no.A hundred and fifteen-123

- Petersen. Okay and Oberg.J (2007), towards a Scalable TestMethodology for second-paintings network-on-Chip, department of digital pc and software program application machine, Royal Institude of era, pp,no. 75.

- Xiang. D and Zhang. Y, (2011), price-powerful power aware center finding out in NOCs depending on some other unicast-based Multicast Scheme, IEEE Transaction on pc Aided layout of included Circuits and system, pp, no.A hundred thirty 5-147.

- 12. Xiang. D (2013), A price-powerful Scheme for networkon Chip Router and Interconnect finding out, 22nd Asian test Symposium, pp, no. 18-21.

- Yao. Y and Lu. Z (2014), Fuzzy waft law for NOC based totally Chip Multi center tool, nineteenth Asian South Pasific layout Autom conference (ASPDAC), pp, no.20-23.

- Zhao. X and Lu. Z, (2015), Heuristics Aided Tightness evaluation of Analytical Bounds in NOC, IEEE Transaction pc-Aided design Integer, pp, no.986-999.

- Zhonghai Lu and Yuan Yao (2016), Dynamic visitors regulation for NOC based system, IEEE Transaction on Very huge Scale Integration (VLSI) device, pp, no. 556-569