# Adaptive Filter Architecture for FPGA Implementations

# Kalaiselvi, Vasuki

Abstract: Adaptive filters play a Significant role in digital signal processing but their implementation in real time consumes high area and power. Several architectures have been proposed for their real time implementation such as Distributed Arithmetic, CORDIC, Systolic, etc. which reduces the area and improves the speed. All these architectures are multiplier less and among these, the CORDIC structure is simple and gives reduction in area at the cost of speed. To overcome this drawback, it is modified by implementing it along with Karatsuba algorithm (KA). The combination of KA algorithm and CORDIC structure gives better performance in terms of area and speed. The proposed work is implemented using Xilinx system generator. The structure is tested for different bit representations and the results show that the proposed structure has better performance compared to the existing structures. The proposed structure can be used in applications such as RADAR, Channel Equalizers and Noise Cancellers.

Keywords: Adaptive filter, FPGA, CORDIC,KA algorithm

#### I. INTRODUCTION

An adaptive filter is defined as a system consisting of linear filter with its transfer function being controlled by a variable parameter using an optimization algorithm. It is a considered as a computational device that models the relation between the two signals iteratively. Adaptive filter are usually realized using a set of instruction that runs on devices like microprocessor, DSP chip or a field programmable array(FPGA). The different classes of adaptive filters are LMS and RLS filters.LMS adaptive filters, have various advantages such as flexibility and programmability, good convergence behavior. computational simplicity, hence it may be easier for it to be implemented using Field Programmable Gate Arrays (FPGAs).

Adaptive filters [1] are used in wide applications in areas like Digital signal processing (DSP), Communications, system identification, noise cancellation and echo cancellation. This paper proposes a new architecture for implementing the adaptive filter using FPGAs. The proposed architecture uses CORDIC structures and KA algorithm for its implementation. CORDIC (Coordinate Rotational Digital Computer) Structures are used widely in computing several mathematical and digital signal processiong operations. Few such operations include computation Trigonometric, hyperbolic exponential,

multiplication operations and DSP operations like [17][18] Discrete Cosine Transform, Fourier Transform. It is

efficient because of its simpleshifter and adder architecture

Due to the above reasons CORDIC occupies less space and has less computation time. KA algorithm is known forits high speed operation with reduced chip area[2], [14]. In the proposed architecture the CORDIC structure is adopted in KA algorithm , thus improving the systemthroughput and reducing the chip area. This proposed architecture is implemented using VHDL.

Adaptive filter algorithms are widely used in linear filters. The two adaptive algorithms for adaptive filter are Least Mean Square (LMS) and Recursive Least square (RLS). The output signal z(n) obtained from the filter is given by

$$z(n) = x(n) * w(n)$$

(1)

Where  $n = 0, 1, 2, 3, \dots, N$ . x(n) refers to the input signal, w(n) refers to the filter co-efficient, and z(n) refers to the output signal.

The error signal of the filter is given by

$$e(n) = z(n) - d(n) \tag{2}$$

Where e(n) refers to the error signal d(n) refers to the desired signal.

The filter coefficients are updated by the  $w(n+1) = w(n+1) + \alpha E(n) * x(n)$  (3)

The LMS algorithm has less number of operations compared to the RLS algorithm.

# II. CORDIC STRUCTURES

CORDIC structure can be used to compute different signal processing operations like DCT,FFT, and mathematical operations such as calculation of sine and cosine values using only adders and shifters.CORDIC can be implemented in three different structures namely Sequential, parallel and pipelined architecture. Among the three architecture, Parallel architecture has high speed. Hence it is widely used in RADAR and Bio medical applications.

Using CORDIC the multiplication operation is carried out in a multiplierlessenvironment. The product is obtained from the CORDIC multiplier by shifting one of the operand and the other operand to zero [1],[4], [14].

The CORDIC multiplication is carried out as

$$C = A * B \tag{4}$$

### Revised Manuscript Received on December 28, 2018

Kalaiselvi, Assistant Professor II, Electronics and Communication Engineering,, Kumaraguru College of Technology, Coimbatore, Tamil Nadu India

Vasuki, Professor, Mechatronics Engineering, Kumaraguru College of Technology, Coimbatore, Tamil Nadu, India

# **Adaptive Filter Architecture for Fpgp Implementations**

Where C is the product and A, B are the operands of the multiplier. Then C can be represented as

$$C = B * \sum_{i=1}^{B} a_i * 2^{-i}$$

(5)

$$= \sum_{i=1}^{B} B * a_{i} * 2^{-i}$$

(6)

$$=\sum_{i=1}^{B} a_i * B * 2^{-i} \tag{7}$$

From above equation it is seen that the product C comprises of shifted versions of the operand B. The coefficients  $a_i$  is determined by making x to 0 one bit at a time. If the i<sup>th</sup>bit position of A is non-zerothen, B<sup>i</sup> is right shifted by i bits and adding the Value of C to it. The i<sup>th</sup>bit is then removed from A by subtracting  $2^{-i}$  from A. On the other hand if the value of A is negative then thei<sup>th</sup> bit in the twos complement format is removed by adding  $2^{-i}$

## A. Ka Algorithm

The KA algorithm is a recursive algorithm which is based on the divide and conquer method. The larger operands are divided into K- small number and product is calculated. The KA algorithm can be represented using two ways. They are 2-way and 3-way algorithm

## ALGORITHM - KA 2 Way Structure:

Let X and Y represent the two operands of the multiplier. They are expressed as

$$X = X_0 + X_1 M^{\frac{N}{2}} \tag{8}$$

$$Y = Y_0 + Y_1 M^{\frac{N}{2}} (9)$$

Let Z be the product of  $\ X$  and  $\ Y$ . Then  $\ Z$  computed by  $\ KA$  equation as

$$Z = K_0 + (K_{01} - K_0 - K_1)D^{M/2} + K_1D^M$$

(10)

Where

M represents the number of bits

D represents the base

$$K_0 = X_0 Y_0, (11)$$

$$K_1 = X_1 Y_1,$$

(12)

$$K_{01} = (X_0 + X_1)(Y_0 + Y_1)$$

(13)

The above multiplication is done by CORDIC structures. The entire operation is done without multiplier .The multiplication is performed for smaller operand. Hence the multiplication complexity is reduced from  $O(n^2)$ . Also the overall critical delay is improved.

ALGORITHM – KA 3 Way Structure:

The multiplication is carried out by dividing the operand into three parts. Let the two multiplication operands be A and B. The two operands is then expressed as

$$A = A_0 + X^{n/3} A_1 + X^{2N/3} A_2 \tag{14}$$

$$B = B_0 + X^{n/3}B_1 + X^{2N/3}B_2$$

(15)

Let Cbe the product by multiplying A and B. Then C is expressed using 3-way as

$$C = C_0 + C_1 X^{N/3} + C_2 X^{2N/3} + C_3 X^N + C_4 X^{4N/3}$$

(16)

Where

$$C_0 = P_0$$

$$C_1 = P_{01} - P_0 - P_{1(17)}$$

$$C_2 = P_{02} - (P_0 + P_2) - P_2 \tag{18}$$

$$C_3 = P_{12} - (P_1 + P_2) \tag{19}$$

$$C_4 = P_2 \tag{20}$$

$$P_0 = A_0 B_0 (21)$$

$$P_1 = A_1 B_1 \tag{22}$$

$$P_{01} = (A_0 + A_1)(B_0 + B_1)$$

(23)

$$P_{02} = (A_0 + A_2)(B_0 + B_2)$$

(24)

$$P_{12} = (A_1 + A_2)(B_1 + B_2) \tag{25}$$

#### III. ARCHITECTURE

The Adaptive algorithm is used in situations when it is necessary to get the desired signal inspite of the error signal. The weights are updated as per equation

$$w(n+1) = W(n) + \mu[d(n) - z(n)] * x(n)$$

(26)

If MSE gradient is positive, then weights are updated as per equation

$$w(n+1) = W(n) - \mu[d(n) - z(n)] * x(n) (27)$$

The negative sign indicates that the weight have to be updated in the direction opposite to the gradient slope.

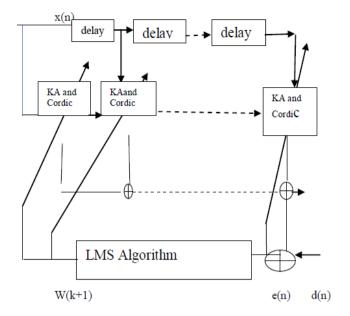

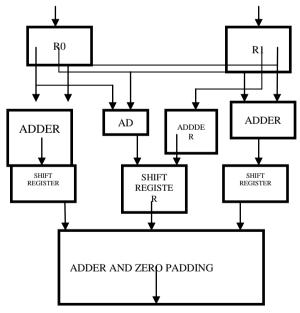

The overall block diagram of the proposed architecture is shown below The difference between the actual response and the desired response is computed. The difference is then multiplied by the input signal. The multiplications in the above update equations are carried out using the KA algorithm described in section I. Furhter the inner multiplication in the KA decomposition is done using the CORDIC structure. Since the CORDIC structure is based on the shift and addoperations the proposed architecture doesn't have multipliers. The KA algorithm using 2-way decomposition is shown in fig.2. The structure consist only of Adders and shift registers. The error signal and the input signal are the two operands (inputs) of the proposed architecture. The two operands are split into two equal parts as per equations 8-9. The partial products are calculated as per equations 10 - 13.

Fig.1. Architecture of the proposed structure

The partial products resulting out of the multiplications (equations 11 - 13) are carried out using CORDIC structures. The multiplication using CORDIC is done wide equations 4-7. By this process the large valued operands are decomposed into small values and the product is computed. Hence the computation complexity is reduced. Also the proposed architecture involves only adders and shifters, hence the hardware complexity is also less.

Fig.2. Architecture of CORDIC incorporated KA 2-way Multiplier structure

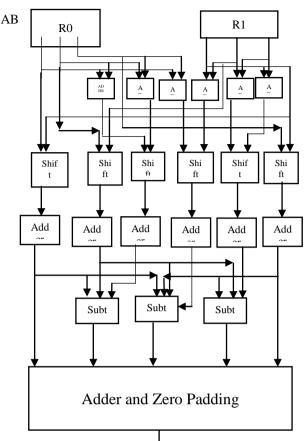

Fig.3. Architecture of CORDIC incorporated KA 2-way Multiplier structure

Similarly the KA 3-way structure is framed. The major advantages is that the higher valued operands are decomposed into very small values compared to the KA 2-way structure. The architecture of KA 3-way structure is shown in fig 3. Similar to the KA 2-way decomposition the KA 3 way is also done. First the two operands are divided into two equal parts ( equations (14,15)). Each part is decomposed into three parts and then the partial products are computed (equations 16-25). The multiplication operation involved in computing the partial products (21-25) is done with the help of CORDIC structures. Since the decomposed values are small the computatipon complexity of this structure is less compared to the @- way decomposition.

## IV. SIMULATION RESULT

A CORDIC incorporated KA FIR adaptive filter is implemented using VHDL . On reset signal the ouputis set to zero. The initial weights are obtained and fed to the filter. The weight is convoluted with the input signal and the output is produced. The actual output is compared with the desired output and the weights are updated according to the proposed architectutres for each clock cycle.

# **Adaptive Filter Architecture for Fpgp Implementations**

The results are obtained for three different structures CORDIC, KA 2-way with CORDIC, KA 3 way with CORDIC.

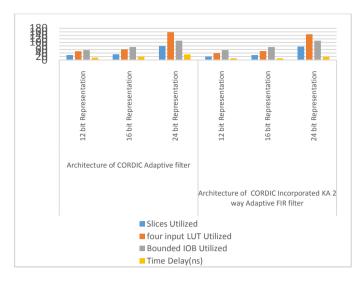

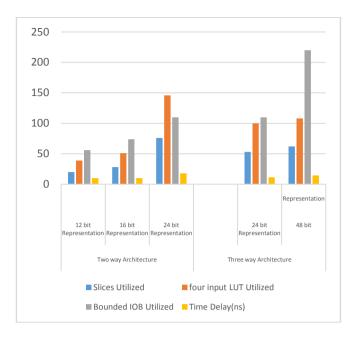

The three structures are simulated for different bit lengths such as 16 bit, 24 bit, 32 bit, 48 bits. Table 1 and 2 shows the various parameters obtained for different bit combinations. Table 1 shows the performance comparison between CORDIC structure and the KA 2-way with CORDIC structure. The later structure occupies less number of slices and number of LUTs. The delay produced by the KA 2- way structure is less compared to the CORDIC structure because the value of the operands are decomposed and computed. Hence this structure is efficient in terms of hardware and computation time.

| Para<br>met<br>er                      | Architecture of CORDIC<br>Adaptive filter |                                  |                                  | Architecture of<br>CORDIC Incorporated<br>KA 2 way Adaptive<br>FIR filter |                                  |                                         |  |

|----------------------------------------|-------------------------------------------|----------------------------------|----------------------------------|---------------------------------------------------------------------------|----------------------------------|-----------------------------------------|--|

|                                        | 12 bit<br>Repre<br>sentati<br>on          | 16 bit<br>Repre<br>sentati<br>on | 24 bit<br>Repre<br>sentati<br>on | 12 bit<br>Repre<br>sentati<br>on                                          | 16 bit<br>Repre<br>sentati<br>on | 24<br>bit<br>Rep<br>rese<br>ntat<br>ion |  |

| Slic<br>es<br>Util<br>ized             | 28                                        | 33                               | 80                               | 20                                                                        | 28                               | 76                                      |  |

| four inpu t LU T Util ized             | 50                                        | 61                               | 158                              | 39                                                                        | 51                               | 146                                     |  |

| Bou<br>nde<br>d<br>IOB<br>Util<br>ized | 56                                        | 74                               | 110                              | 56                                                                        | 74                               | 110                                     |  |

| Tim e Del ay(n s)                      | 13.23<br>6                                | 19.04                            | 31.37                            | 9.954                                                                     | 9.993                            | 17.<br>762                              |  |

TABLE 1

Performance Comparison of CORDIC and KA 2-way

Structure

Fig. 4. Performance Comparison of CORDIC Architecture and KA 2- way with CORDICarchitecture

The Table 2 shows the performance analysis of KA-2 way with CORDIC and KA 3-way with CORDIC structures .The KA 3- way with CORDIC shows better simulation resuls compared to the other structures. Also this structurebeeter results when the input data has very large values. This structures is also best in terms of hardware utilization and computation time.

| Para<br>mete<br>r                  | Two                             | way Archite                     | Three way<br>Architecture       |  |                             |                             |

|------------------------------------|---------------------------------|---------------------------------|---------------------------------|--|-----------------------------|-----------------------------|

|                                    | 12<br>bitRepr<br>esentati<br>on | 16<br>bitRepr<br>esentati<br>on | 24<br>bitRepr<br>esentati<br>on |  | 24 bit<br>Repres<br>entatio | 48 bit<br>Repres<br>entatio |

| Slic<br>es<br>Utili<br>zed         | 20                              | 28                              | 76                              |  | 53                          | 62                          |

| four inpu t LUT Utili zed          | 39                              | 51                              | 146                             |  | 100                         | 108                         |

| Bou<br>nded<br>IOB<br>Utili<br>zed | 56                              | 74                              | 110                             |  | 110                         | 220                         |

| Tim e Dela y(ns )                  | 9.954                           | 9.993                           | 17.762                          |  | 11.384                      | 14.357                      |

TABLE 2

Performance Comparison of KA 2-way and KA 3-way

Structure

Fig.5. Performance Comparison of CORDIC with KA 2 way and 3 way structures.

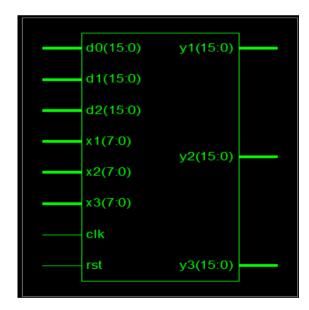

# A. Rtl Schematic Of The Proposed Strucutre

The RTL schematic diagram of the structure proposed is shown in figure 6.  $X_1, X_2, X_3$  represents the input signal,  $d_0, d_1, d_2$  represents the desired signal and  $Y_1, Y_2, Y_3$  represents the output signal.

Fig. 6. RTL schematics of FIR adaptive filter

#### V. CONCLUSION

In this paper multiplier less architecture for implementing adaptive filter was presented. From the simulation results it is found that the KA 2 way and KA 3 way with CORDIC algorithm provides a better performance in terms of hardware complexities and time delay. Also the KA 3 way with CORDIC algorithm shows better performance for high value of input data . Thus this architecture could be used in various applications like noise cancellers, equalizers, echo cancellers.

#### REFERENCES

- P. K. Meher, J. Valls, T.-B.Juang, K. Sridharan, and K. Maharatna, "50 years of CORDIC: Algorithms, architectures, and applications," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 56, no. 9, pp. 1893– 1907, Sep. 2009.

- Chung-Hsin Liu, Chiou-Yng Lee and Pramod Kumar Meher, "Efficient Digital-serial based KA based multiplier over binary Extensions field using block recombination approach," IEEE Trans. on circuits Syst:Reg. papers, Vol. 62, No. 8, Aug 2015

- Reid M. Hewlitt, "Canonical Signed Digit Representation for Fir Digital Filters", IEEE Workshop on Signal Processing Systems, 2000,pp. 416426.

- AmritakarMandal, BrajeshKumarKaushik, Brijesh Kumar, R.P. Agarwal "Implementation of Adaptive FIR Filter for pulse Doppler Radar," proceedings of the IEEE, pp. 978-1-4244-9190-2

- P.Albicococo, G.C. Cardarllic, Pontarelli, "Karatsuba implementation of FIR filter," Int. J. on VLSI Signal Processing, 978-1-4673-5050-1

- B. Swapna Reddy, V. Rama Krishna, "Implementation of Adaptive Filter Based on LMS Algorithm," Int. J. of Engineering Research & Technology (IJERT) Vol. 2 Issue 10, Oct – 2013

- N. Takagi, T. Asada and S. Yajiima, "Redundant CORDIC method with a constant scale factor for Sine and Cosine computation," IEEE Trans. On comput., Vol-C-40, No, 9, pp. 989-995,1991

M.D. Meyer and P. Agarwal, "A modular pipelined

- M.D. Meyer and P. Agarwal, "A modular pipelined implementation of a delayed LMS traversal adaptive filter," ir IEEE int. symposium on ircuitsSyst,, May 1990,pp. 1943-1946.

- Ying He, Hong He, Li Li, Yi Wu, Hongyan pan, "The Applications and Simulation of Adaptive Filter in Noise Canceling," in Int. Conf. on comput. Science and Software Engineering, Vol: 4 year: 2008.

- J.E. Volder, "The Birth of CORDIC," Int.J. on VLSI signal processing, Vol.30, pp. 25-101, 2000.

- C-Y.Lee and P.K.Meher, "Efficient bit-parallel multipliers over finite fields GF," comput. Elect. Eng., vol. 36 no. 5, pp. 955-968, 2010

- A.Vanitha, N. Venkatesh Kumar, "Design Implement and Simulation of adaptive FIR Filter using CORDIC structures for Radar applications," Int.J. of Engineering Science and Innovative Technology (IJESIT), Vol. 2, Issue 4, Jul 2013

- 13. Chung-Hsin Liu, Chiou-Yng Lee and Pramod Kumar Meher, "Efficient Digital-serial based KA based multiplier over binary Extensions field using block recombination approach," IEEE Trans. on circuits Syst:Reg. papers,Vol.62,No.8, Aug 2015

- 14. Lavanya, M., &Kalaiselvi, A. (2016, March). High speed FIR adaptive filter for RADAR applications. In Wireless Communications, Signal Processing and Networking (WiSPNET), International Conference on (pp. 2118-2122). IEEE.

- Sureshkumar N, K.Paramasivam, "Bypassing-Based Multiplier Design: A Tutorial and Research Survey", International Journal of Applied Engineering Research, ISSN 0973-4562 Vol. 10 No.29 (2015) pp:22606-22613.

- 16. D.Vinisha, P.Ramamoorthy, "Performance Analysis Of Enhanced Adaptive Scheduling Scheme In Wireless Sensor Networks" International Journal of Innovations in Scientific and Engineering Research (IJISER), Vol 1 Issue 4 APR 2014, pp258-263.

- K. Pradeep Mohan Kumar, M. Saravanan and M. Aramuthan, "Hybrid Network Intrusion Detection System Based on GANNModels", International Journal of Pure and Applied Mathematics, Volume 116 No. 11 2017, 31-39.

- L.Latha, K.Gayathri Devi, "A New Approach To Image Retrieval Based On Sketches using Chamfer Distance" Journal of Advanced Research in Dynamical and Control Systems, Vol. 9- Sp- 6 / 2017,pp1959-1968

319