# Design of 15-Level inverter topology with reduced number of semiconductor switches for Stand-Alone Power Systems (SAPS)

Ramachandran, TamilarasuViswanathan, SuryaprakashShanmugasundaram

Abstract: Stand-Alone Power Systems (SAPS) help us to supply energy to remote or regional places where electrical infrastructure is not available. SAPS usually has a power generation sources like photovoltaic panels, micro-wind turbines, battery bank, inverter, battery charger and often a diesel generator for power back. Solar or wind has erratic outputs, so frequent changes in power cannot be tolerated by sensitive loads. Hence, Battery banks play a significant role by storing charges directly from renewable energy sources through charge controllers and then delivers inverter for residential uses. SAPS are deliberated to be expensive because of the cost associated with battery banks and renewable energy sources; concurrently reducing the cost and increasing the power quality of inverter is approachable. This paper proposes the importance of multilevel inverter (MLI) by reducing the number of semiconductor switches which inevitably decreases the cost of MLI circuitry and diminishes the harmonics by increasing the level of output. The new topology of MLI inverter is designed and simulated using PSIM (9.0) tool.

Keywords: SAPS, Multilevel inverter, Topology, Total Harmonic Distortion

#### INTRODUCTION I.

ultilevel inverters are increasing viably for converting the most valuable renewable DC sources into a staircase waveform (AC). A Multilevel inverter key role is to give an AC waveform that should approach near to a sine wave. Conventional MLI gives two or three level output has more distortion, harmonics and hysteresis losses in case of motors.[1,2] Many basic MLI are incorporated to obtain a better output but economical consideration need to be focused more. More number of semiconductor switches incorporated in MLI is again a drawback as it increases switching losses, driver circuit and cost.

Research on MLI is in the area of reduction in number of switches, diodes, capacitor, DC sources and harmonics is a focus area as renewable energy is essential for our future. [1,2] Renewable energy resources are very economical form of energy so measures should be taken to make the resource economical and efficient, so a new proposed multilevel inverter is designed to give 15 level output with minimum number of semiconductor devices.

Nowadays addition of different sources can be effectively performed using asymmetric multilevel inverter topologies which help us in choosing rated input sources economically.[3,4] This is incorporated for stand-alone power system where micro wind generator and solar panel are major source of input energy.

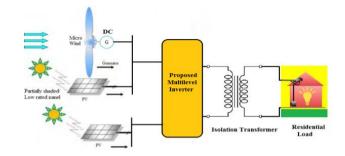

Fig.1.Schematic diagram of proposed multilevel inverter

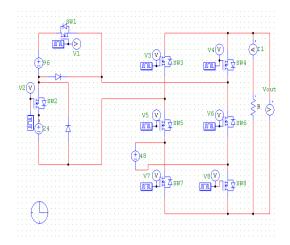

#### II. INVERTER TOPOLOGY

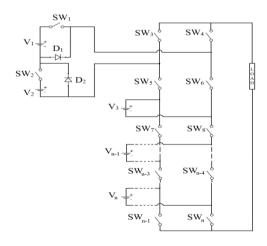

The proposed multilevel inverter is designed for standalone power system where additions of DC sources are decided based on the rated voltage and previous monitoring of energy sources. The general structure of proposed topology

Fig.2.General structure of proposed topology

The proposed MLI has been compared with various other multilevel inverters to know the effective construction of the topology. The control and working of proposed multilevel inverter for 15-level inverter is simulated and results are obtained.

271

Revised Manuscript Received on December 08, 2018.

Ramachandran, Electrical and Electronics Engineering, Kumaraguru Coll egeofTechnology,Coimbatore,Tamilnadu,India

TamilarasuViswanathanElectrical and Electronics Engineering, Kumaraguru College of Technology, Coimbatore, Tamilnadu, India

SuryaprakashShanmugasundaram,ElectricalandElectronicsEngineer ing, Kumaraguru College of Technology, Coimbatore, Tamilnadu, India

## III. CONFIGURATION OF PROPOSED 15-LEVEL INVERTER

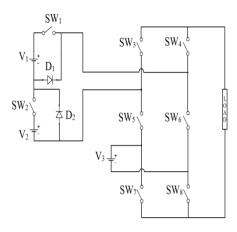

The proposed MLI has fifteen stages of operation for obtaining 15-level output.

Fig.3.Proposed 15-level inverter

The topology depends on number of input sources being necessarily connected. Number of voltage sources decides the number of output levels, usage and rating of semiconductor devices in constructing a multilevel inverter. The switching ONstate duration of switches differs with respect to the output levels and stress onparticular switches can be identified based on the following table [4].

|                                                                         | C              |

|-------------------------------------------------------------------------|----------------|

| Switches                                                                | $T_{on}Period$ |

| $\mathbf{SW}_1$                                                         | 11.2ms         |

| $\mathrm{SW}_2$                                                         | 9.8ms          |

| SW <sub>3</sub> , SW <sub>4</sub> , SW <sub>5</sub> , SW <sub>6</sub> , | 9.1ms          |

| $SW_7$ , $SW_8$                                                         |                |

| $D_{1,}D_{2}$                                                           | 5.6ms          |

**Table I Levels OfPeroids**

$SW_{1\&2}\text{contributes}$  more as it helps in adding with all other input sources.

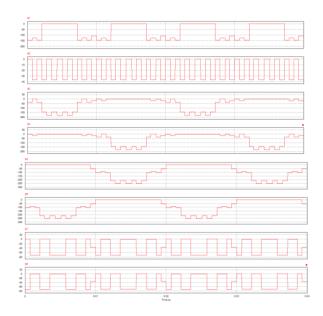

The switching strategies for different frequency have been given below with respective voltage levels for one complete cycle.

Fig.4 Switching Strategies

|           | Switching States |      |         |         |         |         |      |         |                                                 |

|-----------|------------------|------|---------|---------|---------|---------|------|---------|-------------------------------------------------|

| Stat<br>e | S<br>W           | SW 2 | SW<br>3 | SW<br>4 | SW<br>5 | SW<br>6 | SW 7 | SW<br>8 | Output<br>Voltage                               |

| 1         | 0                | 0    | 1       | 0       | 1       | 0       | 0    | 1       | $V_3$                                           |

| 2         | 0                | 1    | 0       | 1       | 1       | 0       | 1    | 0       | $V_2$                                           |

| 3         | 1                | 0    | 0       | 1       | 1       | 0       | 1    | 0       | $V_1$                                           |

| 4         | 1                | 1    | 0       | 1       | 1       | 0       | 1    | 0       | $V_1+V_2$                                       |

| 5         | 1                | 0    | 0       | 1       | 1       | 0       | 0    | 1       | $V_1+V_3$                                       |

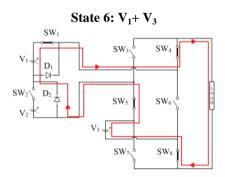

| 6         | 0                | 1    | 0       | 1       | 1       | 0       | 0    | 1       | $V_2+V_3$                                       |

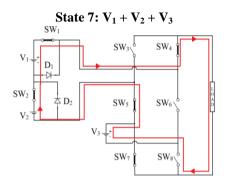

| 7         | 1                | 1    | 0       | 1       | 1       | 0       | 0    | 1       | V <sub>1</sub> +V <sub>2</sub> +V <sub>3</sub>  |

| 8         | 0                | 0    | 0       | 0       | 0       | 0       | 0    | 0       | 0                                               |

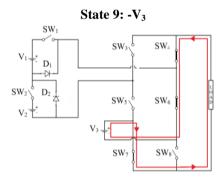

| 9         | 0                | 0    | 0       | 1       | 0       | 1       | 1    | 0       | -V <sub>3</sub>                                 |

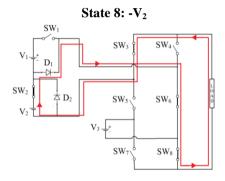

| 10        | 0                | 1    | 1       | 0       | 0       | 1       | 0    | 1       | -V <sub>2</sub>                                 |

| 11        | 1                | 0    | 1       | 0       | 0       | 1       | 0    | 1       | -V <sub>1</sub>                                 |

| 12        | 1                | 1    | 1       | 0       | 0       | 1       | 0    | 1       | - (V <sub>1</sub> +V <sub>2</sub> )             |

| 13        | 1                | 0    | 1       | 0       | 0       | 1       | 1    | 0       | - (V <sub>1</sub> +V <sub>3</sub> )             |

| 14        | 0                | 1    | 1       | 0       | 0       | 1       | 1    | 0       | - (V <sub>2</sub> +V <sub>3</sub> )             |

| 15        | 1                | 1    | 1       | 0       | 0       | 1       | 1    | 0       | -                                               |

|           |                  |      |         |         |         |         |      |         | (V <sub>1</sub> +V <sub>2</sub> +V <sub>3</sub> |

**Table II Switching State For 15 Level Inverter**

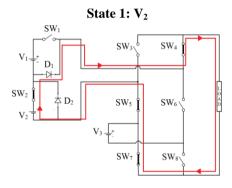

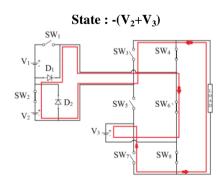

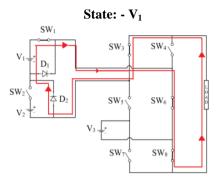

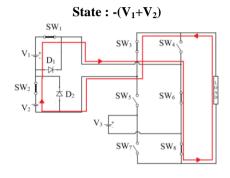

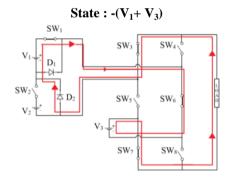

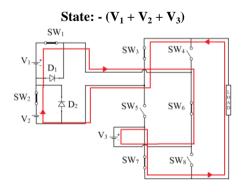

#### IV. STATE OF OPERATION

The current path for different state of output voltages are mentioned

Fig.5.Current Path For Obtaining 1<sup>st</sup>step Output Voltage (Lowest Voltage)

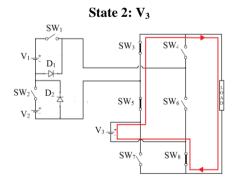

Fig.6.Current Path For Obtaining 2<sup>nd</sup> Step Output Voltage

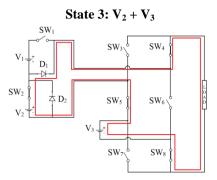

Fig.7.Currvolent Path For Obtaining 3<sup>rd</sup> Step Postive Output Tage

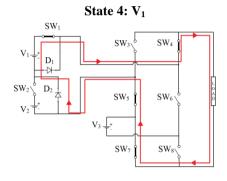

Fig.8.Current Path For Obtaining 4<sup>th</sup> Step Output Voltage (Maximum Of Individual Input Sources)

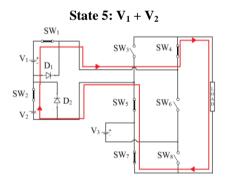

Fig.9.Current Path For Obtaining 5th Step Output Level

Fig.10.Current Path For Obtaining 2<sup>nd</sup> Step Output Voltage

Fig.11.Current Path For Obtaining The Maximum Step Output Voltage

Fig.12.Current Path For Obtaining The Negative Least Step Output Voltage

Fig.13.Current Path For Obtaining The Least Negative Voltage

Fig.14.Current Path For Obtaining 3<sup>rd</sup> Step Negative Output Voltage

Fig.15.Current Path For Obtaining 4<sup>th</sup> Step Negative Output Voltage

Fig.16.Current Path For Obtaining 5<sup>th</sup> Step Negative Output Voltage

Fig.17.Current Path For Obtaining 6<sup>th</sup> Step Negative Output Voltage

Fig.18.Current Path For Obtaining Step Negative Maximum Output Voltage

#### V. SIMULATION RESULTS

## A. Standing Voltage

One of the significant parameter for operating MLI smoothly is the standing voltage[4]. The maximum blocking voltage of the switch is the standing voltage which decides the cost of MLI.

Fig.19. Blocking Voltage Of MOSFET Switches From  $SW_1$  To  $SW_8$

#### **TABLE III**

| Switches                          | Standing Voltages |

|-----------------------------------|-------------------|

| $SW_1$                            | 150 Volts         |

| $SW_2$                            | 38 Volts          |

| SW <sub>3</sub> , SW <sub>4</sub> | 180Volts          |

| SW <sub>5</sub> , SW <sub>6</sub> | 260 Volts         |

| SW <sub>7</sub> , SW <sub>8</sub> | 70 Volts          |

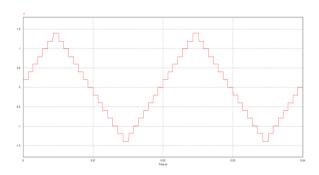

### B. Waveform

The proposed topology is constructed in PSIM tool and output voltage &current waveform are obtained. The simulation tool is implemented by keeping constant input energy sources are  $V_1$ =96 volt,  $V_2$ = 24 volt,  $V_3$ =48 volt, (in terms of ratio 4:1:2) as this paper concentrates more about topology of MLI.

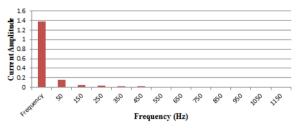

#### C. Total Harmonic Distortion

The presence of harmonic distortion in output leads to increased cost of filtering components, accelerated ageing of equipment due to heating and other harmonic effects.[5,6] The proposed topology gives a THD for current waveform is 2.09% for R-Load.

Fig.20. In Proposed Topology Of 15 Level Inverter PSIM Tool

Fig.21. Current Waveform Of Proposed Topology For R-Load

| Harmonic Order | Frequency | Current Amplitude | Square of<br>current |

|----------------|-----------|-------------------|----------------------|

| 1              | 50        | 1.385240159       |                      |

| 3              | 150       | 0.152901575       | 0.023378892          |

| 5              | 250       | 0.053911748       | 0.002906477          |

| 7              | 350       | 0.031021849       | 0.000962355          |

| 9              | 450       | 0.019175302       | 0.000367692          |

| 11             | 550       | 0.01990896        | 0.000396367          |

| 13             | 650       | 0.01298793        | 0.000168686          |

| 15             | 750       | 0.011271498       | 0.000127047          |

| 17             | 850       | 0.010821154       | 0.000117097          |

| 19             | 950       | 0.008895081       | 7.91225E-05          |

| 21             | 1050      | 0.009752793       | 9.5117E-05           |

| 23             | 1150      | 0.014936585       | 0.000223102          |

| 24             | 1250      | 0.013748234       | 0.000189014          |

|                |           |                   | 0.029010967          |

|                |           |                   | 0.020942915          |

|                |           | THD%              | 2.09429154           |

THD = 2.09 %

# VI. COMPARISON

It is compared with conventional multilevel inverters which give good percentage reduction of switches. [8]

| Components           | NPC | FC | СНВ | SMLI<br>[7] | Proposed topology |

|----------------------|-----|----|-----|-------------|-------------------|

| DC Sources           | 1   | 1  | 7   | 4           | 3                 |

| Diodes               | 12  | 12 | -   | -           | 2                 |

| Capacitors           | 60  | -  | -   | -           | =                 |

| Switching<br>Devices | 24  | 24 | 28  | 13          | 8                 |

#### VII. CONCLUSION

This paper proposes new topology which drastically reduces the use of power electronic components meanwhile reducing the cost of the inverter for SAPS. The proposed MLI has a scope to extend flexibility on design and to optimize the converter for change in input renewable sources.

#### REFERENCES

- R. ShalchiAlishah, D. Nazarpour, S. H. Hosseini and M. Sabahi, "Novel Topologies for Symmetric, Asymmetric, and Cascade Switched-Diode Multilevel Converter With Minimum Number of Power Electronic Components," in IEEE Transactions on Industrial Electronics, vol. 61, no. 10, pp. 5300-5310, Oct. 2014. doi: 10.1109/TIE.2013.2297300

- M. Q. Abbas, A. Majid, J. Saleem and M. Arif, "Design and Analysis of 15-level Asymmetric Multilevel Inverter with Reduced Switch Count using Different PWM Techniques," 2017 International Conference on Frontiers of Information Technology (FIT), Islamabad, 2017, pp. 333-338.doi: 10.1109/FIT.2017.00066

- Rajesh R &MadasamyBalasubramani&JayapalanGowrishankar.

(2013) "Newly-Constructed Single Phase Multilevel Inverter for Distributed Energy Resources" Vol 5 No 2 Apr-May 2013

- N. Vinothkumar, V. Kumar Chinnaiyan, Pradish. M andPrabhakarkarthikeyan, "Multilevel Inverter Structure usingSingle Source and Double Source Module to Reduce PowerElectronics Components", IET The Journal of Engineering, pp. 1-10, March 2017

- J. Gowri Shankar and J. Belwin Edward "Design andImplementation of 15-Level Asymmetric Cascaded H BridgeMultilevel Inverter," Journal of Electrical Engineering, Volume 17 Issue 2,2017

- G. Shankar and J. Belwin Edward, "A 15-level asymmetriccascaded H bridge multilevel inverter with less number ofswitches for photo voltaic system," 2016 InternationalConference on Circuit, Power and Computing Technologies(ICCPCT), Nagercoil, 2016, pp. 1-10.

R. Rajesh, TamilarasuViswanathan, S. Suryaprakash "A Modified

- R. Rajesh, TamilarasuViswanathan, S. Suryaprakash "A Modified Single Phase Multilevel Inverter Topology for Distributed Energy Resources" 2017 Research J. Engineering and Tech 253-258.DOI: 10.5958/2321-581X.2017.00042.3

- Dineshkumar, Premalatha K, Nandhini JJ "ModellingAnd Analysis of Single Stage Single Phase Boost Inverter" International Journal of Pure and Applied Mathematics, Volume 117 No. 8 2017, 89-93. DOI: 10.12732 /ijpam.v117i8.18.

- L.Latha, K.Gayathri Devi," A New Approach To Image Retrieval Based On Sketches using Chamfer Distance", Journal Of Advanced Research In Dynamical And Control Systems, Vol. 9, Sp- 6, 2017, 1959-1968.