# Design and Analysis of High Speed and Low Power Reversible Vedic Multiplier Incorporating with QSDN Adder

# Karanam Deepak.

Abstract: This present work deals with a reversible Vedic type multiplier using the earliest Urdhva Tiryagbhyam sutras of Vedic type mathematics combine with the QSD adder (Quaternary Signed digit number adder). There are three activities be intrinsic into duplication halfway items age, fractional items decrease and expansion. Quick snake design in this way enormously upgrades the speed of the general procedure. A pass on free math errand be able to be cultivated use a top radix number formation, for instance, QSD adder. In QSD, each one number can be address by a digit as of - 3 to 3. Pass on complimentary development as well as distinctive exercises on incalculable, for instance, 64, 128, or more can be executed with consistent deferment and less multifaceted nature. The proposed multiplier configuration is contrasted and a reversible Vedic multiplier consolidates a QSD Quaternary Signed digit number adder viper among a transformation section for quaternary to paired change. The proposition demonstrates a most extreme speed enhancement.

Keywords: Arithmetic Multiplier, Quaternary Signed Digit adder [QSD], UrdhvaTiryagbhyam, Vedic type Mathematics, Carry free addition, QSD, Redundancy.

## I. INTRODUCTION

The basic characteristics that assist us choose the calculation force of a pc is the speediness of its math unit. A basic limit of the number juggling square is increase on the grounds that, in most logical estimations, it shapes most of the implementation period. Thusly, the headway of the speedy multiplier has a result investigate zone used for a extended period[1]. A part of the indispensable figuring's planned for snappy enlargement in a composing are Array multiplier, Booth multiplier, and Wallace multipliers. Vedic type Mathematics is a technique is a number juggling decides to facilitate takes into consideration increasingly proficient executions with respect to speed. Increase in this technique comprises of three stages: age of fractional items, decrease of halfway items, lastly convey spread expansion. Multiplier configuration dependent on Vedic arithmetic has numerous points of interest as the deficient things and totals are made in one phase, which decreases the pass on expansion since least significant bit (LSB) number to most significant bit (MSB) number[2]. These components help in scales the main structure used for greater commitments not including moderately extending the main expansion hold-up since each

### Manuscript published on 28 February 2019.

\*Correspondence Author(s)

**KARANAM DEEPAK**, Department of Electrical & Electronics Engineering, G. Pullaiah College of Engineering and Technology, Kurnool, India.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license <a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>

and every tinier square of the structure work all the while. Vedic multiplier demonstrated upgrades in both the parameters over various structures. Thusly, various use of increment counts subject to Vedic type sutras contains represented inside composing[3]. Vedic type multiplier designs planned composing rely UrdhvaTiryagbhyam type sutras and Nikhilam type sutras of Vedic type Mathematics. After Nikhilam type sutra is gainful designed for wellsprings of information with the purpose of are close up to the force of 10, during the present paper arrangements to execute quick duplication reliant taking place the Urdhva type Tiryagbhyam sutra of Vedic type Mathematics is summed up method for all numbers, has been shown[4. The previous development, pass on induce extension, requires a speedy snake plot since it shapes a bit of the fundamental way. Collections of snake designs contain projected within writing towards enhance the entire execution of the Vedic type multiplier. Snake reliant on Quaternary Signed digit number type adder exhibits the upgrade in speed above former front line adders. Earlier utilization of QSD snake relied upon the Multi Voltage logic or the Multi Value type Logic (MVL). The inconvenience being used of the quaternary type extension exterior the Multiple Voltage justification is so as to, the main snake is the simply a little piece of the main structure and the yields ought towards be changed over backside towards match for additional getting ready. Regardless, usages of the change unit undermine the good conditions grabbed within speed beside with QSD type adder. In the present manuscript, a new execution of the a snake reliant on the adder of QSD type is In which diminishes the pass on expansion interruption of the arrangement through creation make use of of pass on liberated math. The New method of proposed system snake configuration deals with a half and half of double and quaternary number frameworks wherein the total is straightforwardly created in parallel utilizing the idea of a changing piece, wiping out the transformation module. The structure can be scaled to bigger piece usage, for example, 32 bits, 64bits, 128 bits or added through insignificant increment during spread postpone attributable on the way to the affinity plan. We include pre-dominant within the same differentiated present proposed structure and the Vedic type multiplier subject to the New Multi Value type Logic (MVL) method of reasoning that uses a swell pass on snake, the Vedic type Multiplier with the purpose of intertwines a Quaternary Signed digit number adder type adder wind along with a change component used for the quaternary headed for matched change,

Vedic type multiplier with the aim of utilizes cutting edge quick viper plan, for example, Carry select snake and a generally utilized quick duplication instrument, for example,

Booth multiplier, to demonstrate the plausibility of our structure crosswise over imperative correlation focuses[2.

The tip top of the special adders be necessary ever since the speediness of the device pc depend upon the energetically taking place the speediness of the special type adders used in the structure. Moreover, it fills in while a structure hunk designed for blend of all other calculating assignments. Special types of Adders are generally used in different electronic application for example Propelled processing of signal dealing with within special type of the adders are used on the way to execute distinctive counts like finite impulse responses, Infinite Impulse Response, etc. In precedent, the critical test designed for the VLSI circuit's fashioner is near to decrease region of the VLSI chip with use viable enhancement strategies. By then the accompanying stage near to manufacture the speediness of the action towards reach snappy calculation similar to the present microchips a considerable number of rules are played out each moment of second[5]. The system speediness of the movement is the critical necessities within organizing Digital signal processor. The unemployment related through checked digits of the numbers offer the probability of the pass on free of charge extension. The main overabundance gave during the checked number depiction considers brisk extension and subtraction in light of the way that the total or qualification and a digit is nothing but a segment of the simply and the two digits bordering digit number spots the main operands used for a radix number more conspicuous than the two, and three neighbouring digit number position used for a radix number of two. Thusly, main incorporate time intended for two let go stamped the digit numbers are a relentless self-ruling of the main length of the word operands, in the best approach to quick count. The main benefit of pass on liberated development obtainable by adders of QSD numbers can be used in abused in arranging a quick snake circuit. In addition of snake organized with the adders of QSD number structure has a standard plan which is sensible for VLSI utilization which is the exceptional good position over the RBSD wind[6]. An Algorithm for plan of Quaternary Signed digit number adders wind is projected. Twofold checked digits of the numbers are known to allow compelled pass on spread with a reasonably continuously complex extension process requiring tremendous circuit for utilization. An uncommon upper radix number based (quaternary) depiction of the matched stamped digit of the numbers are not simply allow the pass on free of charge development as well as get free of charge elimination yet what's more offers other fundamental central focuses, for instance, ease in reason and higher amassing thickness.

# II. PROPOSED ARCHITECTURE

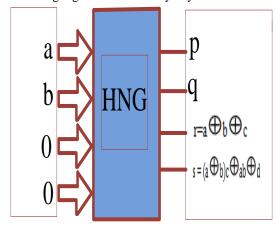

The proposed architecture of multiplier engineering circuit having total two sections. Fundamentally, the main fractional items be practiced utilizing AND doors. The acknowledgment of HNG system entryway as the logic gate of AND door have been completed whenever input system vectors of the HNG door is the Input Vector (IV) there mentioned as (0, 0, a, b), the yield of the vectors

determination of the Output Vectors is (s=ab, r=ab, q=b, p=a). In this manner S yield gives the intelligent articulation of the logic gate of AND door as the inputs are c and d seem to be '0' logic. The Figure 1 shows the demonstrates HNG gate door as logic gate of AND entryway.

Figure 1: HNG gate as AND gate

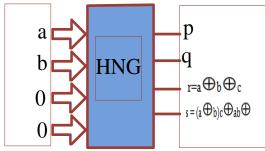

In an imperative segment is the main HNG door is to facilitate a type reversible full viper and the circuit be able to planned used by the utilizing a solitary type of HNG entryway. Whenever the input type of the vectors of the HNG are IV (0, a, b, cin), and the yield vectors resolve the OV (s=count, r=sum, q=cin, p=a). Subsequently it can be conceivable to obtain the both aggregate & convey yields. In main acknowledgment of the reversible type of full viper utilizing the logic gate of the HNG entryway can be executed & appeared in the of Figure 2. The previously mention the full snake circuits utilizes the solitary type of the HNG entryway. Out of four yields, entirety & convey be created in the two yields and the remaining two yields are waste yields. Snake is a crucial unit of the multiplier; therefore it has high effect all in all execution of the framework in respects with power utilization, postponement and region inhabitance.

Figure 2: Full adder using HNG gate

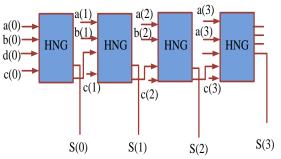

It the apparent from the Figure 2 to facilitate three quantities of the 4 bit swell convey adders are required to plan 4 bit twofold multiplier architecture. The main outline of the 4 bit twofold snake utilizing the logic of HNG entryway is appeared in Figure 3 with utilizing 4 total HNG doors.

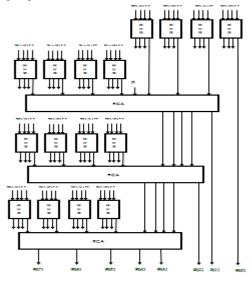

**Figure 3: Ripple carry adder (4 bit) using HNG gate** Our proposed 4bit twofold multiplier utilizing reversible rationale doors is shown in Figure 7. This design is touched base from figure 3 by making the accompanying changes:

- (i) Replacing logic gates of the AND gates with HNG gates shown in Figure 4.

- (ii)(ii) Replacing full adders with 4 bit HNG gates using ripple carry adders shown in Figure 3.

the main changes of the proposed system is the better results of high speed systems and very low power and also having less complexity of the hard ware implementation.

In [22], 4x4 multiplier utilizing reversible rationale entryways was proposed. Yet, they utilized Peres entryway for fractional item figuring. The reproduction consequences of these two multiplier circuits are talked about in the following segment.

Figure 4: Proposed architecture 4\*4 reversible Vedic Multiplier Architecture

# III. PROPOSE ALGORITHM OF THE QSD ADDER

In QSD number framework convey engendering chain are disposed of which diminish the calculation time significantly, henceforth enhancing the speed of the mechanism. The extent of number of QSD is from - 3 to 3, the extension outcome of two QSD numbers is vary from - 6 to +6. In Table I represent the yield meant for each probable blend of the total 2 numbers. And the numbers of the decimal form in the extent of from the value of - 3 to the +3 to be addressed by single digit of the QSD number. The decimal system number outperforms starting this scope; so having more than single digit of the QSD number is necessary. The main extension

results, which are in the extent of the - 6 to the +6, the total two QSD digits are mandatory. The two digits are the QSD architecture results of the LSB digit addresses the all out piece and the MSB digit addresses the pass on bit. To keep this pass on bit to incite from the position is from lower to higher digit position of the QSD architecture number depiction is used as the main structure. the architecture of the QSD numbers allows abundance within the number depictions. A comparable decimal number can be addressed in more than one QSD depictions. So we pick such QSD addressed number which deflects further undulating of pass on. To perform pass on free extension, the development of two QSD numbers ought to be conceivable in two phases:

**Stage 1**: First step creates a middle of the road convey and moderate aggregate from the information QSD digits i.e., numbers to be added and augend.

**Stage 2**: Second step joins middle whole of current digit with the transitional convey of the lower huge number.

Therefore the extensions of the two QSD architecture numbers are completed in two stages. Primary period of snake produces widely appealing pass on and midway whole from the data digits.

Secondary period of snake incorporates the centre total of the present number through the moderate pass on of the inferior colossal number. To clear the additional undulating of the pass on readily available are total two policies to achieve QSD extension in the two phases:

**Guideline 1**: The First one is the standard expresses with the purpose of the greatness of the middle of the road entirety must be not exactly or equivalent to the number two therefore the numbers should be  $\,$  in the scope of from the digit  $\,$  -  $\,$  2 to the digit  $\,$  +2.

**Guideline 2**: And the Second principle expresses with the purpose of the extent to the middle conveys be obliged to be not exactly otherwise equivalent to the number 1 i.e., it can be ought to the scope of from the digit -1 to the digit +1.

As demonstrated by these two standards the transitional total and widely appealing pass on from the underlying advance QSD snake be capable of contain the extent of from the digit of - 6 to the digit +6. Nevertheless, through manhandling by the reiteration characteristics of the QSD architecture numbers can be pick such a QSD addressed and the number can be satisfy the recently referenced total two measures. Right In the second step of the QSD wind incorporates of the entire of the present digit, which is the level of from the digit - 2 to the digit +2, through the midway pass on the lower basic digit of the system, which is the level of the digit from - 1 to the digit of +1, and the final extension outcome can't be the more vital than the 3 that is the extent of from the digit of -3 to the digit of +3. And the present development of the result can be addressed as a single digit QSD number. Accordingly no additional pass on is necessary. In the first stage of the QSD snake, and the extent of the yield is from the digit of -6 to the digit of +6 and this can be addressed within the moderate pass on in addition to the entire structure of QSD configuration because of showed up in the table I.

And we can be discovering within the foremost fragment of the Table I and a couple of figures have diverse depictions, yet simply those that meet the above portrayed two models are picked. The picked widely appealing pass on and moderate entire are recorded within the final area of the Table I is nothing but a QSD architecture coded number.

TABLE I: The sum and carry of the proposed system from -6 to -6

| SUM | QSD represented       | QSD coded        |  |

|-----|-----------------------|------------------|--|

|     | number                | number           |  |

| -6  | 22,12                 | 12               |  |

| -5  | <b>2</b> 3, <b>11</b> | 11               |  |

| -4  | <u>1</u> 0            | <u>1</u> 0       |  |

| -3  | $\bar{1}1,0\bar{3}$   | 11               |  |

| -2  | 12,02                 | 02               |  |

| -1  | 13,01                 | 01               |  |

| 0   | 00                    | 00               |  |

| 1   | 01,13                 | 01               |  |

| 2   | 02,12                 | 02               |  |

| 3   | 03,1                  | 1 <mark>1</mark> |  |

| 4   | 10                    | 10               |  |

| 5   | 11,2 <mark>3</mark>   | 11               |  |

| 6   | 12,22                 | 12               |  |

### IV. IMPLEMENTATION OF THE SINGLE DIGIT PROPOSED OSD ADDER UNIT

In this system there are having two phases connected with pass on liberated development. And the underlying advance creates a center pass on and aggregate from the numbers to be included. And final next step combine the widely appealing aggregate to the present term of the number through the pass on of the lesser basic digit. Towards keep pass on starting additional undulating, there are two gauges are described. And the essential choose means that the degree of the widely appealing total should be not actually otherwise equivalent to 2. And the next standard communicates with the purpose of the span of the pass on required to be not actually or comparable to 1. Along these lines, and main significance to the next step yield can't be present more conspicuous than the 3 which can be able to addressed by the singular digit of the QSD number; from now on additional pass on is necessary. In the stage 1, of the each and every one achievable information sets of the numbers to be included and augend are considered. To oust the further pass on multiplication and the dismissal characteristic of the QSD based numbers is used. And We keep the depiction to such that a degree, to the point that all the midway passes on are compelled to a most outrageous of 1, and the widely appealing wholes are constrained to be under 3, by then the last development will advance toward getting to be pass on without charge. And the main QSD type depictions to the precepts are shown in Table I in favour of the extent of the digit from - 6 to the digit of +6. Because of the extent of the moderate pass on is in the form of from the digit number - 1 to the digit number +1, and its might be present addressed in the form of two bits of twofold integers anyway we obtain the main three bit depiction used for the bit closeness of the transitional total. And the data side of the numbers to be added value (a<sub>i</sub>) can be addressed by the value of 3 the variables of the commitments since a<sub>0</sub>, a<sub>1</sub>, a<sub>2</sub> and the augends of the value Bi is addressed by 3 variable commitment as b<sub>0</sub>, b<sub>1</sub>, b<sub>2</sub>. And the yield part of the midway pass on IC is addressed by I<sub>C0</sub>, I<sub>C1</sub>,I<sub>C2</sub>, and the transitional total is addressed by I<sub>S0</sub>, I<sub>S1</sub>, I<sub>S2</sub>. And total six variable

enunciations used for moderate pass on and widely appealing aggregate similar to wellsprings of data  $(b_0,b_1,b_2,a_0,a_1)$  and  $a_2$ can be gotten from Table I. Therefore we obtain the total six yield verbalizations for the I<sub>C0</sub>, I<sub>C1</sub>,I<sub>C2</sub>, I<sub>S0</sub>, I<sub>S1</sub>, I<sub>S2</sub>. Because of the widely appealing pass on be capable of the addressed by only contains total two bits; and the final third attached piece I<sub>C2</sub> value is proportional to the value of I<sub>C1</sub> therefore the verbalization designed for the two yields resolve proportionate. And then the using of the K-map operations of the basic logic operations is specified in the minimum hardware recognition for generate the middle and the carry of the intermediate state of the sum are copied. and the min terms of the intermediate state carry is  $(I_{C0}, I_{C1}, I_{C2})$  are:

$$IC_{2} = a_{2}b_{2}(\overline{a_{0}b_{0}a_{1}b_{1}}) + (\overline{a_{1} + b_{1}})(a_{2}\overline{b_{0}} + b_{2}\overline{a_{0}})$$

$$IC_{1} = a_{2}b_{2}(\overline{a_{0}b_{0}a_{1}b_{1}}) + (\overline{a_{1} + b_{1}})(a_{2}\overline{b_{0}} + b_{2}\overline{a_{0}})$$

$$IC_{0} = IC_{2} + \overline{a_{2}b_{2}}(a_{1}b_{1} + b_{1}b_{0} + b_{0}a_{1} + b_{1}a_{0} + a_{1}a_{0})$$

Minterms for intermediate sums are:

$$IS_{0} = a_{0} \overline{b_{0}} + \overline{a_{0}} b_{0}$$

$$IS_{1} = (a_{1} \overline{b_{1}} + \overline{a_{1}} b_{1}) \overline{a_{0}} b_{0} + (\overline{a_{1}} \overline{b_{1}} + b_{1} \overline{a_{1}}) a_{0} b_{0}$$

$$IS_{2} = IS_{0} ($$

$$\overline{a_{1}} b_{1} + a_{1} \overline{b_{1}}) + b_{2} \overline{a_{1}} b_{0} + a_{2} \overline{b_{1}} a_{0} + a_{0} b_{0} \overline{a_{1}} b_{1} (a_{2})$$

The last total which is convey free is created from those yields for example Middle convey (Ico, Ic1, Ic2) and Intermediate aggregate (I<sub>S0</sub>, I<sub>S1</sub>, I<sub>S2</sub>). During the way there are six information and three yield state bits.

$$S_{0} = IC_{0}\overline{IS_{0}} + \overline{IC_{0}}IS_{0}$$

$$S_{1} = IC_{1} \bigoplus IS_{1} \bigoplus IC_{0}IS_{0}$$

$$S_{2} = IC_{2} \bigoplus IS_{2} \bigoplus (IC_{1}IS_{1} + (IC_{1} \bigoplus IS_{1}) + IC_{0}IS_{0})$$

In this paper, a clever thought of a viper, in light of QSD type of the adder is proposed. And the calculation used for the projected viper utilizes an half and half of the quaternary in addition to the parallel type of number frameworks. And the yields as of humbler multipliers operations are gotten like twofold type of strings. In the interior the extension unit, of the string is broken down into the parts of quaternary digit of two bits each one.

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) 276 © Copyright: All rights reserved.

Development using the proposed QSD type empowers to the diminish to the pass on spread deferral by making use of pass on free number juggling for example In the quaternary digit they are not having swell past in the pass unit. And especially designed for superior piece of the input part strings this technique be incredibly beneficial. And the final Intermediate total lies on the choice of the (0, 6), because of the main operands are nothing but an unidentified numbers. In the type of quaternary extension towards the pass on free of charge past the principle arrange, and widely appealing entire can't have more conspicuous than the value of 2. By certify this requirement stays steady, the main depiction of the 3 ought to the picked though the including. Nevertheless, the addresses a block the circumstance while changing in the course of the last yield string by and by into twofold because of confines from basically in quaternary yield the interfacing the lower two bits strings to get the combined proportionate.

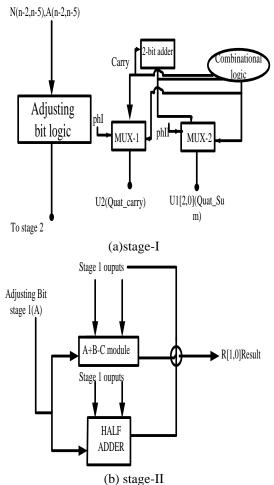

Fig. 5: Proposed type of Adder

there are having total two stages in the proposed type of the adder as shown in the figure 5.

1) **Stage1:** The Stage-I block diagram is as shown in the figure 5(a) the each and every step of different digits are in the same position of the quaternary type depiction of the two n-bit numbers A and B can be added by using the adder unit then we get the value of sum. So the sum is lies between the range of (0,6). The sum obtain from the adder unit, and the intermediate state of sum and intermediate state of carry used for the subsequent stage can be calculate the parallel operation by using the 2x1 state of the operations of multiplexers. And the change the bit value is added in the figure of the parallel operation circuit having the optional type procedure. And the main role to the varying piece figure

hinder used for each one quaternary type of digit development in the earlier period of the two quaternary type of digits of  $a_n$  and b expected by the value of (n-2: n-5).

2) **Stage1:** The Stage-II block diagram is as shown in the figure 5(b). these stage having the total two type of modules. In the first module is the one-piece type of module. it plays the calculation part of the value is (a + bc). so this condition An ultimate LSB bits of the middle of the road total, and B can be convey as of the past quaternary type of digit expansion and the value of C is the varying bit. And the other type of the module can be a half viper and which will include the convey as of the (a+b-c) the module and the specified bit to the one side of the slightest noteworthy piece of the middle of the road aggregate. With respect to the last connection, the sign piece would not be utilized inferable from the alterations proposed in the structure. In this way, its last esteem isn't figured.

#### V. SIMULATION RESULTS

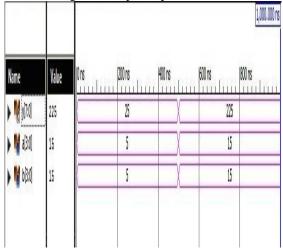

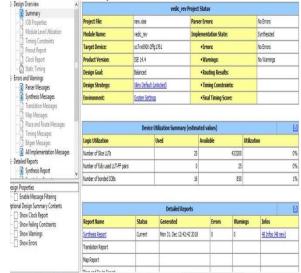

The 4X4 bit vedic type of multiplier is intended by with reversible logic gates using HNG gates. All these modules designed in Verilog HDL and then simulated and synthesized these modules using Xilinx ISE 14.4.

In the simulation result the inputs are taken as a=0101 and b=0101 then we get the output as p=00011001.

Figure 6: Proposed type of four bit multiplier simulation result

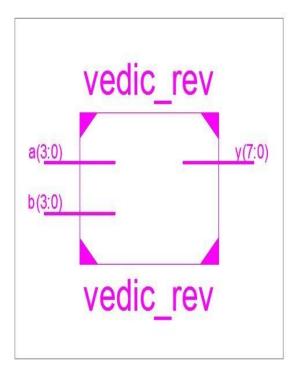

Figure 7: Proposed type of four bit multiplier block diagram And the main block diagram of the 4X4 multiplier is designed and the generated block diagram from the Xilinx tool is shown in the fig 6.

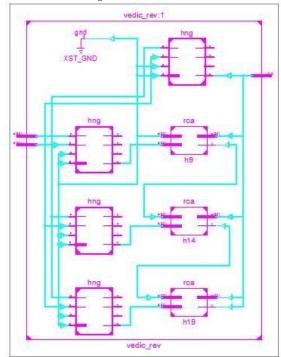

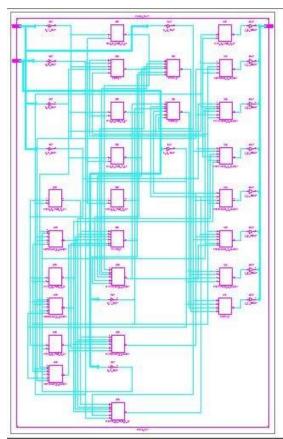

Figure 8: Proposed type of four bit multiplier RTL diagram The RTL schematic of the proposed 4X4 multiplier is obtained by using the Xilinx tool and it is shown in fig 8.

Figure 9: Technology schematic of the proposed 4-bit multiplier

The technology schematic of the proposed 4X4 multiplier is designed by using the Xilinx tool and here the schematic consists of the look up tables.

Figure 10: Summary report of the proposed 4-bit multiplier

# Table I Comparison between Reversible Vedic multiplier using QSDN and Reversible Vedic multiplier

|           | Delay | Static   | Dynamic   | Lut's |

|-----------|-------|----------|-----------|-------|

|           |       | power    | power     | coun  |

|           |       | consumpt | consumpti | t     |

|           |       | ion      | on        |       |

| Reversib  |       |          |           |       |

| le vedic  | 3.298 | 0.110 W  | 3.997 W   | 21    |

| multiplie | ns    |          |           |       |

| r using   |       |          |           |       |

| QSDN      |       |          |           |       |

| Reversib  |       |          |           |       |

| le vedic  | 3.486 | 0.111 W  | 4.079 W   | 25    |

| multiplie | ns    |          |           |       |

| r         |       |          |           |       |

#### VI. CONCLUSION

It very well may be reasoned that the structure when scaled to higher bits just demonstrates a minimal ascent in postponement because of its center qualities. Initially, the parallelism associated with its fractional item age. Besides, decrease of convey engendering delay in the novel snake it joins. Because of the utilization of QSD, the structure can consolidate convey free number juggling while at the same time killing radix change module speed overhead by incorporating idea of modifying bit rationale in its design. The proposed plan is focused towards computerized frameworks requiring high from first to last place and a very low inertness from the expense of territory slide. Multipliers assume a key job in deciding the speed of the framework. Correspondingly, this design would be a decent possibility to be executed as an extensive piece of frameworks like DCT methods, CPU (Central Processing Unit), multiply and Accumulate (MAC) Unit, Image Processors where fast augmentations are basic to the execution of the framework. It can likewise be seen that in spite of the target of diminishing the deferral, the proposed plan performs superior to anything most structures thought about as far as power.

#### REFERENCES

- S. TahmasbiOskuii, P. G. Kjeldsberg, and O. Gustafsson, "Transition activity aware design of reduction-stages for parallel multipliers," in Proc. 17th Great Lakes Symp.On VLSI, March 2007, pp. 120–125.

- M. Perkowski, P. Kerntopf, A. Buller, M. Chrzanowska-Jeske, A. Mishchenko, X. Song, A. Al-Rabadi, L. Jozwiak, A. Coppola and B. Massey, "Regular realization of symmetric functions using reversible logic", in Proceedings of EUROMICRO Symposium on Digital Systems Design (Euro-Micro'01), Warsaw, Poland, pp. 245–252, September 2001

- Ayman A. Fayed, Magdy A. Bayoumi, "A Novel Architecture for Low Power Design of Parallel type of Multipliers," wvlsi, pp.0149, IEEE Computer Society Workshop on VLSI 2001.

- C.-Y. Han, H.-J.Park, and L.-S. Kim. A low-power array multiplier using separated multiplication technique. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing. vol.48, pp. 866-871 (2001)

- S. Shah, A. Al-Khalili, and D. Al-Khalili. Comparison of 32-bit multipliers for various performance measures. Proceedings of the 12th IEEE International Conference on Microelectronics, (2000)

- K. Thakre, S. S. Chiwande and S. D. Chafale, "Design of low power multiplier using reversible logic gate," 2014 International Conference on Green Computing Communication and Electrical Engineering (ICGCCEE), Coimbatore, 2014, pp. 1-6.

- M.Anitha, A.Rajani, N.Pushpalatha, "Optimized multiplier using reversible logic gates: a vedic Mathematical approach", (IJARCET) Volume 3 Issue 10, October 2014.

- 8. Gowthami P, RVS Satyanarayana, "Design of Digital Adder Using Reversible Logic", IJERA, Vol. 6, Issue 2, (Part - 1), pp.53-57, February 2016.

#### **AUTHOR PROFILE**

design.

KARANAM DEEPAK Received the B.Tech degree in Electrical and Electronics Engineering from Prakasam Engineering College, Kandukuru, Prakasam (DT),A.P.India,in 2013.He has completed M.Tech in Power Electronics and Drives from VNR Engineering College,Ponnuru,Guntur (DT),A.P, India . Currently working as a Assistant Professor in G. Pullaiah College of Engineering and Technology since last one year. And his areas of interest are Power Systems, Electrical machines, Electrical Circuits and VLSI

Retrieval Number: D2741028419/19©BEIESP