# Design and Comparison of Different 4:2 Compressors Based on 180nm Technology

Sri Laxmi.P, B. Kumar Sanjiv, Vandana Khare

Abstract --- Many of the circuits such as portable devices, digital signal processing filters, compressors are basic building block for high performance. Different logic types of 4:2 compressors are designed and their performance is computed. The new design uses, different logic style which cut down power consumption and delay. For getting high speed and consuming less power, the new compressor are proposed which consists of eight transistors (8T) XOR-XNOR unit. Different models get designed and simulated using Cadence Virtuoso tool (180nm). From simulation results we reached the improvement of less power consumption, speed of proposed 4:2 compressors.

Keywords: 4:2 compressor, eight transistors(8T),logic styles, Virtuso Cadence tool, power consumed.

#### 1. INTRODUCTION

Today's scenario portable devices have a prominent role in semiconductor industry which in turns to lot of demand for multimedia based applications. Most of digital systems like (digital signal processors, filters,  $\mu$  processors etc) are using efficient compressors (High speed). The project aim is to design a 4:2 compressor which takes less power consumption and perform with less delay. And the capital Objective of the paper is to explain about different styles of compressor designs and their simulation results.

To reducing the operands, while adding partial products the compressors are introduced in multiplication process. Three main stages in multiplication are first stage is to generating the partial product, second stage is to reduce the partial product and the last stage is computation of product. The input for 4:2 compressors as four partial products and the output as reduced to two partial products and critical path delay is also deducted. The proposed designofa4:2compressor has four multiplexers on transmission logic gate and eight transistors.

#### 2. DIFFERENT STYLES OF 4:2 COMPRESSORS

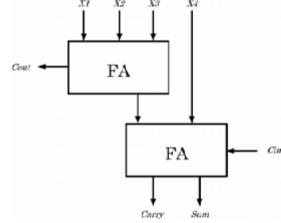

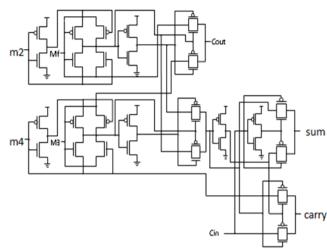

## a. Compressor using 2 full adders

The module has input signals (x1, x2, x3, x4 and  $C_{\rm in}$ ) and output as Sum and Carry as shown in fig 1(a). The  $C_{\rm in}$ signal is doesn't affect the

$C_{out}.Sum = x1 \oplus x2 \oplus x3 \oplus x4(1)$

Carry= Majority [

$$\{x1 \oplus x2 \oplus x3\}$$

,  $x4$ ,  $C_{in}$ ] (2)

$C_{out} = Majority(x1, x2, x3)$  (3)

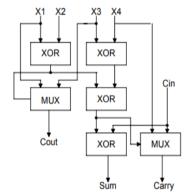

The full adders are constituent of XOR blocks and multiplexers and also from the above equations we can calculate delay from the equation  $4*\Delta$ -XOR gates as shown in Fig .1(b)

## Revised Manuscript Received on March 02, 2019.

**Sri Laxmi.P,**Asst.Professor,ECE Department, CMR College of Engineering & Technology, Hyderabad, Telangana, India

**B. Kumar Sanjiv**, Asst.Professor,ECE Department, CMR College of Engineering & Technology, Hyderabad, Telangana, India

**Dr. Vandana Khare,** Professor, ECE Department, CMR College of Engineering & Technology, Hyderabad, Telangana, India

Fig1. (a) Conventional method of 4:2 compressor

Fig1. (b) 4:2 compressor internal structure of two full adders

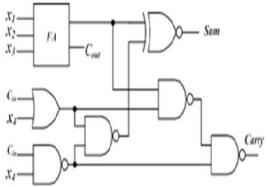

b. 4:2 compressor using full adder, OR, NAND, & XNOR gates

The second style of compressor consists of adder units and gate units such as (NAND, XNOR, ORgates and Full Adder Unit) as shown in figure 2. In this module twofull adders are connected serially. Where  $C_{\rm in}$ , x1, x2, x3 and x4 are inputs, whereas Sum and carry as outputs.

Fig 2. 4:2 compressor using NAND, XNOR, OR and two full adders.

In most of the platforms this gate level module design are process. One of the important criteria for any market is time to facilitated hardware but drawback it is to limited optimization capability.

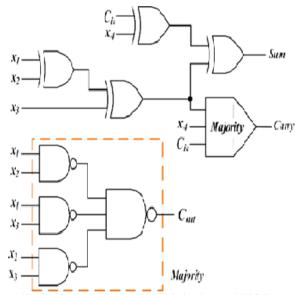

### c. Compressor using Majority & XOR gates

The compressor using Majority & XOR gates are presented in figure 3. To form a three input XOR gate we are cascading 2 input XOR gates.

Fig3. Compressor using Majority and XOR gates

By the simulations we come to know that it is good energy efficient structure.

#### 3. IMPLEMENTATION

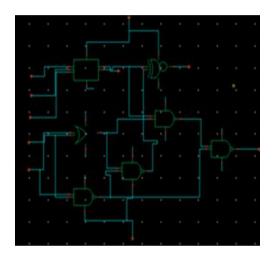

## Proposed compressor

A new layout comprises of transmission logic (four Multiplexers), six transistor (6T) XNOR inverter and two 8T (eight transistors)XOR-XNORunits. For getting good result in speed, full potential swing we have to use XNOR gate operation in this layout and also it consumes less power.

Fig4.Proposed Compressor diagram

The transistors mp1 and mn1 are generates the output which is complement of Y input. The transistors mn2 and mp2 are controlled by the output of (mn1&mp1 transistors). The output of second inverter will produce voltage degradation problem for two combinations (x=0, y=1) and x=1, y=1 to avert fault we are introducing two more transistors mp3 and mn3.

- 1. X=0, Y=0: mp1 and mp2 are ON, logic output is high

- 2. X=0, Y=1: mp2, mp3, mn1 and mn3 are ON logic output is low.

- 3. X=1, Y=0: mp1 and mn2 are ON logic output is low.

- 4. X=1, Y=1: mp3, mn1, mn2 and mn3 are ON logic output is high.

In this layout multiplexer3 generates an inverted output for given in input. Input for multiplexer1 and multiplexer2 are the XOR-XNOR cell output. The multiplexer2 and its complement are given to multiplexer4 (Carry generator).

## 4. RESULTS

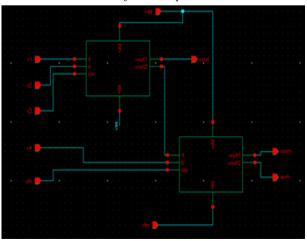

Following are different styles of 4:2 compressors schematics and results. Fig 5.a is about conventional model of compressor result and schematic and result.

Conventional method of 4:2 compressor

Fig 5.a Conventional Compressor Schematic and Output

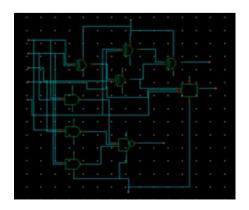

Compressor using two full adders, NAND, OR and XNOR gates

Fig 5.b is about Compressor using two full adders, NAND, OR and XNOR gates of result and schematic and result.

Fig 5.b 4:2 Compressor Schematic and Output Compressor using Majority and XOR gates

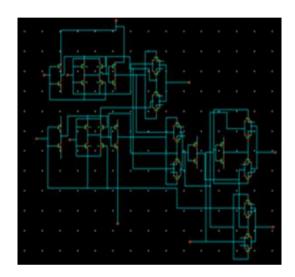

Fig 5.c is about Compressor using Majority and XOR gates of result and schematic and result.

Fig 5.c Schematic and Output of 4:2 Compressor

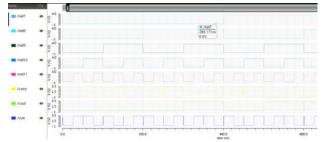

Proposed Compressor

Fig 5.d is about proposed compressor of result and schematic and result.

Fig 5.1.d 4:2 Compressor Schematic and Output

Table 1. Different styles of power consumption of 4:2 compressors in  $\mu W$  and delay in Nano seconds are compared

| Different styles<br>Compressors   |        | POWER<br>(Micro<br>Watts) | DELAY<br>(Nano sec) |

|-----------------------------------|--------|---------------------------|---------------------|

| Conventional<br>Compressor        | method | 74.96                     | 400.5               |

| Compressor using NAND, OR and XNO |        | 98.51                     | 400.6               |

## Design And Comparison Of Different 4:2 Compressors Based On 180nm Technology

| Compressor using Majority & XOR gates | 142.4 | 400.5 |

|---------------------------------------|-------|-------|

| Proposed Compressor                   | 23.26 | 400.2 |

The result for above proposed module with givenvoltageof 3.3 V, an average powercut down by the newcompressor is  $23.26\mu W$  and the superlative delay is 400.2ns

#### 5. CONCLUSION

The proposed layout consequently attains the reduced power consumption and less delay using 36 transistors. For achieving the good energy-efficient compressor reduced transistor area is proposed. Comparing with previous designs the proposed module achieved less no. of transistors, cut down area and high energy efficiency. As result for above modules with givenvoltageof3.3V, anaveragepowercut down by the proposed compressor is  $23.26\mu$ W and the superlative delay is 400.2ns.

#### REFERENCES

- Rathisha Shetty ,and Mr.Mahesh B.Neelagar, " Design and Implementation of High Performance 4-bit Dadda Multiplier using Compressor", , International Journal of Computer Science and Mobile Computing (IJCSMC), Vol.6 Issue.7, July- 2017

- Manish Kumar and Jonali Nath, "Performance analysis Comparison of 4:2 Compressors in 180nm CMOS Technology," IOP Conf. Series: Materials Science and Engineering 225 (2017) 012138 doi:10.1088/1757-899X/225/1/012138

- S. Vasu Krishna and K. Lal Kishore," Efficient Implementation of 18t Compressor For Multiplier Applications", International Journal of Latest Trends in Engineering and Technology (IJLTET) Special Issue-ICRACSC-2016.

- Ajit Pal, "Low Power VLSI Circuits and systems" Springer India 2015

- D.Sasirekha, D.L.Jayanthi and S.Udaya Kumar "Low Area and High Speed Vedic Mathematics Multiplier using Compressor", International Journal for Scientific Research & Development Vol.2, Issue 12,2015 | ISSN (online):2321-0613

- 6. Abdoreza Pishvaiea\*,Ghassem Jaberipurb,c and Ali Jahanianb" High-performance CMOS(4:2) compressors "Article in International Journal of Electronics.November 2014

- S. Kumar and M. Kumar, "4-2 Compressor design with New XOR-XNOR Module," 4th International Conference on Advanced Computing & Communication Technologies (ACCT), pp. 106-111, 2014.

- H. Kaul, et al., "A 320 mv 56 w 411 gops/watt ultra-low voltage motion estimation accelerator in 65 nm cmos," IEEE Journal of Solid-State Circuits, vol. 44, pp. 107-114, 2009.

- Nirlakalla Ravi, S. Venkateswarlu and T. Jayachandra Prasad "A Comparative Performance Analysis of Low Power Bypassing Array Multipliers", I.J. Information Technology and Computer Science, 2013.

- 10. Sreehari Veeramachaneni, Kirthi Krishna M,Lingamneni Avinash, Sreekanth Reddy Puppala , M.B. Srinivas Centre for VLSI and Embedded System Technologies. International Institute of Information Technology Gachibowli, hyderabad-500032, India."Novel Architectures for HighSpeed and Low-Power 3-2, 4-2 and 5-2 Compressors"20th International Conference on VLSI Design 0-7695-2762-0/07 \$20.00 © 2007

- 11. Meon nand D. Radhakrishnan, "High performance 5: 2 compressor architectures" IEE Proc.-Circuits Devices Syst., Vol. 153, No. 5, October 2006.

- K. Prasad and K. K. Parhi, "Low-power 4-2 and 5-2 compressors," 35th Asilomar Conference on Signals, Systems and Computers, vol. 1, pp. 129-133, 2001.

- 13. Jorge Tonfat, Ricardo Reis, "Low Power 3-2 and 4-2 Adder Compressors Implemented Using ASTRAN", South Symposium on Microelectronics,pp.1-6.

Srilaxmi.P is presently working as an Assistant Professor at CMRCET, Hyderabad. She has received M.Tech (Embedded Systems) from JNTU Hyderabad. She has more than 7 years of experience in the field of teaching. She

has published 3 research papers in journals & Conferences of national/international repute. Her areas of interest include VLSI System design and Embedded systems.

B.Kumar Sanjiv is presently working as an Assistant Professor at CMRCET, Hyderabad. He has received M.Tech (Digital Electronic and Communication System) from JNTUH Telegana. He has more than 8 years of

teaching experience. He has published around 4 research papers in journals & Conferences of national/international repute. His areas of interest include VLSI System design, Communication and Embedded systems.

Dr. Vandana Khare working as Professor in CMR College of Engineering & from JNTU Hyderabad (T.S), M.E (Digital Technology in ECE department. She completed her PhD in Communication Engineering techniques) in

1999 from SGSITS, INDORE (M.P) India and B.E in ECE in the year 1994 from GEC Rewa (M.P). She has 20 years of teaching experience. She has published 27 research papers in International journals &presented 05 papers in National & International conferences. She is life member of ISTE & IETE Technical societies. Her research Interest includes computer networks, mobile computing and Bio-medical imaging.