# Radix 4 Fast Fourier Transform Using New Distributive Arithmetic

# Guduguntla Sandeep, S.P.V.Subba Rao

Abstract—Fast Fourier Transform is a standout amongst the most productive changes in DSP tasks. Proficiency of FFT is constrained through the velocity of equipment multipliers of DSP components. Not with standing, to enhance the effectiveness of FFT's programmable models give plausibility to expand the execution of computerized framework by abuse of parallelisms of actualized calculations. This paper exhibits an outline of 16 point radix 4 complex FFT center utilizing NEW disseminated arithmetic Mean. The proposed plan has change regarding equipment usage contrasted with conventional strategies. It is simulated and synthesized by utilizing Xilinx ISE 13.2.

#### 1. INTRODUCTION

Advanced Signal Processing (DSP), because of hazardous development in wired and remote systems and in sight and sound, speaks to one of the most blazing zones in gadgets. Application territories, for example, computerized flag handling, interchanges, and so on utilize advanced frameworks which carryout complex functionalities. Equipment effective and control proficient structures for these frameworks are most required to accomplish greatest execution. Quick Fourier Transform (FFT) is a standout amongst the mainly productive approaches to actualize Discrete Fourier Transform (DFT) because of its decreased use of number juggling gadgets. DFT is this type of principal contraptions that are utilized for the recurrence research of discrete time indicators plus to communicate to a discrete time organization in recurrence field utilizing its type assessments. Because of expanded usability of FFT in present day electronic frameworks, superior radix FFTs, for example, radix – four, radix – eight, radix – 2k, opening radix, and so forth are intended for improved planning plus diminished equipment. The essential distinction of the specified strategies lies in the define of their butterfly elements are Conveyed.

Arithmetic has transformed into an amazing device to actualize duplicate and aggregate unit in numerous computerized flag handling frameworks. It dispenses with the requirement of a Multiplier this is utilized as a chunk of MAC detail. DA actualizes MAC detail thru pre-processing every single conceivable item and by putting away them utilizing a read just memory. Utilization of ROM can be dispensed with on the off chance that one arrangement of the data sources has a settled esteem. This is finished with circulating the coefficients to the contributions of the unit. This process is known as NEW Disseminated Arithmetic (NEDA). Along

#### Revised Version Manuscript Received on 05 April, 2019.

**Guduguntla Sandeep,** PG Scholar, Vlsi And Embedded Systems, Sreenidhi Institute of Science and Technology, Yamnampet, Ghatkesar, Ranga Reddy, Telangana. India.

**Dr. S.P.V.Subba Rao** Professor, Department of ECE, Sreenidhi Institute of Science and Technology, Yamnampet, Ghatkesar, Ranga reddy, Telangana. India.

these lines, utilising NEDA, several MAC like detail could also be entire simply by means of utilising adders plus shifters. Engineering plans make use of both DA strengthen or CORDIC unit solution to address actualizes FFT, which contain ROM as en most important unit within the define. The deliberate procedure is dependent upon NEDA, which does now not necessitate any ROM accordingly producing the plan to have reduced apparatus. The conveyance of the coefficients is completed ideally to in addition decrease the repetitive gadget elements.

#### 2. LITERATURE SURVEY

## A NEW Disseminated Arithmetic Architecture plus its Appliance to One Dimensional Discrete Cosine Transform.

Common disseminated Arithmetic (DA) is well recognized in ASIC outline plus it consists of on-chip ROM to participate in fast plus normality. In this dissertation, another DA design referred as NEDA is planned gone for lessening the outlay measurements of intensity plus region while keeping up fast and exactness in Digital Signal Processing @SP) appliances. Numerical examination demonstrates that NEDA can actualize inward result of vectors as 2's supplement numbers utilizing just augmentations, trailed by few movements at the last stage. Relative investigation demonstrates that NEDA beats broadly utilized methodologies, for example, MAC and DA in numerous perspectives. Being a rapid design free of ROM, increase p subtraction, NEDA can likewise uncover the excess obtainable in the snake cluster comprising of sections of 0 and 1. An equipment pressure plot is acquainted with produce a butterfly structure with least number of increments.

# Dispersed arithmetic based performance of Fourier transform targeted at FPGA architectures

Discrete Fourier change is perceived as one of the fundamental advanced flag preparing tasks. A standout amongst the most proficient techniques for playing out this change is quick Fourier change (FFT). It has been demonstrated that no calculation for registering the DFT server have a littler multifaceted nature than the FFT. Therefore most FPGA usage depends on this methodology. Through the presentation of particular DSP squares installed into programmable structures the effectiveness of FFT is restricted by the velocity of equipment multipliers of DSP components.

# Radix 4 Fast Fourier Transform Using New Distributive Arithmetic

Be that as it may, programmable models give probability to build the execution of advanced framework by abuse of parallelisms of actualized calculations. In this paper use of dispersed number-crunching idea to DFT execution is depicted.

# 3. MATHEMATICAL ARTICULATIONS FOR PROPOSED OUTLINE

NEW Disseminated Arithmetic (NEDA) strategy is being utilized in numerous advanced flag handling frameworks that necessitate MAC element. Changes, for example, FFT, DCT, and so forth have numerous augmentations that thus require various multipliers.

#### A. Mathematical Derivation Of Nedawc.

Scientific inference of NEDA is as per the following.

Think about the accompanying aggregate of

$$Y = \sum_{k=1}^{L} A_k \times X_k \quad , \tag{1}$$

items:

whereAk are settled coefficients, and the Xk are the info information words. On the off chance that both the Ak and Xk are in 2's supplement organize, then Ak might be communicated as:

$$A_k = -A_k^M 2^M + \sum_{i=N}^{M-1} A_k^i 2^i , \qquad (2)$$

where Aik = 0 or 1 , I = N, N + 1, . . . , M, and A? is the sign piece, plus An: is the slightest noteworthy piece (LSB). We allude to (M-N+I) ay DA exactness. Joining (1) plus (2) yields:

$$Y = \sum_{k=1}^{L} \left( -A_k^M 2^M + \sum_{i=N}^{M-1} A_k^i 2^i \right) X_k$$

$$= -\left[ \sum_{k=1}^{L} A_k^M X_k \right] 2^M + \sum_{i=N}^{M-1} \left[ \sum_{k=1}^{L} A_k^i X_k \right] 2^i$$

$$= -(Y^M \cdot 2^M) + \sum_{i=N}^{M-1} (Y^i \cdot 2^i) ,$$

(3)

Where

$$Y_i = \sum_{k=1}^{L} A_k^i X_k$$

,  $i = N, N+1, \dots, M$ .

Condition (3) can be modified in network item as

$$Y = \begin{bmatrix} A_1 & A_2 & \cdots & A_L \end{bmatrix} \begin{bmatrix} X_1 \\ X_2 \\ \vdots \\ X_L \end{bmatrix}$$

$$= \begin{bmatrix} 2^N & 2^{N+1} & \cdots & 2^M \end{bmatrix} \begin{bmatrix} A_1^N & A_2^N & \cdots & A_L^N \\ A_1^{N+1} & A_2^{N+1} & \cdots & A_L^N \\ \vdots & \vdots & \cdots & \vdots \\ -A_1^M & -A_2^M & \cdots & -A_L^M \end{bmatrix} \begin{bmatrix} X_1 \\ X_2 \\ \vdots \\ X_L \end{bmatrix}$$

$$= \begin{bmatrix} 2^N & 2^{N+1} & \cdots & 2^M \end{bmatrix} \begin{bmatrix} Y_1^N \\ Y_1^N \\ \vdots \\ -Y_M \end{bmatrix},$$

(4)

Where

$$Y^{i} = \begin{bmatrix} A_{1}^{i} & A_{2}^{i} & \dots & A_{L}^{i} \end{bmatrix} \begin{bmatrix} X_{1} \\ X_{2} \\ \vdots \\ X_{L} \end{bmatrix}$$

(5)

By presenting an administrator IMP), (4) can be

additionally improved as

$$Y = \begin{bmatrix} 2^{N} 2^{N+1} & \cdots & 2^{M} \end{bmatrix} \begin{bmatrix} 1 & 0 & \cdots & 0 & 0 & 0 \\ 0 & 1 & 0 & \cdots & 0 & 0 \\ 0 & 0 & 1 & 0 & \cdots & 0 \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ 0 & 0 & 0 & \cdots & 1 & 0 \\ 0 & 0 & 0 & \cdots & 0 & INV(\cdot) \end{bmatrix} \cdot \begin{bmatrix} A_{1}^{N} & A_{2}^{N} & \cdots & A_{L}^{N+1} \\ A_{1}^{M+1} & A_{2}^{M+1} & \cdots & A_{L}^{M+1} \end{bmatrix} \begin{bmatrix} X_{1} \\ X_{2} \\ \vdots & \vdots & \vdots & \vdots & \vdots \\ A_{1}^{M-1} & A_{2}^{M-1} & \cdots & A_{L}^{M-1} \end{bmatrix} \begin{bmatrix} X_{1} \\ X_{2} \\ \vdots \\ X_{L} \end{bmatrix}$$

$$= \begin{bmatrix} 2^{N} 2^{N+1} & \cdots & 2^{M} \end{bmatrix} \begin{bmatrix} 1 & 0 & \cdots & 0 & 0 & 0 \\ 0 & 1 & 0 & \cdots & 0 & 0 \\ 0 & 0 & 1 & 0 & \cdots & 0 \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ 0 & 0 & 0 & \cdots & 0 & INV(\cdot) \end{bmatrix} \begin{bmatrix} Y_{N+1} \\ Y_{N+1} \\ \vdots \\ Y_{M} \end{bmatrix}$$

$$INV(B) = INV \begin{pmatrix} \sum_{k=R}^{S} B^{k} \cdot 2^{k} \\ k=R \end{pmatrix} + 1 \cdot 2^{R} ,$$

$$(7)$$

what's more, B is number in the 2's supplement arrange. Reminder that in (6), lattice An is the appropriated number juggling (DA) grid of settled coefficients Ak, where  $k=1,2,\ldots$ , L. [A] is significant to NEDA since its arrangement can prompt reserve funds in equipment to execute the calculations. It just comprises of 0's plus 1's, calculation of

$$\begin{bmatrix} Y^{N} \\ Y^{N+1} \\ \vdots \\ Y^{M} \end{bmatrix} = [A] \begin{bmatrix} X_1 \\ X_2 \\ \vdots \\ \vdots \\ X_L \end{bmatrix}$$

(8)

involves just expansion activities. Along these lines, we allude to [A] as the Adder Array. Furthermore, administrator ZNV(.) includes just tasks of reversal and expansion, subsequently for the network calculation

$$\begin{bmatrix} 1 & 0 & \dots & 0 & 0 & 0 \\ 0 & 1 & 0 & \dots & 0 & 0 \\ 0 & 0 & 1 & 0 & \dots & 0 \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ 0 & 0 & 0 & \dots & 1 & 0 \\ 0 & 0 & 0 & \dots & 0 & INV(\cdot) \end{bmatrix} \begin{bmatrix} Y^N \\ Y^{N+1} \\ \vdots \\ Y^M \end{bmatrix}$$

(9)

jn (6) 2's supplement equipment is essential (adder plus inverters). The last phase of processing Y, as indicated by (6),

$$Y = \begin{bmatrix} 2^{N} \ 2^{N+1} & \cdots & 2^{M} \end{bmatrix} \left\{ \begin{bmatrix} 1 & 0 & \cdots & 0 & 0 & 0 \\ 0 & 1 & 0 & \cdots & 0 & 0 \\ 0 & 0 & 1 & 0 & \cdots & 0 \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ 0 & 0 & 0 & \cdots & 1 & 0 \\ 0 & 0 & 0 & \cdots & 0 & INV(\cdot) \end{bmatrix} \begin{bmatrix} Y^{N} \\ Y^{N+1} \\ \vdots \\ Y^{M} \end{bmatrix} \right\}$$

can be acknowledged with moving and expansion. By and large, by utilizing NEDA, internal result of vectors (1) can be actualized with fundamental cells of snake.

#### A. Radix 4 FFT

The N-point DFT of an information grouping X(k) is characterized as

$$X(k) = \sum_{n=0}^{N-1} x(n) W_N^{kn}, \quad 0 \le k \le N-1$$

$$W_N = e^{-j2e/N}$$

At the point when N is an intensity of two, the FFT dependent on the Cooley – Tukey calculation is most ordinarily utilized with the end goal to register the DFT effectively. The Cooley – Tukey calculation diminishes the quantity of activities (N2)for the DFT to (N log2N) for the FFT. As per this the FFT ascertained in a progression of n=logp N stages where p is the base of the radix. The other famous calculation is the radix-4 FFT, or, in unique words strong than the radix-2 FFT. The radix-4 FFT circumstance is recorded.

$$X(k) = \sum_{n=0}^{N-1} \left[ x(n) + (-j)^k x \left( n + \frac{N}{4} \right) + (-1)^k x \left( n + \frac{N}{2} \right) + (j)^k x \left( n + \frac{3N}{4} \right) \right] W_N^{pk}$$

beneath:

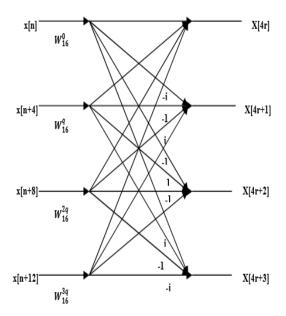

Fig. 1 Radix 4 Butterfly structure

The radix-4 FFT condition basically consolidates pair phases Of a radix-2 FFT into one, with the intention that 1/2 the identical quantity of tiers is major (see Figure2). For the reason that the radix-four FFT calls for a lot less degrees plus butterflies than the radix 2 FFT, the calculations of FFT is also moreover made strides. For example, to compute a sixteen-factor FFT, the radix-2 obtains log216=4 organizes yet the radix-4 obtains just log416=2 stages. Next, we talk about the numerical issue that emerges from a limited length issue. The vast majority utilize a settled direct DSP toward play out the figuring in their implanted framework on the grounds that the settled point DSP is exceptionally programmable and is cost effective. The downside is that the settled point DSP has restricted powerful range, or, in other words the summation flood issue that happens all the time in

FFT. A plan is expected to defeat this issue. This prompts the meaning of the twiddle factors as

$$\omega_N^{nk} = e^{-j2\pi nk/N}$$

#### 4. DESIGN OF FFT USING NEDA

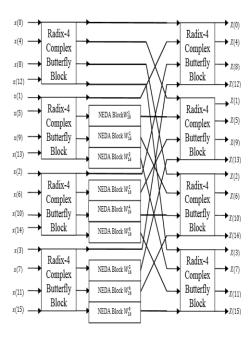

On this dissertation, we projected the execution of 16point compound FFT utilising radix-four technique. Composite duplications foremost amid the procedure became actualized via utilising NEDA. As in preserving with the radix-four sixteen-point FFT, calculation, to actualize radix-4butterflies are compulsory. Four radix-four butterflies are applied within the main set up plus the alternative 4 being utilized within the next/ultimate measure. The info is bought in day-to-day request plus the yield in bit-inversion hooked up. The yield of each radix-four butterfly is accelerated thru the certain twiddle explanations. In the indicated rectangular chart, the essential step incorporates of four radix-4 butterflies. The contributions to the butterflies are x(n), x(n+4), x(n+8), x(n+12) wherever n is 0 for first butterfly, 1 for subsequent butterfly, 2 for the following butterfly, plus three for the final butterfly, all of earliest step. The deal with motives are specified by  $W_{16}^0$ ,  $W_{16}^q$ ,  $W_{16}^{2q}$ ,  $W_{16}^{3q}$  where q is 0 for butterfly. As planned in our plan, the intricate handle

motives are specified by 16, 16, 16, 16 where q is 0 for butterfly. As planned in our plan, the intricate handle increases compulsory at the step-1 yield have been actualized via utilizing NEDA squares. In favored nine NEDA squares are obligatory on the yield of earliest part of the sixteen point FFT CPU.

In this step, 4 extra radix-4 butterfly squares are applied. The principal radix-four butterfly within the subsequent step obtains the important yield of the four radix-4 butterfly squares applied within the number one step. The 2nd radix-4 butterfly in the second step obtains the next yield of the 4 radix-4 butterfly squares pursued via the NEDA square (every time compulsory). This fashion proceeds for the closing radix-four butterfly squares furnish inside the 2nd step. There is no necessitating of utilizing any NEDA avert after 2nd step on account that the twiddle hindrance that is 1 is accelerated to the yields of the subsequent step. The ultimate yield arrives in somewhat-inversion arrange. The upside of utilizing radix-4 calculation is that it holds the effortlessness of radix-2 calculation plus confers the yield with slighter intricacy. The NEDA rectangular considered within the planned square graph does the intricate broaden of the yield of the predominant step plus the specified twiddle part.

## Radix 4 Fast Fourier Transform Using New Distributive Arithmetic

Fig.2 Block diagram of 16 point FFT architecture

#### 5. RESULTS

Result of the planned design is implemented using Xilinx ISE for simulation and Synthesis.

#### Simulation.

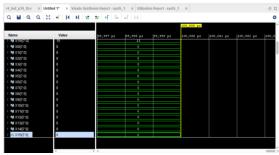

Fig. 3 Input Simulation.

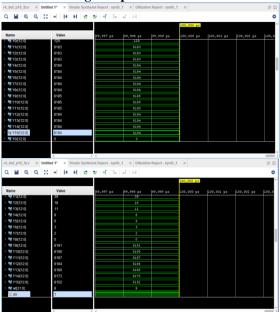

Fig. 4 Output Simulation.

#### Synthesis Result:

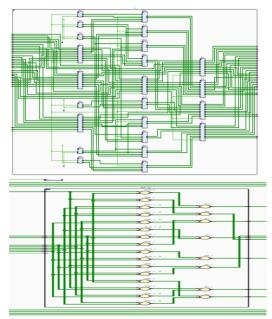

Fig. 5 RTL Schematic.

## 6. CONCLUSION

The projected dissertation certain design of 16-point radix-four intricate FFT center using NEDA that's a ROM much less plus multiplier much less method. The projected plan is productive as far as equipment when contrasted with other customary strategies. The proposed plan has been executed on various FPGAs to analyze the execution measurements.

#### REFERENCES

- Stanley A. White, "Applications of Distributed Arithmetic to Digital Signal Processing: A Tutorial Review," IEEE ASSP Magazine, vol. 6, no. 3, pp. 4 – 19, Jul. 1989.

- Wendi Pan, Ahmed Shams, and Magdy A. Bayoumi, "NEDA: A NEw Distributed Arithmetic Architecture and its Application to One Dimensional Discrete Cosine Transform," Proc. IEEE Workshop on Signal Processing Syst., pp. 159 – 168, Oct. 1999.

- M. Rawski, M. Vojtynski, T. Wojciechowski, and P. Majkowski, "Distributed Arithmetic Based Implementation of Fourier Transform Targeted at FPGA Architectures," Proc. Intl. Conf. Mixed Design, pp. 152 – 156, Jun. 2007.

- S. Chandrasekaran, and A. Amira, "Novel Sparse OBC based Distributed Arithmetic Architecture for Matrix Transforms,", Proc. IEEE Intl. Sym. Circuits and Syst., pp. 3207 – 3210, May 2007.

- Richard M. Jiang, "An Area-Efficient FFT Architecture for OFDM Digital Video Broadcasting," IEEE Trans. Consumer Elect., vol. 53, no. 4, pp. 1322 – 1326, Nov. 2007.

- Alban Ferizi, BernhardHoeher, Melanie Jung, Georg Fischer, and Alexander Koelpin, "Design and Implementation of a Fixed-PointRadix4 FFT Optimized for Local Positioning in Wireless Sensor Networks," Intl. Multi-Conf. Syst. Signals and Devices, pp. 1 – 4, Mar. 2012.

- 7. Li Wenqi, Wang Xuan, and Sun Xiangran, "Design of Fixed-Point High-Performance FFT Processor," Intl. Conf. Edu. Tech. and Comput., vol. 5, pp. 139 143, Jun. 2010.