# A Low Power 8-Bit Current-Steering DAC Using **CMOS** Technology

# P.Ramakrishna, M. Nagarani, K. Hari Kishore

Abstract: Design of 8-bit current-steering DAC is proposed in this paper. The 800 MHz conversion rate has been obtained by a fully custom designed new architecture. With the operating voltage of 1V and 180nm CMOS technology this DAC is designed. The power dissipation is of 42.92uw which is very low. The DAC will thus create a "stair stepping" analog output until digital input is met or the voltage supply is reached. The measured integral non linearity (INL) is less than ±0.31LSB and the static differential non-linearity error (DNL) is ±0.418 LSB.

Keywords: DAC, current steering, Current mirror, cascade.

#### I. INTRODUCTION

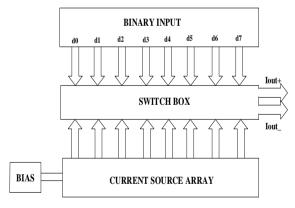

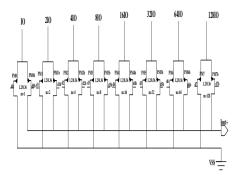

The digital to analog converter is a system to convert digital signal to analog signal. It is widely used in digital signal processors. DAC'S are often used to convert finiteprecision time series to a varying physical data. These are mainly used in different applications like audio amplifier, video amplifier, display electronics, data acquisition systems, data distribution systems. Current steering DAC's are the more commonly used architectures because of their small size and simplicity, high resolution and high speed. The architecture diagram of current steering DAC(CS-DAC) is shown in figure 1.

Fig. 1 Proposed CS-DAC architecture

8-bits binary weighted are the inputs of architecture. Based on the binary principle current sources are scaled. Here the i<sup>th</sup> current source output current is equal to the 2<sup>1</sup>.I, Where  $I=I_{LSB}$ , i.e., least significant bit(LSB)current.

#### Revised Manuscript Received on April 14, 2019.

P.Ramakrishna, Research Scholar, Department of ECE, Koneru Lakshmaiah Educational Foundation, Vaddeswaram, Guntur, Andhra

M. Nagarani, Professor, Department of ECE, Koneru Lakshmaiah Educational Foundation, Vaddeswaram, Guntur, Andhra Pradesh, India, Anurag Group of Institutions, Hyderabad, India

K Hari Kishore, Professor, Department of ECE, Koneru Lakshmaiah Education Foundation, Vaddeswaram, Guntur, A.P. India

N-bit binary weighted CS-DAC output voltage in ideal case is given by

$$V_{\text{out}} = -V_{\text{ref}} \sum_{i=0}^{n} b_i \frac{1}{2^{i+1}}$$

(1)

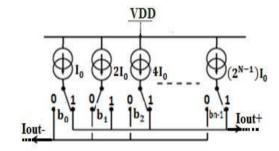

For the design of DAC the best way is to associate the CMOS switches in place of current sources weighted. Here for N-bit converter, the N current sources are used, those are represented as:  $I_0$ ,  $2I_0$ ,  $4I_0$  and  $(2^{N-1})I_0$ . The switches designed with CMOS technology acts as a current sources weighted are shown in figure 2.

Fig. 2 DAC at switched current source

The output current is:

$$I_{out+} = (B_0 + 2B_1 + 4B_2 + \dots + 2^{N-1} B_{N-1})I_0$$

(2)

$$I_{\text{out+}} = KI_0 \tag{3}$$

And, its complementary":

$$\begin{split} I_{\text{out-}} &= (B_0 + 2B_1 + 4B_2 + \dots + 2^{N\text{-}1} \; B_{N\text{-}1}) I_0 \\ I_{\text{out-}} &= (2^N\text{-}1\text{-}K) I_0 \end{split} \tag{4}$$

$$I_{\text{out-}} = (2^{N} - 1 - K)I_{0} \tag{5}$$

The total I<sub>tot</sub>current drawn by the converter is:

$$I_{tot} = I_{out-} - I_{out+} = (2^{N} - 1)I_0$$

(6)

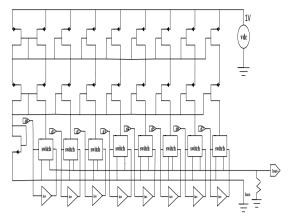

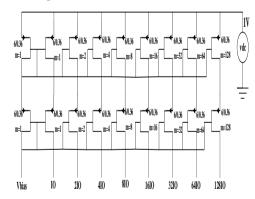

## II. ARCHITECTURE OF CS-DAC

The architecture which is proposed in this paper explains the low power CS-DAC which is based on the two blocks in that one is current mirror circuit and the other is switches. where all the widths of all MSB'S and LSB'S are same for current source transistors. The complete schematic of proposed design CS-DAC is shown below figure 3.

137

# A Low Power 8-Bit Current-Steering DAC Using CMOS Technology

Fig. 3 Proposed CS-DAC schematic

The blocks used in this proposed architecture are:

Binary inputs, the block switches, current array sources, biasing voltages and filter.

# 1. Inputs

Here the binary inputs are used to control the switchers by using the PMOS logic signals d0, d1, d2, d3, d4, d5, d6 and d7 and also with their components d0b,d1b, d2b, d3b, d4b, d5b, d6b and d7b.

#### 2. Switches

In this design the current coming from all the eight array sources are aligned by using this block switches as the output iout+ and iout-. And also controls the signals coming from the binary input. The ON/OFF characteristics at the branches of the DAC can be controlled by using this block switches as shown in figure 4. The dynamic characteristics are improved by keeping the switching times are equal to the current passing through the branches. The MOS transistor size is inversely proportional to the switching time. MOS switch corresponding to LSB is minimum and for MSB is maximum which is 128 times greater.

Fig. 4 schematic of the switch

Here the switches are designed simply by using PMOS transistors as shown in the below figure. These switches can be designed as pairs to form a differential pairs. The power source cutting is completely restricted by using this differential pair. Here the DAC output iout+ is mainly concentrated by connecting iout- to the ground as shown in figure 5.

Fig. 5 the switches used in CS-DAC

#### 3. Array of current sources

The current array sources are used to deliver the currents at 8 orders of switches which is equal in value. The design of these weighted current sources is easy technology using CMOS process. If the sources of units are combined with 2,4,8,... then easily avoid the noise.. The unitary sources are shown in figure 6.

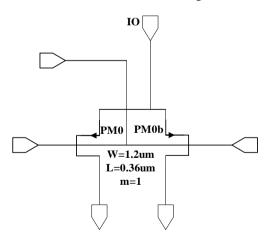

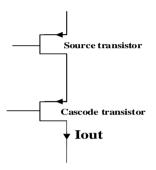

Fig. 6 Current Source

The current sources used in the DAC with the cascade sources are shown in below figure 7. Where the output is improved compared to the current mirror.

Fig. 7 The current source used in CS-DAC

## 4. Biasing voltages

The reference voltage is generated by using this block, which is represented as Vbias to polarize the PMOS current mirror cascades. The binary input signals d0 to d7 and their complements d0b to d7b control these PMOS switches. Here the D0 is the least significant bit (LSB) and D7 is the most significant bit.

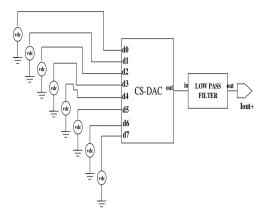

#### 5. With Filter

The CS-DAC with filter circuit is shown in below figure 8.

Fig. 8 The CS-DAC with filter circuit

The main purpose of the filter is to remove the some unwanted components from the signals. There are different kinds of filters are present. Here the low pass filter is used to smoothen the resulted signal output.

#### III. RESULT

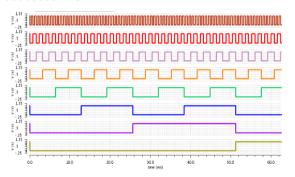

Figure 9 shows the binary inputs (d0, to d7) of DAC from 8'b00000000 to 8'b11111111.

Fig. 9 inputs of CS-DAC 1LSB =  $\frac{1V}{256 \text{ bits}}$  = 3.9V

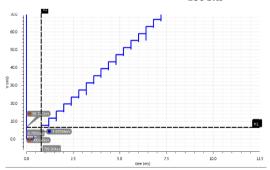

Fig. 10 Stair case output of CS-DAC Results

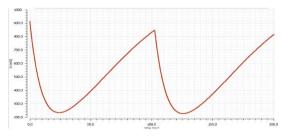

Fig. 11 simulation results of 8-bit CS-DAC after filter with 800MHz

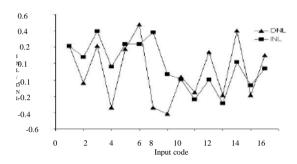

The offset, gain error and DNL and INL calculations are described below.

**INL/DNL:** The integral non linearity is the one which is used to measure the performance of the DAC's and ADC's after the offset and gain errors are compensated. The differential non-linearity is the one which is also used to measure the performance by measuring the real and ideal widths at each level of the converter. INL/DNL plot is illustrated in figure 12.

Fig. 12 INL/DNL plot at 800MHz

The transistors of source are selected by adjusting the lengths and widths to meet the specifications those are INL and DNL. Here the saturation voltage is closer to the transistor voltage VDs.

#### **DAC Specifications**

Table, 1

| PARAMETERS         | CS-DAC (PROPOSED) |

|--------------------|-------------------|

| Process            | GPDK 0.18um       |

| Supply voltage     | 1V                |

| Resolution         | 8-bit             |

| Full scale current | 31.252mA          |

| LSB size           | 246.594μA (1LSB)  |

| Conversion rate    | 800MHz            |

| Power dissipation  | 42.92uW           |

| INL (LSB)          | ±0.3 (LSB)        |

| DNL (LSB)          | ±0.718 (LSB)      |

# IV. CONCLUSION

In this paper the design of low power 8-bit current steering DAC by using CMOS technology is presented. The test results are obtained with low power with high performance with frequency of 800MHz. The DAC's are mainly used in wide range of applications like digital audio applications, data communication applications and other types of applications.

### REFERENCES

139

- Zhi-Yuan Cui, Hua-Lan Piao, and Nam-Soo Kim, "A 10-bit Current steering DAC in 0.35-µm CMOS Process", Transactions On Electrical And Electronic Materials, Vol. 10, No. 2, April 25, 2009.

- Mircea Tomoroga, Lucian Jurca, "Study of Matching Errors in Unit Element Approach of Current-Steering Segmented DAC Design", 6th WSEAS International Confeence on System Science and Simulation in Engineering, 2007.

## A Low Power 8-Bit Current-Steering DAC Using CMOS Technology

- Eulalia Valestrieri, "Some Critical Notes on DAC Time Domain Specifications Instrumentation and Measurement", Technology Conference, Italy, April, 2006.

- Jurgen Deveugele, Michiel S.J.Steyaert, "A 10-bit 250-MSPS Binary-Weighted Current-Steering DAC", IEEE Journal of Solid-State Circuits, Vol-41, No.2 Feb,2006.

- J. Huynh, B. Ngo, M. Pham, and L.He, "Design of a 10-bit TSMC 0.25um CMOS Digital to Analog Converter", Proceedings of the 6th international Symposium on Quality Electronic Design-2005.

- J Jacob Wikner, "Studies on CMOS Digital-to-Analog Converters", Dissertation No. 667, Linköping Studies in Science and Technology, 2001

- A. V.d. Bosch, M. S. J. Steyaert, and W. Sansen, "Solving Static and Dynamic Performance Limitations for High Speed D/A Converters," Proc. of the 10th Workshop on Advances in Analog Circuit Design, Apr. 2001.

- R. Jacob baker, harry w. Li, and D.E. Boyce, "CMOS circuit design, layout, and simulation," the institute of electrical and electronics engineers, inc., New York, 1998.

- Farzan, K., Johns, D.A., "A power-efficient architecture for high-speed D/A converters," Proc. 2003 Int. Symp. Circuits and Systems, pp. 1897–1890, May, 2003.

- Jung J, Baek K H, Lim S I, et al, "Design of a 6bit 1.25GS/S DAC for WPAN," Proc Int Symp Circuits and Systems, 2008:2262.

- Tony Chan Carusone, David A. Johns, Kenneth W. Martin "ANALOG INTEGRATED CIRCUIT DESIGN", 2nd ed. Printed in the United States of America, 2011.

- Phillip E. Allen and Douglas R. Holberg, CMOS Analog Circuit Design. Second Edition. Prentice-Hall, 2002.

- Rasavi Behzad, "Principles of Data Conversion System Design", pp 63-69, 79-94, Piscataway N.J., IEEE Press, 1995.

- Sam Blackman Professor Robert Brodersen A Low Power, 8-bit, 200 MHz Digital-to-Analog Converter.

- Helna Aboobacker, Aarathi R Krishna, Remya Jayachandran, "Design, Implementation and Comparison of 8 Bit 100 Mhz Current Steering Dacs," International Journal of Engineering Research and Applications (IJERA), pp.881-886, Vol. 3, Issue 4, Jul-Aug 2013.

- Mostafa, C. and Q. Hassan, "1GS/s,Low Power Flash Analog to Digital Converter in 90nm CMOS Technology," IEEE conference on Multimedia Computing and Systems (ICMCS), 2012 International, pp 1097–1100.

- Mostafa, C. and Q. Hassan, "Design of a Low Power, High Speed Analog to Digital Pipelined Converter for High Speed Camera CMOS using 0.18μm CMOS Technology," Australian Journal of Basic and Applied Sciences, February 2015.

- 18. Yadlapati, A., Kakarla, H.K. An Advanced AXI Protocol Verification using Verilog HDL (2015) Wulfenia, 22 (4), pp. 307-314.

- Bindu Bhargavi, K., Hari Kishore, K. Low Power Bist on Memory Interface Logic (2015) International Journal of Applied Engineering Research, 10 (8), pp. 21079-21090.

- Charan, N.S., Kishore, K.H. Recognization of delay faults in cluster based FPGA using BIST (2016) Indian Journal of Science and Technology, 9 (28).

- Hari Kishore, K., Aswin Kumar, C.V.R.N., Vijay Srinivas, T., Govardhan, G.V., Pavan Kumar, C.N., Venkatesh, R.V. Design and analysis of high efficient UART on spartan-6 and virtex-7 devices (2015) International Journal of Applied Engineering Research, 10 (9), pp. 23043-23052.

- Kante, S., Kakarla, H.K., Yadlapati, A. Design and verification of AMBA AHB-lite protocol using Verilog HDL (2016) International Journal of Engineering and Technology, 8 (2), pp. 734-741.

- Bandlamoodi, S., Hari Kishore, K. An FPGA implementation of phase-locked loop (PLL) with self-healing VCO (2015) International Journal of Applied Engineering Research, 10 (14), pp. 34137-34139.

- 24. Murali, A., Hari Kishore, K., Rama Krishna, C.P., Kumar, S., Trinadha Rao, A. Integrating the reconfigurable devices using slow-changing key technique to achieve high performance (2017) Proceedings 7th IEEE International Advanced Computing Conference, IACC 2017, art. no. 7976849, pp. 530-534.

- A. Surendar, K. H. Kishore, M. Kavitha, A. Z. Ibatova, V. Samavatian "Effects of Thermo-Mechanical Fatigue and Low Cycle Fatigue Interaction on Performance of Solder Joints" IEEE Transactions on Device and Materials Reliability, P-ISSN: 1530-4388, E-ISSN: 1558-2574, Vol No: 18, Issue No: 4, Page No: 606-612, December-2018.

- 26. N Bala Dastagiri K Hari Kishore "A 14-bit 10kS/s Power Efficient 65nm SAR ADC for Cardiac Implantable Medical Devices"

- International Journal of Engineering and Technology (UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 34-39, March 2018.

- N Bala Dastagiri, Kakarla Hari Kishore "Reduction of Kickback Noise in Latched Comparators for Cardiac IMDs" Indian Journal of Science and Technology, ISSN No: 0974-6846, Vol No.9, Issue No.43, Page: 1-6, November 2016.

- 28. N Bala Dastagiri, K Hari Kishore "Analysis of Low Power Low Kickback Noise in Dynamic Comparators in Pacemakers" Indian Journal of Science and Technology, ISSN No: 0974-6846, Vol No.9, Issue No.44, page: 1-4, November 2016.

- 29. Avinash Yadlapati, Hari Kishore Kakarla "Design and Verification of Asynchronous FIFO with Novel Architecture Using Verilog HDL" Journal of Engineering and Applied Sciences, ISSN No: 1816-949X, Vol No: 14, Issue No: 1, Page No: 159-163, January 2019.

- Meka Bharadwaj, Hari Kishore "Enhanced Launch-Off-Capture Testing Using BIST Designs" Journal of Engineering and Applied Sciences, ISSN No: 1816-949X, Vol No.12, Issue No.3, page: 636-643, April 2017.

- Dr. Seetaiah Kilaru, Hari Kishore K, Sravani T, Anvesh Chowdary L, Balaji T "Review and Analysis of Promising Technologies with Respect to fifth Generation Networks", 2014 First International Conference on Networks and Soft Computing, ISSN:978-1-4799-3486-7/14,pp.248-251, August 2014.

- 32. P Bala Gopal, K Hari Kishore, R.R Kalyan Venkatesh, P Harinath Mandalapu "An FPGA Implementation of On Chip UART Testing with BIST Techniques", International Journal of Applied Engineering Research, ISSN 0973-4562, Volume 10, Number 14, pp. 34047-34051, August 2015.