# Electrical Characteristics of Double Gate FINFET Under Different Modes of Operation

# K.Sarath Chandra, K Hari Kishore

Abstract: CMOS scaling has provided the enhancement of VLSI industry for its miniaturization of devices as well as increase in the operating speed at the expense of power dissipation. The three metrics of VLSI industry speed, area and power are interlinked to each other such that one metric has to be compromised for another metric to have better value depending on which particular application to be targeted. Furthur sclaing of cmos is not possible because of material and process technology limits. Because of second order effects prevailing in CMOS researchers are looking for alternative replacement for CMOS which overcomes the second order effects existing in CMOS scaling and provide very less power dissipation. Now a day's power dissipation is very crucial parameter because of miniaturization of devices a feature called portability came in to picture where battery is essential requirement. The battery technology has not evolved as much as the VLSI technology as evolved over the years which has left no option for the designers to design the devices which consume less power and give more battery life which is the most primary requirement from customer point of view. In this regard FINFET is found to be one of the right substitute for CMOS to design the applications which are targeted to have low power delay product. FINFET electrical characteristics are plotted under different modes of operation and leakage currents are compared for N-Type and P-type FINFETs, and concluded that back gate biasing reduces leakage currents.

Keywords: FinFET, MOSFET, 32 nm Technology, Power, Speed

# I. INTRODUCTION

In the VLSI industry, both Arithmetic and Logic lowpower circuits have become very important. Due to the rapid increase in the usage of the portable electronic devices, the VLSI design efforts are mainly focused on low-power circuits with high-speed computation. In various DSP processors, Multiplier and Adder circuits are the main building blocks of the Arithmetic Unit. In such processors, certain parameters like power, area, delay-time, etc. have to be given due consideration for efficiency. The designers are thus forced to concentrate on addressing the constraints like high speed, small area, high throughput, and low power consumption [1-3]. As innovation downsizes to 32nm and the present Complementary Metal-Oxide semiconductor (CMOS) innovation has confronting as far as possible.

## Revised Manuscript Received on April 14, 2019.

**K.Sarath Chandra,** Research Scholar, Department of ECE, Koneru Lakshmaiah Education Foundation, Vaddeswaram, Guntur, AP, India, Assistant Professor, Department of ECE, VNRVJIET, Hyderabad, Telangana

**K Hari Kishore**, Professor, Department of ECE, Koneru Lakshmaiah Education Foundation, Vaddeswaram, Guntur, AP, India 522502

This issue is because of the expanded leekage control dispersal, the expanded short-channel impacts, extreme process varieties, high power thickness, etc. To beat this scaling limit, the specialists are probed different innovations. Among which FinFET innovation has been assessed as one of the promising substitution to MOSFET of CMOS innovation.

The power dissemination in CMOS incorporates dynamic and static segments. The power dissemination is because of leekage current in stand by mode. The dynamic power dissipation is mainly due to because of switching power which arises because of charging and discharging capacitance and another is because of short circuit power which arises because of non zero rise time and fall times.

Decrease of supply voltage diminishes control dispersal, this is on the grounds that the power dissemination has quadratic association with the supply voltage. Be that as it may, decreasing supply voltage corrupts the execution. With the end goal to fulfill the superior necessities, VTH must be scaled. Woefully, such scaling prompts significantly increment in spillage current, which turns into another real worry for low power and superior circuit plans [4]. Prior in micrometer innovations the dynamic power is the prevailing part of aggregate power yet in nanometre advances spillage control is the predominant segment. Beginning at 70nm semiconductor innovation, spillage power will contribute with 50 % to add up to circuit's capacity [5].

#### II. FINFET TECHNOLOGY

Two fold entryway FinFETs, can conquer the scaling deterrents [6] [7]. the front and back entryways might be made autonomous and one-sided to control the current and the gadget edge voltage The most essential element of FinFETs is that [8]. The capacity to control limit voltage varieties offers an adaptability to diminish reserve control dispersal. FinFET is viewed as promising innovation that can affect the prompt future because of its low spillage control utilization, superior.[6].

FinFETs ability to configure the back gates to provide greater speed and greater leakage control gives the scope for the designers to use FinFET to have low power delay product.

## III. MODES OF OPERATION

FinFET's can be worked in three methods of activity i.e. hamper, low power mode and autonomous door mode. The geometry of FinFET permit less spillage current in light of their solid power over the channel.

# **Electrical Characteristics of Double Gate FINFET Under Different Modes of Operation**

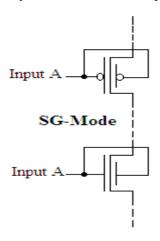

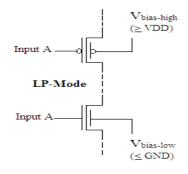

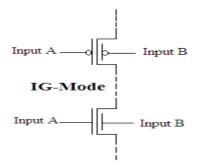

This transistor design is of shorted door (SG) and is delineated in Figure 1.(a). In the low-control (LP) working mode, exhibited in Figure 1.(b), use of turn around predisposition on the back door lessens spillage current incredibly (Ioff). Having a back-entryway inclination of -0.2V on a n-type FinFET diminishes Ioff by 85% of a tantamount SG FinFET [7]. A pivot tendency unfavorably impacts the on current (Ion) of the transistor. Molecule diminishes by about 60% in the LP mode when the pivot tendency is set to - 0.2V for a n-type transistor [7]. Littler turn around predispositions effectsly affect Ioff and Ion, yet to a lesser degree [7]. The back-door can be fixing to another info, prompting autonomous entryway (IG) working mode, imagined in Figure 1.(c). In any case, the FinFET's entryways might be made free (additionally alluded to as a MIGFET, or different autonomous door FET) to consider separate authority over the front-and back-doors [5]. The electrical properties are plotted for sc door and low power method of activity for forward and switch predisposition.

Fig. 1 (a) Shorted-gate (SG) mode FinFETs

Fig. 1 (b) Low-power (LP) mode FinFETs

Fig. 1 (c) Independent-gate (IG) mode FinFETs

Table. 1 FinFET Technology Model

| Parameter Value                |               |  |  |

|--------------------------------|---------------|--|--|

| Fin height (Hfin)              | 70 nm         |  |  |

| Fin thickness (TSI)            | 14 nm         |  |  |

| Oxide thickness (Tox)          | 1.1 nm        |  |  |

| N-Channel Surface Orientation  | <105>         |  |  |

| Length of gate (LG)            | 25 nm         |  |  |

| Source to gate /drain underlap |               |  |  |

| (LSD)                          | 10 nm         |  |  |

| Gate thickness (TG)            | 20 nm         |  |  |

|                                | 4.4 eV        |  |  |

| Cata work function (AC)        | (n-type)      |  |  |

| Gate work function (ΦG)        | 4.8 eV        |  |  |

|                                | (p-type)      |  |  |

|                                | 560 cm2/(V-s) |  |  |

| Mobility                       | (n-type)      |  |  |

|                                | 200 cm2/(V-s) |  |  |

|                                | (p-type)      |  |  |

| Doping of Fin body (N Body)    | 1014 cm-3     |  |  |

| Drain/ Source resistance (RSD) | 180 Ω-μm      |  |  |

| Voltage Supply (VDD)           | 1 V           |  |  |

| Source/drain doping (NDS)      | 1020 cm-3     |  |  |

#### IV. SIMULATION RESULTS

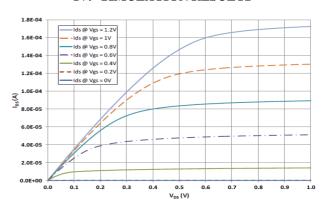

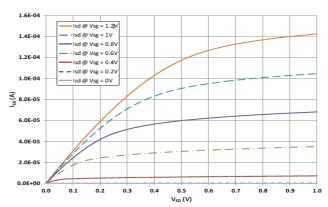

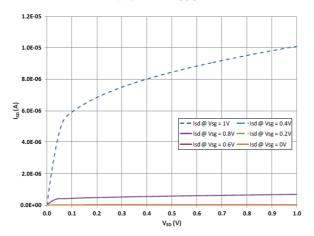

Fig. 1.1 n-type SG-mode

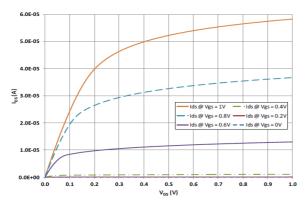

Fig. 1.2 p-type in SG-mode

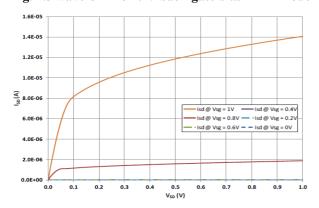

Fig. 1.3 waveform for 0 V back-gate bias in LP mode

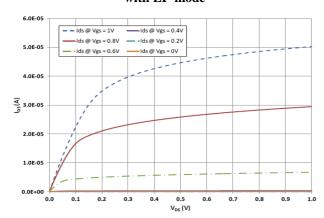

Fig. 1.4 waveform for VDD back-gate bias in p-type with LP-mode

Fig. 1.5 waveform for -0.4V back-gate bias in n-Type with LP-mode

Fig. 1.6 waveform for 1.4 back-gate bias in p-type with LP-mode

Table. 2 LP-mode FinFET Ion and Ioff currents for various back-gate bias voltage

| N-TYPE FinFET |                 |                       | P-TYPE FinFET |                 |                       |

|---------------|-----------------|-----------------------|---------------|-----------------|-----------------------|

| Back-<br>Gate | Current         |                       | Back-<br>Gate | Current         |                       |

| Bias(V)       | I <sub>on</sub> | I <sub>off</sub> (pA) | Bias          | I <sub>on</sub> | I <sub>off</sub> (pA) |

|               | (µA)            |                       | (V)           | (µA)            |                       |

| -0.4          | 41.6            | 1                     | 1.4           | 27.9            | 0.2                   |

| -0.3          | 45.3            | 2                     | 1.3           | 29.7            | 0.8                   |

| -0.2          | 49.3            | 15                    | 1.2           | 32.7            | 3                     |

| -0.1          | 53.2            | 65                    | 1.1           | 35.7            | 12                    |

| 0.0           | 57.2            | 360                   | 1.0           | 38.8            | 70                    |

| 0.1           | 61.3            | 2560                  | 0.9           | 42.0            | 490                   |

| 0.2           | 65.6            | 14600                 | 0.8           | 45.1            | 3600                  |

| 0.3           | 68.7            | 22400                 | 0.7           | 47              | 7900                  |

| 0.4           | 72.7            | 30300                 | 0.6           | 49.6            | 13570                 |

Table. 3 FinFET leakage current for LP configuration (pA)

| CONFIGURATION |           | Leakage Current (pA) |        |  |

|---------------|-----------|----------------------|--------|--|

| N -TYPE(V)    | P-TYPE(V) | N-TYPE               | P-TYPE |  |

| -0.2          | +1.2      | 15.6                 | 3.2    |  |

| 0             | $v_{dd}$  | 372                  | 75     |  |

#### V. CONCLUSION

We have observed that when we make forward bias on the back gate then on current increases lightly where as Ioff current increases exponentially. When we apply reverse bias to back gate there is slight linear increase in Ion where as the off current decreases exponentially giving a better Ion: Ioff ratio. Further it is investigated that in low power shorted gate configuration back gate biasing will reduce leakage currents. we also conclude that solitary balance ntype FinFET has around 5X more spillage current than a solitary balance p-type FinFET; explicitly 4.91X if in LP design with inclinations at - 0.2 V for n-type and 1.2 V (VDD+0.2V) for p-type, 4.96X if in LP setup with predispositions at 0 V for n-type and 1V VDD for p-type. FinFETs capacity to arrange the back gate to give more prominent speed and more prominent leakage control gives the scope for the designers to use FinFET to have low power delay product.

# REFERENCES

- J. D. Meindl, "Low power Microelectronics: Retrospect and Prospect," Proceedings of the IEEE, Vol.83, No.4, pp. 619-635, 1995.

- P. Chandrakasan, S. Sheng and R. W. Brodersen, "Low-Power CMOS Digital Design," IEEE Journal of Solid-State Circuits, Vol.27, No.4, pp. 473-484, 1992.

- P. Pant, V. De and A. Chstterjee, "Device-Circuit Optimization for Minimal Energy and Power Consumption in CMOS Random Logic Network," ACM/IEEE Design Automation Conf., pp. 403-408, 1997.

- Liqiong Wei, Kaushik Roy and Vivek K. De, "Low Voltage Low Power CMOS Design Techniques for Deep Submicron ICs," 13th International Conference on VLSI Design, pp.24 – 29, 2000.

# **Electrical Characteristics of Double Gate FINFET Under Different Modes of Operation**

- M. R. de Alba Rosano and A. D. Garcia-Garcia, "Measuring leakage power in nanometer CMOS 6T SRAM cells," in Proc. IEEE Int. Conf. Reconfigurable, Comput. FPGA's, 2006.

- "International Technology Roadmap for Semiconductors," [Online]. Available: www.itrs.net

- T.-J. King, "FinFETs for nanoscale CMOS digital integrated circuits," in Proc. Int. Conf. Computer-Aided Design, pp. 207-210, Nov. 2005.

- J.-P. Colinge, "The SOI MOSFET: From single gate to multigate," in FinFETs and Other Multi-Gate Transistors, 1st ed., J.-P. Colinge, Ed., New York, Springer, 2008, pp. 1-48.

- Yadlapati, A., Kakarla, H.K. An Advanced AXI Protocol Verification using Verilog HDL (2015) Wulfenia, 22 (4), pp. 307-314.

- Bindu Bhargavi, K., Hari Kishore, K. Low Power Bist on Memory Interface Logic (2015) International Journal of Applied Engineering Research, 10 (8), pp. 21079-21090.

- Charan, N.S., Kishore, K.H. Recognization of delay faults in cluster based FPGA using BIST (2016) Indian Journal of Science and Technology, 9 (28).

- Hari Kishore, K., Aswin Kumar, C.V.R.N., Vijay Srinivas, T., Govardhan, G.V., Pavan Kumar, C.N., Venkatesh, R.V. Design and analysis of high efficient UART on spartan-6 and virtex-7 devices (2015) International Journal of Applied Engineering Research, 10 (9), pp. 23043-23052.

- Kante, S., Kakarla, H.K., Yadlapati, A. Design and verification of AMBA AHB-lite protocol using Verilog HDL (2016) International Journal of Engineering and Technology, 8 (2), pp. 734-741.

- Bandlamoodi, S., Hari Kishore, K. An FPGA implementation of phaselocked loop (PLL) with self-healing VCO (2015) International Journal of Applied Engineering Research, 10 (14), pp. 34137-34139.

- Murali, A., Hari Kishore, K., Rama Krishna, C.P., Kumar, S., Trinadha Rao, A. Integrating the reconfigurable devices using slow-changing key technique to achieve high performance (2017) Proceedings - 7th IEEE International Advanced Computing Conference, IACC 2017, art. no. 7976849, pp. 530-534.

- A. Surendar, K. H. Kishore, M. Kavitha, A. Z. Ibatova, V. Samavatian "Effects of Thermo-Mechanical Fatigue and Low Cycle Fatigue Interaction on Performance of Solder Joints" IEEE Transactions on Device and Materials Reliability, P-ISSN: 1530-4388, E-ISSN: 1558-2574, Vol No: 18, Issue No: 4, Page No: 606-612, December-2018.

- 17. N Bala Dastagiri K Hari Kishore "A 14-bit 10kS/s Power Efficient 65nm SAR ADC for Cardiac Implantable Medical Devices" International Journal of Engineering and Technology (UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 34-39, March 2018.

- N Bala Dastagiri, Kakarla Hari Kishore "Reduction of Kickback Noise in Latched Comparators for Cardiac IMDs" Indian Journal of Science and Technology, ISSN No: 0974-6846, Vol No.9, Issue No.43, Page: 1-6, November 2016.

- N Bala Dastagiri, K Hari Kishore "Analysis of Low Power Low Kickback Noise in Dynamic Comparators in Pacemakers" Indian Journal of Science and Technology, ISSN No: 0974-6846, Vol No.9, Issue No.44, page: 1-4, November 2016.

- 20. Avinash Yadlapati, Hari Kishore Kakarla "Design and Verification of Asynchronous FIFO with Novel Architecture Using Verilog HDL" Journal of Engineering and Applied Sciences, ISSN No: 1816-949X, Vol No: 14, Issue No: 1, Page No: 159-163, January 2019.

- P Kiran Kumar, P Prasad Rao, Kakarla Hari Kishore, "Optimal Design of Reversible Parity Preserving New Full Adder / Full Subtractor", Proceedings of 2017 11th International Conference on Intelligent Systems and Control, ISCO 2017, pp. 368-373, , 25<sup>th</sup> and 26<sup>th</sup> February 2017.

- 22. A Murali, K Hari Kishore, C P Rama Krishna, S Kumar, A Trinadha Rao "Integrating the Reconfigurable Devices using Slow-changing Key Technique to achieve High Performance "Proceedings- 7<sup>th</sup> IEEE International Advance Computing Conference, IACC 2017, 7976849 ISSN: 2473-3571, pp.530-534, July 2017.

- 23. Nadhindla Bala Dastagiri, Kakarla Hari Kishore, Vinit Kumar Gunjan and Shaik Fahimuddin, "Design of a Low-Power Low-Kickback-Noise Latched Dynamic Comparator for Cardiac Implantable Medical Device Applications", Proceedings of 2nd International Conference on Micro-Electronics, Electromagnetic and Telecommunications, Lecture Notes in Electrical Engineering, ISSN No: 1876-1100, E-ISSN: 1876-1119, pp. 637-645, 29th March 2017.

- 24. G. Vijaya Padma, K. Hari Kishore and S. Jaya Sindura, "Controlling the Traffic Interactions with High Mobility and Constant Network Connectivity by Vanets", Proceedings of 2nd International Conference on Micro-Electronics, Electromagnetic and Telecommunications,

- Lecture Notes in Electrical Engineering (Publisher: Springer Nature Singapore Pte Ltd), ISSN No: 1876-1100, E-ISSN: 1876-1119, pp. 593-601, 29<sup>th</sup> March 2017.

- 25. A Murali, K Hari Kishore, L Srikanth, A Trinadha Rao and V Suresh, "Implementation of Reconfigurable Circuit with Watch-Points in the Hardware", Proceedings of 2nd International Conference on Micro-Electronics, Electromagnetic and Telecommunications, Lecture Notes in Electrical Engineering, ISSN No: 1876-1100, E-ISSN: 1876-1119, pp. 657-664, 29th March 2017.

- Meka Bharadwaj, Hari Kishore "Enhanced Launch-Off-Capture Testing Using BIST Designs" Journal of Engineering and Applied Sciences, ISSN No: 1816-949X, Vol No.12, Issue No.3, page: 636-643, April 2017