# Design of Efficient Single Precision Floating Point Multiplier using Urdhva Triyagbhyam Sutra of Vedic Mathematics

Sai Venkatramana Prasada G S, G Seshikala, Niranjana S

Abstract---: Multiplication of floating point(FP) numbers is greatly significant in many DSP applications. The performance of the DSP's is substantially decided by the speed of the multipliers used. This paper proposes the design and implementation of IEEE 754 standard single precision FP multiplier using Verilog, synthesized and simulated in Xilinx ISE10.1. Urdhva Triyagbhyam Sutra of Vedic mathematics is used for the unsigned mantissa calculation. The design implements floating point multiplication with sign bit and exponent calculations. The proposed design is achieved high speed with minimum delay of 3.997ns.

Index Terms: Floating point numbers, Single precision, IEEE 754, Urdhva Triyagbhyam Sutra, Vedic mathematics.

# I. INTRODUCTION

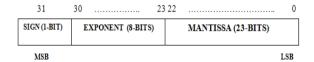

Multiplication of floating point binary numbers is the most important operation in DSP applications. IEEE 754 standard provides formats for the FP numbers. IEEE 754 standard format for single precision(32-bit) FP number consist of a Sign unit(1-bit), Exponent unit(8-bits) and Mantissa unit(8-bits) as shown in fig.1.

Fig.1: IEEE 754 Single Precision Format

MSB's of two 32-bit numbers are XORed to generate sign bit of the product. Exponent of the product is calculated by adding exponents of the inputs using Carry Look Ahead(CLA) adder and biasing to -127. Mantissa multiplication unit is designed using Urdhva Triyagbhyam Sutra of Vedic mathematics.

# A. Urdhva Triyagbhyam Sutra

The exact meaning of Urdhva Tiryabyham sutra is "Vertically and Crosswise". Urdhva Tiryabyham Sutra can be applied to all the cases of multiplication. In this method, the partial products & their sum is obtained in parallel. The steps involved in 2x2 multiplication[14] using Urdhva

# Revised Manuscript Received on April 12, 2019.

Sai Venkatramana Prasada G S, Assistant Professor, Dept. of E &C, Srinivas University, Mangaluru -574146 Research scholar, School of E&C, Reva University, Bangalore -560064, India. (E-mail: svprasad007@yahoo.co.in)

**Dr.G Seshikala,** Professor, School of E&C, Reva University, Bangalore -560064, India.

**Dr.Niranjana S,** Associate Professor-Senior Scale, MIT, MAHE, Manipal, Udupi -576104, India.

Tiryabyham Sutra are shown in fig.2. The same procedure can be extended for 3x3 multiplication[3] as shown in fig.3.

Fig.2. 2x2 Multiplication Using Urdhva Sutra

Fig.3. 3x3 Multiplication Using Urdhva Sutra

The 3x3 multiplier can be used for constructing higher order multipliers such as 6x6, 12x12 and 24x24 bit multiplication.

# II. PREVIOUS WORKS

Swapnil Suresh Mohite, Sanket Sanjay Nimbalar, Madhav Makarand Bhathande, Rashmi Rahul Kulkarni presented the design of 32-bit FP multiplier using Urdhva Triyagbhyam sutra[1] which reduces the processing delay. Code was written in VHDL using Xilinx ISE series. Overall performance of designed multiplier depends upon the performance of mantissa multiplier unit. Mantissa multiplier was designed using Urdhva Triyagbhyam sutra. 3x3 multiplier was used as basic multiplier. 8-bit CLA is used for adding two 8-bit exponent. Output of the adder was biased to -127 to generate the exponent of output floating point number. The proposed multiplier circuit takes 71.239ns to perform multiplication of two 32-bit floating

# DESIGN OF EFFICIENT SINGLE PRECISION FLOATING POINT MULTIPLIER USING URDHVA TRIYAGBHYAM SUTRA OF VEDIC MATHEMATICS

point binary numbers. This delay is significantly less than Booth multiplier. Aniruddha kanhe, Shishir Kumar Das, Ankit Kumar Singh described the design and implementation of IEEE 754, 32-bit FP multiplier[3] using vedic mathematics. The

Urdhva Triyagbhyam sutra was used for mantissa multiplication. Multiplication was achieved by adding the biased 8-bit exponent, multiplying the normalized 24-bit mantissa and resultant was converted in excess 127 bit format. The exponent calculation unit was implemented using 8-bit RCA. Sign bit was calculated by XORing the MSB's of the inputs. The multiplier was designed in Verilog HDL and simulated using Modelsim simulator. This design was synthesized using Xilinx ISE12.1 tool targeted on the Xilinx Vertex5. The design utilizes lesser number of LUT's, thereby reduces the power consumption.

Soumya Havaldar, K S Gurumurthy[4] proposed the design of multiplier for floating point numbers using vedic mathematics. This design also manages overflow, underflow and rounding. Design was coded in VHDL, simulated and synthesized using ISE14.6 tool targeting the Xilinx VertexVI FPGA. This work concludes that; the proposed design occupies less space and high operating speed due to vertical and crosswise calculation using Urdhva Triyagbhyam sutra.

Pooja Hatwalne, Ameya Deshmukh, Tanmay Paliwal, Krupal Lambat proposed a design and implementation of single precision FP multiplier using VHDL[5]. 24-bit multiplier using Urdhva Triyagbhyam sutra of vedic mathematics was designed for mantissa calculation. 8-bit CLA adder was used for exponent calculation. The design was synthesized and simulated in Xilinx ISE14.7 targeted on Spartan3 device. The proposed floating point multiplier showed optimized and better timing performance with total delay of 36.19ns.

# III. SILULATION RESULTS

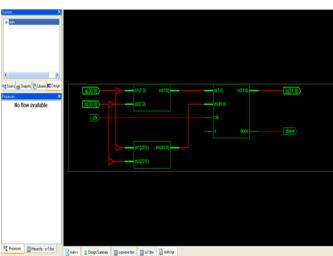

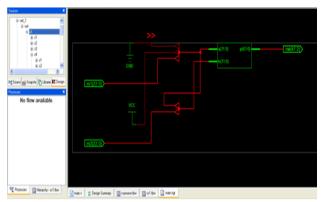

32-bit floating point multiplier design is implemented in VHDL and simulated using Xilinx ISE10.1. The unsigned mantissa multiplication is achieved by using Urdhva Triyagbhyam Sutra of Vedic mathematics. Fig.4-6 shows the RTL schematics of 32-bit floating point multiplier, mantissa unit and exponent calculation unit respectively.

Fig.4: Schematic Of 32-Bit Floating Point Multiplier

Fig.5: Schematic Of Mantissa Calculation

Fig.6: Schematic Of Exponent Calculation

**Table 1: Performance Analysis**

| Parameters        | Proposed Urdhva 32X32 |  |  |

|-------------------|-----------------------|--|--|

| NO. SLICES        | 298                   |  |  |

| NO. 4 IP LUT      | 579                   |  |  |

| NO.OF BONDED IOBs | 96                    |  |  |

| COMBINATIONAL     | 3.997ns               |  |  |

| DELAY             |                       |  |  |

Table 1 show the device utilization and combinational delay of the proposed design. Table 2 show the comparison of the proposed design with the designs of the literatures. The proposed design exhibits lesser device utilization and delay.

**Table 2: Comparison of Performance Parameters**

| Paper    | Number<br>of Slices | LUT's | Bonded<br>IOB's | Time<br>delay(ns) |

|----------|---------------------|-------|-----------------|-------------------|

| [1]      | 911                 | 1580  | 96              | 71.293            |

| [3]      | -                   | 966   | 99              | 5.246             |

| [4]      | -                   | 705   | 96              | 21.823            |

| [6]      | -                   | 672   | 96              | 4.94              |

| [9]      | 1389                | 1545  | 129             | 13.141            |

| [10]     | 2041                | 3317  | 206             | 89.374            |

| [11]     | -                   | 1032  | 99              | 5.246             |

| [12]     | 999                 | 1819  | 1               | 14.17             |

| Proposed | 298                 | 579   | 96              | 3.997             |

| design   |                     |       |                 |                   |

# IV. CONCLUSION

The single precision FP multiplier using Urdhva Triyagbhyam Sutra is designed in VHDL, simulated using Xilinx ISE10.1 and parameters such as number of slices, 4 input LUT's and delay were analyzed and compared with the literatures. The proposed design utilizes lesser number of slices and LUT's thereby reduces the hardware requirement. High speed is also achieved by the use of Urdhva Triyagbhyam Sutra and CLA adder. This proposed work can be extended for the design of double precision(64-bit) FP multiplier using Vedic mathematics.

#### REFERENCES

- Swapnil Suresh Mohite, Sanket Sanjay Nimbalar, Madhav Makarand Bhathande, Rashmi Rahul Kulkarni, "32 bit Floating Point Vedic Multiplier", IOSR Journal of VLSI and Signal Processing(IOSR-JVSP), Volume 6, Issue 2, Ver. I, pp 16-20, Mar-Apr.2016.

- Sneha khobragade, Mayur Dhait, "Design of High Speed Single Precision Floating Point Multiplier Using Vedic Mathematics", International Journal of Innovative Research in Computer and Communication Engineering, Vol.3, Issue 7, pp 6875-6882, July 2015.

- Aniruddha kanhe, Shishir Kumar Das, Ankit Kumar Singh, "Design and Implementation of Floating Point Multiplier based on Vedic Multiplication Technique", IEEE International Conference on Communication, Information & Computing Technology(ICCICT), Mumbai, pp 1-4, Oct. 19-20,2012.

- Soumya Havaldar, K S Gurumurthy, "Design of Vedic IEEE 754 Floating Point Multiplier", IEEE International Conference On Recent Trends In Electronics Information Communication Technology, pp 1131-1135, May 20-21.2016.

- Pooja Hatwalne, Ameya Deshmukh, Tanmay Paliwal, Krupal Lambat, "Design and Implementation of Single Precision Floating Point Multiplier using VHDL on SPARTAN 3", International Journal of Latest Trends in Engineering and Technology, Vol.8, Issue 3, pp 263-269, May 2017.

- Sushma S Mahakalkar, Sanjay L Haridas, "Design of High Performance IEEE 754 Floating Point Multiplier Using Vedic Mathematics", IEEE International Conference on Computational Intelligence and Communication Networks, pp 985-988, 2014.

- Pratheeksha Rai, Shailendra Kumar, Prof. S H Saeed, "Design of Floating Point Multiplier Using Vedic Aphorisms", International Journal of Engineering Trends and Technology(IJETT), Vol.11, Number 3, pp 123-126, May 2014.

- Irine Padma B T, Suchitra K, "Pipelined Floating Point Multiplier Based on Vedic Multiplication Technique", International Journal of Innovative Research in Science, Engineering and Technology, Vol.3, Issue 5, pp 130-137, July 2014.

- Arish S, R K Sharma, "An Efficient Floating point Multiplier Design for High Speed Applications Using Karatsuba Algorithm and Urdhva Triyagbhyam algorithm, IEEExplore, pp 303-308, July 2015.

K Veeraraju, B Sujatha, "An Implementation of Single

- K Veeraraju, B Sujatha, "An Implementation of Single Precision Floating Point Vedic Multiplier Using Verilog", International Journal of Engineering Technology, Management and Applied Sciences, Vol.2, Issue 7, pp 128-134, December 2014.

- 11. I V Vaibhav, K V Saicharan, B Sravanthi, D Srinivasulu, "VHDL Implementation of Floating Point Multiplier Using Vedic Mathematics", International Conference on

- Electrical, Electronics and Communications, pp 110-115, June 2014

- 12. Kusuma Keerti, "Design of High Performance Single Precision Floating Point Multiplier", ITSI Transaction on Electrical and Electronics Engineering(ITSI-TEEE), Vol.2, Issue 1, pp 36-40, 2014.

- 13. Ajay A Raut, Dr. Pravin. K. Dahole, "Floating Point Multiplier for DSP Using Vertically and Crosswise Algorithm", IETE 46<sup>th</sup> Mid Term Symposium "Impact of Technology on Sill Development", International Journal of Electronics, Communication & Soft Computing Science and Engineering, pp 267-271, 2015.

- Shweta Agrawal , Vijay Kumar Magraiya, Abhay Khedkar "Implementation of Vedic Multiplier on Circuit Level", International Journal of Advanced Engineering Research and Science (IJAERS), Volume 1- No.6, pp 53-55, 2014.