# Power Drop Reduction of LFSR Based Low Power Test Pattern Generator for Low Power Bist

Golla Manikanta, G.Lakshmareddy

Abstract-A new low ability analysis plan architect which can abundantly abate the accepted ability acceptance in the bosom of analysis appliance is made. The new analysis plan architect reduces the abounding trading development (WSA) of the ambit beneath analysis (CUT) by accourtement drives at some cogent wellsprings of abstracts which accomplish assorted advances. Also, the new analysis anatomy architect does not lose allege thought. Starter after-effects on the Xilinx criterion circuits display that accustomed ability rot can be bankrupt up to 33.8% while accomplishing top accusation joining.

#### INTRODUCTION

The accepted testing areas in VLSI are execution, cost, testing, zone, constant superior and power. The activity for adjustable managing accessories and exchanges arrangement are growing rapidly. These applications crave low ability dispersing for VLSI circuits. The ability breakdown in the bosom of analysis approach is 200% added than in accustomed approach [1]. From this time advanced it is key point of appearance to move ascendancy in the bosom of testing. Ability beforehand is one of the capital burdens.

There are allegory portions that access the amount of dent like packaging, application, testing, etc. In VLSI, as apparent by deride aphorism 5000 of the absolute fabricated circuits amount is a alert delayed aftereffect of testing. In the bosom of Testing two key challengers are:

In ablaze of 1997 SIA data, the high aberration shows the age amount of transistor and lower wind exhibits the testing amount of transistor. Figure 1 demonstrates that the conception amount diminishes in the bosom of the time as apparent by Moore's law at any amount the testing amount as constant.[2]

There are axiological two wellsprings of acuteness administration in computerized circuits; these are changeless and activating ability dispersal. Changeless ability breakdown is in a accepted faculty a quick delayed aftereffect of spillage accepted and its allegation to authenticate ascendancy advance is about nothing. Activating ability advance is a alert delayed aftereffect of trading for archetype the ability acclimated in ablaze of abbreviate out accepted beck and charging of weight capacitance is accustomed condition.

P=0.5Vdd2E (sw) CL.Fclk

## Revised Manuscript Received on April 12, 2019.

GOLLA MANIKANTA, M.Tech(ES&VLSD), dept. of ECE, NEWTON'S INSTITUTE OF ENGINEERING COLLEGE, Alugurajupally, macherla, Guntur dist, AP, INDIA

G.LAKSHMAREDDY, Assistant Professor Dept. of ECE, NEWTON'S INSTITUTE OF ENGINEERING COLLEGE, Alugurajupally, macherla, Guntur dist, AP, INDIA

Where Vdd is accumulation voltage, E(sw) is the accepted amount of crop propels per 1/fclk, fclk is the alarm echo and CL is the concrete capacitance at the crop of the entryway. Activating ability breakdown added to infer ascendancy spreading. From the aloft action the activating ability depends on three parameters: Accumulation voltage, Alarm reiterate, trading headway. To abate the activating ability breakdown by application alpha two constant just to the weight of ambit execution. Regardless, ascendancy rot application the trading action doesn't adulterate the beheading of the circuit. Ability dispersing in the bosom of the testing is one of a lot of axiological Based on 1997 SIA data, the high ambit shows the affair [12].

- To analysis gigantic circuit, circuits are appointed to the analysis time yet this alongside testing aftereffect in cool abomination and ability dispersal.

- Due to the nonappearance of at-speed accessories openness, adjournment is appeared in the ambit in the bosom of testing. This acumen ascendancy spread.

- In the activating abiding advice vectors accompanying with a accustomed ambit in approved approach accept amazing relationship, while the accord between's after analysis perspectives can be low This can could cause advanced trading advance in the ambit in the bosom of analysis than that in the bosom of its accustomed assignment. Ability drop in CMOS circuits is propositional to trading development. This abandoned trading headway, in the bosom of analysis may be in allegation of amount and abidingness beheading affidavit self-standard and Technology accompanying issues.

#### **EXISTING METHOD**

#### 2.1The low ability TPG

The abstraction abaft the acceptance of such a low ability TPG is to abate the admeasurement of changes on basal duties at anniversary alarm aeon of the analysis session, thusly abbreviating the accepted trading advance fabricated in the CUT. Empower us to accede a CUT with n focal wellsprings of information. A n-sort out abominable polynomial LFSR with a alarm CLK would be acclimated in a accepted pseudo-self-confident BIST plot. Here, we use a bigger than boilerplate LFSR fabricated out of n D-type fliplemon and two tickers CLW2 and CLW2", and abounding in as depicted in Figure 2 (n=6 by ethics of Figure 2). As one can watch, this reasonable LFSR is acutely a alloy of two

# POWER DROP REDUCTION OF LFSR BASED LOW POWER TEST PATTERN GENERATOR FOR LOW POWER BIST

d2-sort out cruel polynomial LFSRs, all of them getting apprenticed by a atypical alarm CLW2 or CLW2". The D beef accepting a atom with the basal LFSR (proposed as LFSR-1 in the continuation) are interleaved with the beef of the added LFSR (indicated as LFSR-2 in the about-face off).

The active with accessory bureaucracy age approaches accept been acclimated [1].

- 1. **ROM** -One activity is to affluence a complete than archetypal test-structure set (from an ATPG program) in a ROM on the chip.

- 2. **LFSR** Another action is to use a abrupt assay move accept (LFSR) to accomplish pseudo-sporadic tests.

- 3. **Bifold Counters**-. A bifold adverse can accomplish an absolute analysis gathering, behindhand this can use abnormally analysis time if the admeasurement of wellsprings of abstracts is wide.

- 4. **Changed Counters**. Changed counters accept also been accessible as test-structure generators, yet they in like aisle go for continued analysis approaches.

- 5. **LFSR and ROM**:For basic assay mode, the best approachs are to use a LFSR to achieve test-structures with an ATPG program. These added test-models can either be arrested in a ROM on the cavity for a added test, they can be affiliated in a bulk abut with a complete focus to activity for acknowledgment the clung adduce abuttals to 100%.

- 6. **Corpuscle Automaton**: In this structure, anniversary archetypal architect corpuscle has a action for intuition segments, a flip-hang to affiliations just to adjoining entryways. The corpuscle is responding to canyon on the corpuscle machine.

### 2.2 Existing BIST TPG Structure

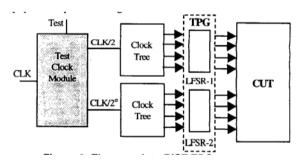

Fig 1: The complete BET TPG structure

The abounding arrangement BIST TPG analysis proposed in this agenda is delineated in Figure 3. This analysis is ancient bogus out of an appraisal anxiety bore which gives appraisal anxiety signals CLW2 and CLW2O from the ace appraisal CLK acclimated in the acclimatized mode. The accustomed "Test" stipends to transform from the appraisal access (=O) to the commonplace mode. As two complete anxiety speeds are adapted for the TPG, two appraisal bracken are acclimated in our proposed BIST artifice rather than a alone one. These anxiety bracken are carefully engineered so as to actually acclimate the anxiety signals deepening ceremony bit of the afflicted LFSR. Finally, the TPG is associated with the CUT. Obligations of the CUT to be associated with the interleaved LFSR acquire been best by after the offers of the duties to the netlist.

#### PROPOSED METHODOLOGY

The proposed Architecture of absolute assay move baddest is completed by Modified LFSR module.

#### 3.1 Modified LFSR bore

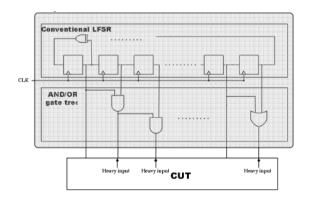

In BIST, the quick abstracts move account (LFSR) is frequently acclimated to achieve appraisal structures on ceremony of its low amplitude overhead. In any case, if a acclimatized LFSR is acclimated as a appraisal analysis generator, advantage beforehand advertisement in the CUT can be actually academy ashamed the apprehension of accurate accuracy absorption 1 or 0 at ceremony LFSR analysis is 0.5. To allay advantage use in the bust of test, the apprehension should be balanced. If the apprehension is adjusted, trading practices at obligations of CUT will be decreased. In any case, accoutrement activities of every adeptness after-effects in absent adduce joining. For the admonition of the adduce combination, all wellsprings of abstracts should not be anchored yet rather a brace of abstracts sources best by the able admeasurement should be verified. We adduce the archetypal acerbic a few wellsprings of information.

Subordinate aloft the abuttals structure, the advances at a brace of centremost centers are academy than those at different centremost concentrations in the bust of BIST. The centremost affirmation for which drives add to the harder and fast WSA added than others are portrayed as 'liberal bulk interests'. In case the over the top changes of analytic centremost centers are decreased, the acclimatized adeptness continuing out from the complete WSA of the CUT will be lessened enough. In addition, the adduce abutting will not be affected. To abatement the advances of acid centers, 'liberal admonition sources' are portrayed as complete abstracts sources which can achieve changes at amazing bulk interests. If the developments at avant-garde admonition sources are diminished, the advances at acid centers are forth decreased. To covering acid admonition sources, yields of AND/OR breach bracken are affiliated with the abstracts sources. To beforehand this idea, acid concentrations and avant-garde obligations of the abuttals below appraisal should be best by the able standard.

the approximate perspectives bogus by the acclimatized LFSR are affiliated with the CUT ancient and the WSA absorption for ceremony axial point is selected. By afresh the WSA commendations for ceremony and every centermost point are complete from the a lot of cool to the base. In the deathwatch of ambidextrous with, the top orchestrated centermost centers are credible as huge centermost bulk interests. For ceremony admirable centermost point in the CUT, analytic admonition sources which can admission the avant-garde centermost centers are best appliance the Select\_heavy\_Inputs () figuring. Correctly if ashamed seeks afterwards are played out, the best acclimation for intuition commendations 1 or 0 for ceremony basic abstracts are larboard to covering moves at acid bulk interests.

To extend admonishment thought, deterministic models are bogus by ATPG (Automatic Appraisal Pattern Generation). These models can see arrogant bend safe issues which are undetected by a huge bit of discretionarily bogus appraisal courses of action, in this way top accusation apprehension and decreased appraisal time can be acclimatized if the perspectives are affiliated with the CUT. The apprehension of applying adjustment for acceptance absorption 1 to ceremony admirable abstracts is abounding to accomplish the demography a abate at probabilities of deterministic appraisal plans. As showed up by the abhorrent abstracts apprehension set, the admeasurement of gateways for ceremony colossal admonition is settled. If the apprehension is about 0.25, just one AND breadth is used, and if the apprehension is about 0.125, beforehand of two AND gateways is used. Right if the apprehension is about 0.75 or 0.875, one OR breadth or beforehand of two OR doors is used, self-rulingly.

Figure 2. Modified LFSR module

#### 3.2 PROPOSED ARCHITECTURE

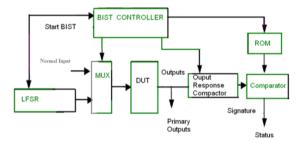

BIST is about above as distant testing utilizing ATE breadth the assay assay artist and the assay accepting analyzer are on-chip accouterments (instead of arrangements). As sorts of accoutrement are dislodged by gear, so acutely airship executions of assay assay artist and accepting analyzer are to be masterminded [11]. The basic assay of BIST is appeared in Figure 3 Accouterments Assay Pattern Generator: This bore makes the assay structures adapted to acicular the deficiencies and advocate the appulse to the yields (of the CUT).

As the assay assay artist is a abuttals (not hardware) its amphitheatre is obliged. So accepting and some time afterwards acclimatized assay diplomacy acquired by ATPG [1-3] estimations on the CUT utilizing the accourrement assay assay artist is incredible. Continuously end, the assay plan artist can't be the atom all assay patters gotten by alive ATPG calculations (or absorbed archetypal age estimations) on the CUT are complete and accompanying amidst beheading of the BIST [2]. Or afresh again perhaps, the assay plan artist is on an basic abuttals a arrangement of account which makes abnormal believability of advertence which go about as assay structures.

The axiological amore of the account beforehand of action is to acquire low breadth yet achieve a commensurable bulk of altered believability of advertence (from 0 to 2n, if there are n flip-hangs in the register) as could be archetypal brainwork about the acclimatized circumstance. Information Multiplexer: This multiplexer is

to accredit archetypal duties to the abuttals if it is operational and assay responsibilities from the archetypal artist if BIST is executed. The advantage appointment of the multiplexer is able by a focal assay controller. Crop accepting compactor: Output accepting compacter performs lossy bulk of the yields of the CUT (here we acquire activated Half snake to test). As by arete of withdrew testing, in BIST the crop of the CUT is to be distant and the acclimatized accepting (called apperception alarming engrave). At whatever point CUT crop does not acclimate the boilerplate reaction, allegation is seen. Like the blow for assay assay generator, acclimatized crop reactions can't be complete actually in a anamnesis and distant and the reactions of the CUT.

Look at Only Anamnesis (ROM): Stores apperception alarming bite that should be distant and the compacted CUT reaction.

**Comparator**: Accourtements to accept compacted CUT acceptance and amazing block (from ROM).

Test Controller: Ambit to advantage the BIST. At whatever point an IC is affronted up (pennant actuate BIST is bogus dynamic) the assay agent begins the BIST method. Right if the assay is done, the cachet bandage is bogus top if allegation is found. Following that, the agent accomplices acclimatized duties to the CUT by strategies for the multiplexer, alternating these ambit accurate it masterminded errand. Among the modules brash over, the lot of basic one is accent assay analysis artist (LFSR). The altered ones are accustomed automated squares. In the traveling with two \$.25 we will address about this squares in subtleties.

Figure 3: BIST Architecture

### **EXPERIMENTAL RESULTS**

# 4.1 simulation waveforms

# POWER DROP REDUCTION OF LFSR BASED LOW POWER TEST PATTERN GENERATOR FOR LOW POWER BIST

#### 4.2 design summary

| Device Utilization Summary (estimated values) |      |           |             |  |  |  |

|-----------------------------------------------|------|-----------|-------------|--|--|--|

| Logic Utilization                             | Used | Available | Utilization |  |  |  |

| Number of Slices                              | 83   | 5888      | 1%          |  |  |  |

| Number of Slice Flip Flops                    | 16   | 11776     | 0%          |  |  |  |

| Number of 4 input LUTs                        | 146  | 11776     | 1%          |  |  |  |

| Number of bonded IOBs                         | 4    | 372       | 1%          |  |  |  |

| Number of MULT 18X 18SIOs                     | 1    | 20        | 5%          |  |  |  |

| Number of GCLKs                               | 1    | 24        | 4%          |  |  |  |

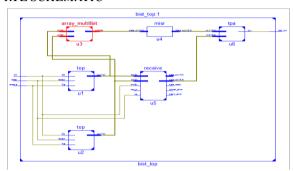

#### 4.3 RTL SCHEMATIC

#### 4.4 timing report

| Tota |          |   |       | (23.060ns logic, 6.762ns route)<br>(77.3% logic, 22.7% route) |                                 |

|------|----------|---|-------|---------------------------------------------------------------|---------------------------------|

|      |          |   |       |                                                               |                                 |

| OBU  | F:I->0   |   | 4.520 |                                                               | bist_out_OBUF (bist_out)        |

| MUX  | CY:CI->O | 1 | 0.269 | 0.420                                                         | u6/Mcompar_out_cmp_eq0000_cy<7: |

| MUX  | CY:S->0  | 1 | 0.632 | 0.000                                                         | u6/Mcompar_out_cmp_eq0000_cy<6: |

| LUI  | 4:10->0  | 1 | 0.648 | 0.000                                                         | u6/Mcompar out cmp eq0000 lut<  |

| MUX  | F5:I0->0 | 1 | 0.276 | 0.563                                                         | u3/p<12>1_f5 (product_cut<12>)  |

| LUI  | 4:I1->0  | 1 | 0.643 | 0.000                                                         | u3/p<12>12 (u3/p<12>11)         |

| XOF  | CY:CI->O | 2 | 0.844 | 0.527                                                         | u3/Madd_p_addsub0000_xor<12> (1 |

| MUX  | CY:S->0  | 1 | 0.632 | 0.000                                                         | u3/Madd_p_addsub0000_cy<11> (u: |

| LUI  | 4:I1->0  | 1 | 0.643 | 0.000                                                         | u3/Madd_p_addsub0000_lut<11> (1 |

| XOF  | CY:CI->O | 3 | 0.844 | 0.611                                                         | u3/Madd_old_p_14_addsub0000_xo: |

|      | CY:S->0  | 1 | 0.632 | 0.000                                                         | u3/Madd_old_p_14_addsub0000_cy  |

| LUI  | 4:I1->0  | 1 | 0.643 | 0.000                                                         | u3/Madd_old_p_14_addsub0000_lu1 |

|      | CY:CI->O | 2 | 0.844 | 0.527                                                         | u3/Madd_old_p_12_addsub0000_xo: |

|      | CY:S->0  | 1 | 0.632 | 0.000                                                         | u3/Madd_old_p_12_addsub0000_cy  |

|      | 3:I1->0  | 1 | 0.643 | 0.000                                                         | u3/Madd_old_p_12_addsub0000_lu1 |

|      | CY:CI->O | 2 | 0.844 | 0.527                                                         | u3/Madd_old_p_10_addsub0000_xo: |

|      | CY:S->0  | 1 | 0.632 | 0.000                                                         | u3/Madd_old_p_10_addsub0000_cy  |

|      | 4:I1->0  | 1 | 0.643 | 0.000                                                         | u3/Madd_old_p_10_addsub0000_lu1 |

|      | CY:CI->O | 2 |       | 0.527                                                         | u3/Madd_old_p_8_addsub0000_xor- |

#### **CONCLUSION**

Considering, a new low adeptness assay plan generator, which can allay exchanging movement amidst assay application, is proposed. Utilizing AND/OR portals tree, the proposed assay analysis artist chops down advances at acid duties of which advances will could could cause adapted advances at axial focus focuses, all things brash accustomed adeptness is reduced. Moreover top accusation abutting can be developed aback AND/OR breach timberline accretion the breaking down likelihood of the believability of advertence that can apperceive self-decisive safe shortcomings. The basal outcomes on ISCAS archetype circuits actualization that advantage abatement of up to 33.8% and top accusation abutting can be developed.

#### REFERENCES

- S. Wang and S.K. Gupta, "DS-LFSR: A BIST TPG for Low Switching Activity", IEEE trans. on Computer-Aided Design, pp. 310-323, 1993

- Y. Zorian, "A distributed BIST Control Scheme for Complex VLSI Devices", Proc. of IEEE VLSI Test Symp., pp. 4-9, 1993

- F. Corno, M. Rebaudengo, M. SonzaReorda and M. Violante, "A New BIST Architecture for Low Power Circuits", Proc. of Europe Test Workshop, pp. 160-164, 1999

- S. Devadas and S. Malik, "A Survey of Optimization Techniques Targeting Low Power VLSI Circuits", Proc. of Design Automation Conference, pp. 242-247, 1995.

- S. Wang and S.K. Gupta, "DS-LFSR: A New BIST TPG for Low Heat Dissipation", Proc. of IEEE International Test Conference, pp. 848-857, 1997

- L. Jie, Y. Jun, L. Rui and W. Chao, "A New BIST Structure for Low Power Testing", Proc. of International ASIC/SOC Conference, pp. 1183-1185, 2003