# Analysis of Five Level Cascaded H- Bridge Multilevel Inverter using PV Systems

K. Usha, Sathyabama V, Sathya Preetha R, Supriya S, Tarrani S

Abstract: The construction of a Cascaded H-bridge multilevel inverter is done by connecting a set of single full bridge inverter in series. An attempt is made to perform a detailed analysis on five-level Cascaded H-bridge Multilevel Inverter (CHMLI)utilizing three modulation techniques namely Equal Phaseshift method, Phase opposition disposition method, Alternate Phase Opposition disposition method. The Total Harmonic Distortion (THD) % and circuits complexity of the three PWM techniques were compared using MATLAB/SIMULINK software.

Index Terms: Multilevel Inverter, Pulse Width Modulation, Equal Phaseshift, Phase disposition, Phase opposition Disposition, Alternate Phase Opposition Disposition, Total Harmonic Distortion, Photovoltaic systems.

#### I. INTRODUCTION

Photovoltaic system is a mechanism to produce electric power from solar energy by using a solar cell. The concept of multilevel inverters improved the power quality, lowered the switching losses, gave better electromagnetic compatibility provided elevated voltage capability[1]. These advantages made the multilevel inverters to become popular. Multilevel inverters give a staircase or stepped sinusoidal waveform as its output. There are three topologies in multilevel inverters such as Diode clamped multilevel inverter, Flying capacitor multilevel inverter, Cascaded H-bridge multilevel inverter. The Neutral Point clamped multilevel inverter (m-level) requires (m-1) capacitors, 2(m-1) switching devices and (m-1)(m-1) clamping diodes for its construction. The levels of the output voltage depends on The flying capacitors multilevel inverter uses capacitors instead of using clamping diodes. It does not use extra diodes and the voltage output is obtained by combining capacitors.When more than three levels employed, clamping diodes are subjected to high voltage stresses.It requires additional storage capacitors when the number of levels increase. Among the three above mentioned topologies cascaded multilevel makes use of lesser number of components to give same number of voltage levels.

### Revised Manuscript Received on May 10, 2019.

K.Usha, Associate Professor, Department of Electrical and Electronics

Engineering, SSN College of Engineering, Anna University, Chennai, India.

Sathyabama V, UG Scholar, Department of Electrical and Electronics

Engineering, SSN College of Engineering, Anna University, Chennai, India.

Sathya Preetha R, UG Scholar, Department of Electrical and Electronics

Engineering, SSN College of Engineering, Anna University, Chennai, India.

Supriya S, UG Scholar, Department of Electrical and Electronics

Engineering, SSN College of Engineering, Anna University, Chennai, India.

Tarrani S, UG Scholar, Department of Electrical and Electronics

Engineering, SSN College of Engineering, Anna University, Chennai, India.

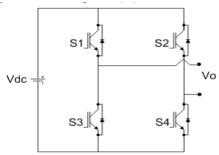

#### II. CASCADED MULTILEVEL INVERTER

In CHMLI each bridge has solar cells or batteries as separate dc source. They generate the almost sinusoidal waveform voltage [2]. This CHMLI can produce N level voltages (i.e for five level H-bridge inverter can generate five different voltage outputs +2Vdc, +vdc, 0 ,-2Vdc and -vdc). So output voltage the sum of all the individual inverter outputs gives the overall output voltage of an N-level H-bridge MLI.

Fig1.Cascaded Multilevel Inverter

Renewable energy sources make use of these type of separate dc sources. If the two back to back converters fail to switch synchronously, short circuit can be expected as connecting them between two converters in that manner is not possible.

The switches in cascaded MLI are triggered using different PWM techniques such as Equal Phaseshift (EP) method, Phase opposition disposition (POD), Alternate Phase opposition disposition (APOD).

# III. VARIOUS MULTICARRIER PWM TECHNIQUES

#### A. Equal Phase Shifted Method

For equal phase method the triggering pulses given to the individual eight switches in the MLI is given by PWM generators in which it is designed that at which time the switches has to be on and for how much duty cycle it has to be on to produce the required stepped output waveform and it is designed with of the help of switching angle.

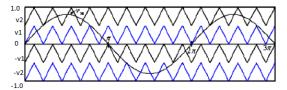

# **B.** Phase Disposition

This technique uses (n-1) carriers. In here all are in phase with one another in order to get the desired "n" level waveforms. The harmonics are located at the carrier frequency( $f_{\rm c}$ ).It does not appear in the lone voltage since it is a co-phase component.

# Analysis of Five Level Cascaded H- Bridge Multilevel Inverter using PV Systems

Carrier frequencies are found as sidebands for the other surrounded harmonic components. If the reference waveform is greater than both carrier waveform then +Vdc/2 is obtained. In case the reference is greater than the lower carrier waveform but less than the upper carrier waveform then it is found to be switching to 0. If the reference is less than both carrier waveforms then -Vdc/2 value is attained. In Two triangles namely upper and lower triangles are found to be present in the PWM scheme. The upper one ranges from 1 to 0 and the lower one ranges from 0 to -1. The pulse obtained by PD method is shown in the figure 2[3]. Similarly for a N-level inverter, (N-1) triangles are present with 2/(N-1) peak to peak value

Fig 2.Pulse width waveform for PD method

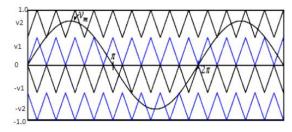

# C. Phase Opposition Disposition

This technique uses (n-1) carriers where those carriers that are above the reference are found to be in phase with one another and those that are below the reference are displaced by 180 degrees with respect to those above the reference. For both the phase and line voltage waveforms the harmonics are found to be around the carrier frequency(f<sub>c</sub>). If the reference waveform is greater than both the carrier waveforms, then +Vdc/2 is obtained . The waveform for POD method in figure 3[3]. If the reference waveform is greater than the lower carrier waveform or is less than the upper carrier waveform 0 voltage is obtained. Vdc/2 is obtained if the reference waveform is less than both carrier waveforms.

Fig 3. Pulse width waveform for POD method

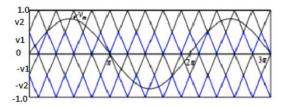

# D. Alternate Phase Disposition and Opposition

In this technique (n-1) carriers are 180 degrees alternately in order to get a "n" level waveform. When the reference is greater than all other carrier waveforms then +Vdc/2 is the voltage level. If the reference is less than the uppermost carrier waveforms and greater than all other carrier waveforms then +Vdc/4 is the obtained voltage level. When the reference is less than the two uppermost carrier waveforms and greater than two lowermost carriers then 0 level is attained. If the reference is found to greater than the lowermost carrier waveforms and lesser than all the other carrier waveforms then -Vdc/4 is obtained. The pulse given to the switches can be seen in figure 4[3].

Fig 4. Pulse width waveform for APOD method

#### IV. SIMULATION RESULTS

#### A. Equal Phase Method

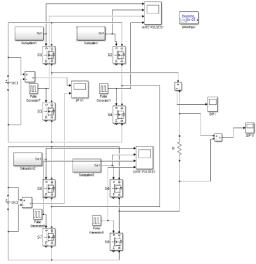

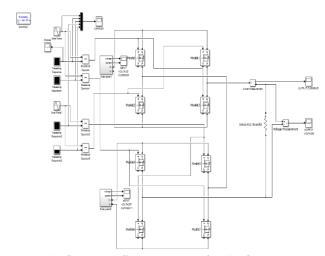

The simulation circuit for a single phase H-bridge MLI is shown in figure 5. The pulse to the switches are given according to the EP technique. The output waveform is seen by connecting a scope.

Fig 5. Cascaded five MLI for Equal phase method

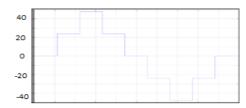

For equal phase method the triggering pulses for the individual eight switches in the MLI is given by PWM generator in which it is designed that at which time the switches has to be on and for how much duty cycle it has to be on to produce the required stepped output waveform and it is designed with of the help of switching angle. Figure 6 shows the output waveform of five level H-Bridge MLI using EP method.

Fig 6.Voltage output for five level H-bridge MLI using EP method

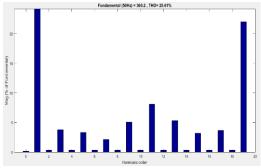

The THD analysis is done using FFT analysis in MATLAB .The THD obtained for EP method is 39.54% is shown in the figure 7.

Fig 7.THD analysis of Equal Phase method

#### **B.** Phase Opposition Disposition Method

Figure 8 depicts the single phase H-bridge MLI simulation circuit .The pulse to the switches are given according to the POD technique .The output waveform is seen by connecting a scope.

Fig 8.Cascaded 5 level MLI for POD method

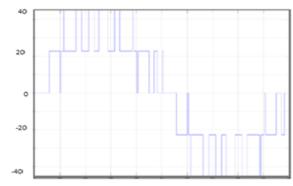

The output waveform produced for this method is shown in figure 9. In phase opposition disposition (POD) technique all those carrier waveforms above zero reference are in phase and those below them are 180 deg out of phase. The THD analysis is done using FFT analysis in MATLAB. The THD obtained for POD is 25.61% is shown in the figure 10.

Fig 9.Voltage output for five level H-bridge MLI using POD Method

Fig 10.THD analysis of POD

# C. Alternate Phase Opposition and Disposition Method

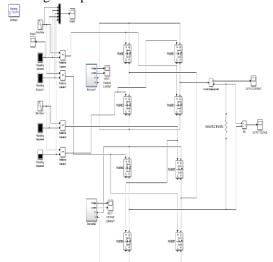

The simulation circuit for a single phase H-bridge MLI is illustrated in the figure 11. The pulse to the switches are given according to the APOD technique. The output waveform is seen by connecting a scope.

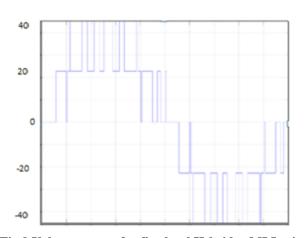

The output waveform produced is shown in the figure 12. For APOD technique modulation all carrier waveforms are out of phase with its neighbour carrier by 180 degree.

Fig 11. Cascaded five level MLI for APOD method

Fig 12.Output Volatge for Five level H-bridge MLI using APOD Method

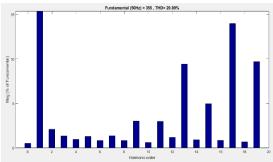

The THD analysis is done using FFT analysis in MATLAB .The THD obtained for POD is 20.89% is shown in figure 13.

# Analysis of Five Level Cascaded H- Bridge Multilevel Inverter using PV Systems

Fig 13.THD analysis of APOD Method

#### V. COMPARITIVE ANALYSIS

The simulation for the above three methods have been done by using MATLAB/SIMULINK and the Total Harmonic Distortion of Alternate Phase Opposition Disposition Method is found to be the least as shown in Table 1. It and has a vast usage in various fields. Thus the hardware has been implemented for the same technique.

**Table 1: THD for Various Methods**

| S.no | Method                                       | %THD for various methods |

|------|----------------------------------------------|--------------------------|

| 1    | Equal Phase                                  | 39.54                    |

| 2    | Phase Opposition Disposition                 | 25.61                    |

| 3    | Alternate Phase<br>Opposition<br>Disposition | 20.89                    |

#### VI. HARDWARE IMPLEMENTATION

The hardware is implemented by interfacing the control circuit, comprising of the PIC controller and the Optocoupler circuit (for electrical isolation), with the power circuit as shown in Figure 14.

Fig 14 .Layout of Hardware

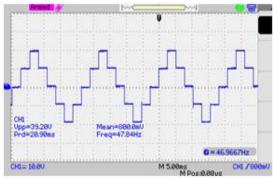

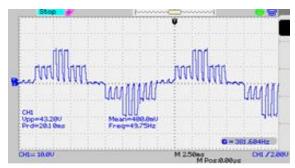

The output waveform produced by EP and APOD method is shown in the Figure 15 and 16 respectively.

Fig 15.Cascaded H-Bridge Five level MLI using EP method

Fig 16.Cascaded H-Bridge Five level MLI using APOD method

# VII. CONCLUSION

In this work, various techniques such as EP Method, POD Method, APOD Method are analyzed and compared. The THD analysis is carried out for various techniques using FFT analysis tool in MATLAB simulation software and it is found that APOD has less distortion of 20.89%. The efficacy of APOD method is verified using hardware implementation of the circuit.

#### **REFERENCES**

- José Rodríguez, Jih-Sheng Lai, and Fang Zheng Peng, "Multilevel inverters: A Survey of topologies, controls, and applications," IEEE Transaction on Industrial Electronics, vol. 49, no. 4, pp. 724–738, August 2002

- Mariusz Malinowski, K. Gopakumar, Jose Rodriguez, and Marcelo A. Pérez, "A survey on cascaded multilevel inverters," IEEE Transaction on Industrial Electronics, Vol. 57, no. 7, pp. 2197–2206, July 2010.

- Tengfei Wang and Yongqiang Zhu, "Analysis and Comparison of Multicarrier PWM Schemes Applied in H-bridge Cascaded Multi-level Inverters", 5<sup>th</sup> IEEE Conference on Industrial Electronics and Applications, June 2010.

- Y. Ounejjar and K. Al-Haddad, "A novel high energetic efficiency multilevel topology with reduced impact on supply network,," in Proceedings of IEEE 34th Annual Conference. Industrial Electronics. (IECON), 2008, pp. 489–494.