# Survey on Routing Algorithms for Fault Tolerant in Network on Chip

# Devendra Rapelli, J. L. Mazher Iqbal

Abstract—Latest styles in VLSI study areas archives a variety of cores systems are built-into solitary chip silicon processor in circumstances of submicron gadget. Also these multi main systems are undertaking huge parallel computation process efficiently using Network on Chip architecture. As a router its fundamental duty is to get rid of the whole delay and in addition power dissipation. In this research paper we will explain usuall router strategies and various issues with their operating strategies and propose new ideas for enhancing its efficiency.

Index terms: Network On chip; Round Robin Arbitration; Dynamic Router; Processing Element.

# 1. INTRODUCTION

On-chip communication is usually taking part in an increasingly dominating part in System about Nick (SoC) style, as the technology scales and nick integrity grows. The common approach to present day time on-chip conversation is usually the centralized bus-based approach, by which the parts on a particular nick communicate over the distributed moderate. This style needs a centralized arbitration system to prevent blockage. Both the solitary moderate and the centralized arbitrator are ineffective and incur very much over head to preserve and make use of efficiently. A very much better strategy is usually to produce an interconnect topology beforehand, and after that designate an user interface that elements should make use of to connect to this interconnected network. This modular strategy to SoC style provides much even more effective conversation by leveraging pc network concepts, which possess been well founded for many years. In the traditional model of distributed coach as a main transmitting moderate to an even more general interconnection network eliminates the want for a centralized visitors control system, reduces contention, and enables higher throughput for on-chip marketing communications.

To meet up with the overall performance and style efficiency requirements, Network on chip is proposed while to provide a better modularity and scalability, dependability and higher bandwidth compared to tour bus based different solution is proposed for conversation infrastructure. As one can imagine, the style options in conditions of structures redirecting reasoning possess a solid effect on the efficiency

# Revised Version Manuscript Received on May 29, 2019.

**Devendra Rapelli**, Research scholar, ECE Department, Vel Tech, Rangarajan Dr. Sagunthala R&D Institute of Science and Technology, Avadi, Chennai, Tamilnadu, India (email: devend.rapelli@gmail.com)

**Dr. J. L. Mazher Iqbal**, Professor. ECE Department, Vel Tech, Rangarajan Dr. Sagunthala R&D Institute of Science and Technology, Avadi, Chennai, Tamilnadu, India (email: mazheriq@gmail.com)

of such chip-based systems. The functionality of Systems on Nick henceforth mainly depends upon the fundamental routing methods, namely result selection and insight selection. Nevertheless, the redirecting methods for NoC possess some exclusive style factors besides low latency and high throughput. Credited to limited restrictions on memory space and processing assets, the redirecting methods for NoC should become fairly basic. Between parts of a nick, the data is usually moved as packets through the network. The interconnecting network includes cables, routers, processors, remembrances and additional Rational House (IP) hindrances linked to routers. A redirecting formula takes on a significant function on network's procedure and decides how the packets are delivered from sender to receiver.

The most important consideration in NoC design is the selection of appropriate architecture based on the application constraints. The primary restrictions to end up being regarded as are throughput, effective usage of silicon nick space and energy dissipation. It is definitely also to become used into accounts, how the design of a particular structures can impact power usage and overall performance. The boost in energy dissipation can vary inversely with respect to boost in throughput (Marconett 2010).

# 2. ASSOCIATED WORKS

Fault Tolerance, efficiency are the two big problems we face during the interconnections of networks for multi-scale processor and architectures. Fault Tolerance serves generally as the power of the entire network to operate during the presence of failures of any element but the methods which identify fault tolerance tends to be a trouble for overall performance degradation. Duato (1997) proposed a theory of fault tolerant adaptive routing that needs per physical channel a minimum of four digital stations.

A different fault tolerant routing algorithm use a digital stations which has been proposed by Recreation area et al (2006). Switches employing a redirecting algorithm that has digital channels and requires extra logic circuits for buffers and multiplexers. Their approach supplies the unwanted characteristic of needing extra logic circuits for buffers and multiplexers that are even more prone to failures.

Zhou and Lau (2001) proposed an issue about tolerant routing algorithm that uses for the routing purpose a virtual station. Faulty links and switches are connected to f-polygons. Around these f-polygons the packets are

delivered. The main problem of this method is, it is generally triggered with the

# International Conference on Multidisciplinary Perspectives in Engineering & Technology (ICMPET-19) |24th -25th May, 2019 | KITS, Markapur, Andhra Pradesh, India

utilization of virtual stations. Regarding an individual faulty physical hyperlink, all digital links owned by that faulty

physical hyperlink become faulty aswell. Boppana and Chalasani (1995) have offered a similar strategy that uses digital stations for fault tolerance and combines the faults in f-chains and f-bands around that your packets are routed. Another strategy for fault tolerance that uses f-chains and f-bands for routing packets around faulty areas is shown in the task by Chen and Chiu (1998).

Li et al (2006) proposed a Dynamic XY (DyXY) routing, that gives adaptive routing a predication for congestion circumstances in the proximity, and makes routing, deadlock-free of charge, livelock-free of simultaneously. The algorithm uses devoted wires to research the position of the neighboring switches. The drawback is usually that its foresight is bound and it could show just the position of the neighbouring nodes as occupied or not really. Another routing algorithm acquiring the position of a change into consideration is provided by Hu et al (2004b). The change decides to path a packet right into a particular direction predicated on its own position and the position of its outgoing queues.

# 3. PRESENT ARBITRATION TECHNIQUES

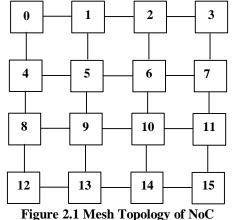

On-chip systems are made up of an arranged of distributed router nodes and communication stations, and the network topology refers to the set up of these nodes and communication stations. It straight impacts all essential network guidelines like route size, router difficulty, latency and throughput. These variables translate into efficiency and power of the network. Greatest choice of topology for a particular software is dependent on

style goals and guidelines. From the conversation perspective, there possess been numerous topologies for NoC structures. These consist of Mesh, Torus, Band, Butterfly, Octagon and abnormal interconnection systems. There are a great deal of study functions reported in books dealing with NoCs topology era. Bei Yu et al (2010) possess suggested a strategy to style the appropriate topology that minimizes the power intake of interconnects and network parts in NoC.

#### 3.2 CROSSBAR ROUTING SWITCH

This element is responsible for linking router input buffers to router outcome buffers. High-speed routers will make use of crossbar systems with total connection, while lower-speed implementations may utilize systems that perform not really actually present full connection between understanding buffers and result buffers. The metres Occasions n can connect any of the metres guidelines to each of the n outcomes. The primary concern when making use of a crossbar as the switch in a router datapath is usually normally to give speed up on the understanding of the crossbar, the result of the crossbar or on both sides. The speedup can become provided in space or period.

#### 3.3 HYPERLINK CONTROLLER

Across the physical funnel, flow control between close by routers is usually applied with this gadget. On either component of a channel the link controllers are synchronized to transfer stream control products. Adequate loading must finish up becoming provided on obtaining element to accounts for delays in distribution of data and motion control signals. As soon as a controller on the result path indications hurdle comprehensive placement through an event, the controller at the understanding channel must have sufficient buffer in the transit to store all of the phits, also all the phits that will become shot during the period needs for the stream control transmitting to propagate back again once again to the result route. The controller in the digital channels are also responsible for resolving the received phit's destination channel.

#### 3.4 Virtual Path Controller

For multiplexing, the contents of the virtual channel on the physical channel this component is responsible. The keep off can finish up getting expected to become logarithmic in the amount of channels by using tree-based arbitration,

# 3.5 Redirecting And Arbitration Unit

Manipulating and arbitration gadget equipment the routing function, The message headers are ready to compute the collection of applicant result channels and generate needs for adaptive routing protocols. If important contraindications coping with is generally getting used in the network, the new headers, one for each applicant effect path must finish up becoming created. For ignorant routing protocols, header update is generally an incredibly fundamental process.

Manipulating and arbitration gadget also deploys the selection function of the routing process: chosing the end result internet web page web page link for an incoming meaning. Result direct placement is generally combined with understanding path needs. Problems for the same result must finish up getting arbitrated and if comparative coping with can become used, a header must end up being chosen. If the requested buffers are full, the inbound message proceeds to become in the understanding obstacle until a requested buffers converts into free of charge of charge. Quantity 2.6 depicts a complete crossbar that links all insight virtual channels to all effect virtual channels. Additionally, a router may also utilizes a design where total connection is normally

simply provided between physical channels, and digital channels arbitrate for crossbar understanding slot

machines. Fast arbitration's recommendations are essential in keeping low blood circulation control latency through the modification.

#### 3.6 BUFFERS

Usually FIFO (Preliminary In Initial Out) buffers are used for storing text message communications in transit. In the router model exhibited in Form 2.6, a hurdle is associated with both understanding and result physical channels. The stream size is certainly an important quantity of motion control items. In alternative designs, buffers may become connected simply with tips (understanding loading) or outcomes (result loading). In package switching, however, a package is generally delivered through a path as quickly as that path is generally arranged apart, but the pursuing path is certainly not really actually appropriated (supposing that it can end up being accessible) until the container generates the route it is definitely certainly currently using. Certainly, some barriers space can be normally required to store the package before pursuing path can become organized. That screen should finish up becoming allocated before starting container sending. Consequently, hurdle allocation is generally cautiously related to the switching program.

#### 4 TURNING STRATEGIES IN SYSTEMS ON CHIP

Network stream control also called viewing that routing environment, determines just how packets are transmitted inside a network. The establishing is generally not really actually right reliant to manipulating formula. Many algorithms are designed to utilize some offered establishing, but the bulk of them perform not really actually define which establishing should become used. The switching strategies generally used for on-chip systems are store and forward, digital cut-through and wormhole switching whose features are known while going after areas.

#### 4.1 SHOP AND AHEAD SWITCHING

Store and ahead is the simplest routing environment. Packets move in one piece, and entire package requirements to become held in the router's storage space before it can finish up becoming delivered to the pursuing router. Consequently the hurdle memory space requirements to end up being as large as the largest container in the network. The latency is generally the combined period of obtaining a package and sending it ahead. Sending cannot become started before the whole package is generally received and held in the router's storage space.

# 4.2 VIRTUAL CUT-THROUGH SWITCHING

Virtual cut-through is usually normally an improved version of store and ahead mode. When the pursuing router provides authorization the router begins to send out package to the pursuing router. Package is generally held in the router until the forwarding begins. Forwarding can finish up getting started before the whole package is certainly received and held to router. In this switching placing, actually even more buffer storage space is certainly needed similar to store and

forward placing, but the latency can become lower. Hu and Marculescu (2004a) have demonstrated a hurdle planning requirements that applications the obstacle depth at each understanding path of the router organized on the software features. When digital cut-through switching is usually utilized, the packets are regarded as solitary client.

#### 4.3 WORMHOLE SWITCHING

In wormhole turning, packets are divided into little and equivalent sized flits (stream control digit or stream control unit). A 1st flit of a packet is definitely certainly delivered likewise as packets in the digital cut-through redirecting. After initial flit, the path is usually set aside to path the staying flits of the packet. This path is definitely known as wormhole. Wormhole setting needs much less memory space than the two additional settings because just one flit requirements to end up being held at once. Also the latency can be smaller sized and a risk of deadlock is certainly bigger. The risk can become decreased by multiplexing many digital slots to one physical opening, therefore the possibility of visitors blockage and obstructing reduces. Schwiebert and Jayasimha (1995) possess analyzed the required and plenty of condition for deadlock free of charge redirecting for wormhole routers. The regional info of the router is normally regarded because non-local details may increase the style difficulty. Hu and Kleinrock (1997) possess created an analytical model for wormhole router with finite size buffers. The model uses a deadlock free of charge redirecting algorithm.

#### 4.4 MULTICAST ROUTING

Multicast, or one-to-many, conversation is a basic collective discussion procedure and is highly demanded in parallel control and telecommunication applications. Instances of such applications consist of Fast Fourier Transform (FFT), challenge synchronization, and produce update / invalidate in directory-centered cache coherence protocols (Lin and Ni 1993). Also, teleconferencing and video broadcasting are common applications in a telecommunication environment. There's been developing attention in helping multicast in parallel pc systems. Multicast could end up being supported in either gear or software program. There's been very much concentrate on assisting multicast in wormhole sent instant systems in software program system. In addition, there's been some concentrate on helping multicast in software program plan in multistage systems (Duato et al 2003).

Generally, the multicasting problem could be patterned simply by three routing techniques: unicast based, tree-based (Malumbres et al 1996) and route- based routing (Lin and Ni 1993). The multicast procedure in unicast based method generally performes its process by sending a person, a copy of message to every destination from the basis, else by sending the unicast messages to various subset of places. The disadvantage of this plan usually is credited to the real truth

that multiple copies of the same message are shot in to the network and the traffic

# International Conference on Multidisciplinary Perspectives in Engineering & Technology (ICMPET-19) |24th -25th May, 2019 | KITS, Markapur, Andhra Pradesh, India

of such network will be increased. then, each copy of such messages will drop substantial start-up latency at the resource. In tree-structured multicast technique, a composed of forest is usually generally constructed in that your resource is usually normally indicated as the primary and after that marketing communications are delivered down the woods. In this way a message could duplicate itself at a quantity of the intermediate nodes and sent along multiple outgoing channels toward disjoint subsets of locations. Each message is usually obstructed if every branch of the woods is generally clogged,. Twigs must continue forward in stop stage, which may lead to a message to bring many channels for prolonged time periods, producing in increasing network contention.

Although such schemes need to be used effectively in networks employing store and forward, virtual cut-through routing and tree-based routing incur high congestion in wormhole networks (Lin and Ni 1994). A response to overcome the disadvantage of tree-centered redirecting is usually by using the route organised multicast wormhole redirecting. In this technique, a source node works on a notice for delivery to a few of places by 1scapital t selecting the details of the destination to end up being capable where they should become shipped, and putting this categorized list in the header of the message. Several research possess verified a path-centered show excellent general overall performance quality over their unicast-structured and tree-centered counterparts (Boppana et al 1998). Yuanyuan Yang (1998) gives offered a program of interconnection systems for assisting multicast marketing communications in parallel digesting systems.

### 4.5. OBLIVIOUS ROUTING

Ignorant routing algorithms have no info regarding circumstances of the network, like visitors quantities or congestions. A router makes manipulating decisions on the factors of some method for example arbitrarily. The simplest ignorant manipulating algorithm is certainly a minimal switch manipulating. It methods packets using as few turns into as feasible.

# 4.6. ADAPTIVE ROUTING

Duato (1993) has proposed for wormhole networks the a deadlock-free adaptive routing algorithm. The manipulating algorithms which are also fault-tolerant experienced been simulated; it exhibited higher general efficiency. The effect of the digital stations skilled been studied in their function. Chiu (2000) provides supplied a model that restricts packets obtaining particular transforms without usage of digital stations, therefore staying away from deadlock. Their new results screen regular level of adaptiveness for every arranged of source-destination nodes. Though the model can finish up becoming long term to non-uniform site visitors, they perform not really actually support issue tolerance.

Obstruction occurs in personal computer systems when a resource requirements exceed the ability we actually at the. as packets fill up the lines and collection size evolves until packets are decreased. Actually though the bandwidth of the network links can end up being raised, the blockage will not

really get reduced because boost in hyperlink variety causes severe blockage. In Systems on Nick, IP hindrances that may generate arbitrary quantity of visitors are connected. Depending on the route variety and quantity of digesting cores, blockage turns into unavoidable. Common solutions to prevent blockage are blockage centered redirecting, where an alternative route with much less blockage is usually selected. Raising the barrier size will become an alternative answer that compensate for brief bursts but on-chip systems are source limited.

Kim et al (2005) had devised a new router constructions which utilizes adaptive routing. Their low latency two-stage pipelined buildings uses boundary obstruction placement to select the ideal result path with low latency. The manipulating process shows reduced energy intake. Ascia et al (2006) released the concept of Neighbors-on-Path to consider benefit of the conditions of indecision that can happen in an adaptive wormhole manipulating. The stream placement of the boundary nodes is definitely certainly known by dedicated signals organized on which the route of very much less obstruction is generally calculated. Change model redirecting is definitely structured on barring specific becomes during the packet redirecting to prevent deadlocks.

# 4.7 DETERMINISTIC ROUTING

As a function of the destination address deterministic routing algorithms establish the path, between each single pair of node. A deterministic redirecting protocol will usually offer the same result route for the same destination. While deterministic algorithms are oblivious, the talk is usually not really always accurate. Deterministic redirecting became extremely well-known when the wormhole switching was broadly utilized. One primary advantage of deterministic redirecting can be its simplicity when it comes to router style. Because of the simple reasoning, the deterministic redirecting provides low latency when the network isn't very overloaded. Nevertheless, the deterministic routers fail to react dynamically to network blockage when the packet inserted into the network raises.

It is simple to compute the distance between current and destination nodes in the case of Hypercubes, Meshes, and Torus topologies as the sum of the offsets in all the sizes,. The simplest manipulating algorithm consists of reducing an counteract to zero before acquiring into concern the counter top in the following dimensions known as Dimensions Purchase Redirecting (Ni and McKinley 1993). Sizing Buy Redirecting (DOR) warranties a minimal jump count number and offers a basic implementation which makes it a well-known choice for NoC systems. While DOR performs well at low network weight credited to the brief header latency, its functionality degrades quickly as the fill on the network boosts credited to absence of insert managing. It can be known as XY redirecting for the 2D Mesh topology and e-cube redirecting for Hypercubes. A range vector redirecting and a hyperlink condition redirecting are shortest route

redirecting algorithms. Ali et al (1997) provides studied the require for problem tolerant algorithms. They possess suggested basic type of hyperlink condition redirecting criteria that fits a NoC in the event of failures.

# 4.8 MISTAKE TOLERANCE IN SYSTEMS ON CHIP

For large-scale multiprocessor architectures performance and fault tolerance are two dominating problems that faces the design of interconnection networks. Problem threshold is usually normally the capability of the network to function in the presence of element failures. Nevertheless, methods utilized to identify mistake threshold are frequently at the expenditure of significant overall performance degradation. Duato (1997) suggested a theory of problem tolerant adaptive routing which needs at least four digital stations per physical funnel.

One more routing algorithm that is fault tolerant uses digital channels was proposed by Recreation area et al (2006). Changes making use of a manipulating formula with digital stations want extra reasoning circuits for buffers and multiplexers. Their strategy provides the unwanted quality of needing extra reasoning circuits for buffers and multiplexers that are even more responsible to failures.

Zhou and Lau (2001) proposed an issue tolerant routing algorithm which uses virtual stations for the routing. Faulty links and changes are blended to f-polygons. The packets are delivered around these f-polygons. The main disadvantage of this answer is generally brought on by the utilization of digital channels. In the case of a solitary faulty physical hyperlink, all digital links owed to that faulty physical link become faulty as well. Boppana and Chalasani (1995) possess shown a comparable strategy that uses digital stations for mistake threshold and combines the problems in f-chains and f-rings around which the packets are sent. Another technique for problem patience that uses f-chains and f-bands for redirecting packets around faulty areas is usually provided in the function by Chen and Chiu (1998).

# 5. CONCLUSION & FUTURE PLANS

The router architecture of the Network on chip and its elements are discussed. Analysis functions related to different types of redirecting algorithms are also offered. Existing functions related to adaptive and mistake tolerant wormhole redirecting are talked about. The want for blockage control system which forms the essential intent of this research can be also stressed.

# **REFERENCES**

- Ahmed Aldammas.: The efficiency of buffer and buffer-less data-flow control schemes for congestion avoidance in Networks on Chip. In: Journal of King Saud University – Computer and Information Sciences, pp. 96–112 (2016)

- Carloni, L.P., Pande, P., Xie, Y.: Networks-on-chip in emerging interconnect paradigms: advantages and challenges. In: Proceedings of the 2009 3rd ACM/IEEE International Symposium on Networks-on-Chip, pp. 93–102 (2009)

- Rahmani, A.-M., Latif, K., Vaddina, K.R., Liljeberg, P., Plosila, J., Tenhunen, H.: Congestion aware, fault tolerant and thermally efficient inter-layer communication scheme for hybrid NoC-bus 3D architectures. In: Proceedings of the 5th ACM/IEEE International Symposium on Networks-on-Chip, pp. 65–2 (2011)

- Feero, B.S., Pande, P.P.: Networks-on-chip in a three-dimensional environment: a performance evaluation. IEEE Trans. Comput. 58(1),

- 32-45 (2009)

- Pavlidis, V.F., Friedman, E.G.: 3-D topologies for networks-on-chip. IEEE Trans. Very Large Scale Integr. Syst. 15(10), 1081–1090 (2007)

- John Jose, Bhawna Nayak, Kranthi Kumar, Madhu Mutyam, "DeBAR: Deflection based adaptive router with minimal buffering", in Design Automation and Test in Europe Conference, pp.1583-1588, March 2013.

- Jing Lin, Xiaola Lin, Liang Tang, "Making-a-stop: A new bufferless routing algorithm for on-chip network", Elsevier Publish Journal of Parallel and Distributed Computing, pp.515-524, 2012.

- Chris Fallin, Greg Nazario, Xiangyao Yu, Kevin Chang, Rachata Ausavarungnirun, Onur Mutlu, "MinBD: Minimally-Buffered Deflection Routing for Energy-Efficient Interconnect", in Sixth IEEE/ACM International Symposium on Networks on Chip (NoC), pp.1-10, May 2012.

- 9. Robert Mullins, Andrew West, Simon Moore, "Low-Latency Virtual-Channel Routers for On-Chip Networks", ISCA, 2004.

- Cota E, Morais Antony, Soares Lubaszewski, "Reliability, Availability and Serviceability of Networks- on- Chip," Springer, 2010.