M. Saravanan, R. Arun Sekar, Ramanan S.V, M. Srinivasaperumal

Abstract: This paper centers around the plan of Fixed width multipliers utilizing Baugh-Wooley based corner calculation. The greatest supreme mistake after truncation is ensured to be close to 1 unit of minimum position (ulp), by utilizing the adjusted settled width multiplier plan. Fixed width multiplier is a subset of Fixed width multiplier, registers just n most noteworthy bits for n\*n increase. In the traditional strategy cancellation, decrease, truncation and adjusting techniques are considered together with the end goal to limit the quantity of half adders and full adders amid tree decrease. This plans to diminish the most extreme stature of the halfway item exhibit and standard designs. This system is quite compelling in all multiplier outlines, however particularly in the short piece width two's supplement multipliers for elite installed centers. The Booth based stall calculation is a moderately clear method for doing marked augmentations. The proposed Fixed width Booth based corner multiplier is contrasted and the customary Fixed width marked multiplier got from quantization plot. It has executed in Multiply and Accumulate (MAC) unit and Arithmetic and Logic Unit (ALU) and FIR channels utilizing settled width Booth based corner multiplier. The proposed technique beats existing strategy regarding area and delay.

Index Terms: Multiply and Accumulate (MAC), Baugh-Wooley (BW), Booth multiplier, Full adders (FA), Ripple Carry adder (RCA), Fixed width multiplier, signed multiplier.

### I. INTRODUCTION

Multiplication is a vital math task and multiplier executions date quite a few years back in time. Increases were initially performed by iteratively using the ALU"s adder. As timing limitations ended up stricter with expanding clock rates, committed multiplier equipment executions, for example, the cluster multiplier was presented. From that point forward perpetually, refined strategies on the best way to execute augmentations have been proposed. Multipliers [1] are in truth complex adder exhibits. This is a task basic to a substantial number of utilizations, and the many-sided quality of this capacity has prompted a lot of research coordinated at accelerating its execution. Multipliers can be executed utilizing diverse calculations. Contingent upon the calculation utilized the execution qualities of the multipliers change. In the usage of computerized multipliers paired adders are a basic segment. With the rise of intensity as an outline thought, speed isn't the main model by which different executions are

### Revised Manuscript Received on June 05, 2019

M. Saravanan, Department of ECE, SNS College of Technology, Coimbatore, Tamil Nadu, India.

R.Arun Sekar, Department of ECE, GMR Institute of Technology, Rajam, Andhra Pradesh, India

Ramanan. S.V, Department of ECE, PPG Institute of Technology, Coimbatore, Tamil Nadu, India.

**M. Srinivasaperumal**,. Department of ECE, SNS College of Technology, Coimbatore, Tamil Nadu, India.

judged. Outlining multipliers with low power, vitality effective adders decrease the power utilization and effectiveness of multipliers.

### A. MOTIVATION

In this task, plan the Fixed width multiplier [2] utilizing Booth calculation. Fixed width multiplier has a similar piece width of info and yield. In advanced flag handling frameworks multiplier assumes a critical job yet in addition it expends more power and region. With the end goal to lessen power and territory involved, settled width multipliers are outlined. Settled width property rearranges the multiplier structure with the point of enhancing power and speed. Fixed width multipliers don't frame the majority of the slightest critical sections in the halfway item lattice. Yield is the weighted total of halfway items. By taking out more sections the region and power utilization of the number juggling unit are fundamentally diminished and by and large the delay likewise diminishes. Region sparing of this multiplier can be accomplished by specifically truncating n minimum huge segments and safeguarding n most critical columns. The BW calculation is a moderately clear method for doing marked augmentations. It utilizes just a variety of FA and a last RCA.

## B. CONCEPT

Multiplication is an intricate number juggling activity, or, in other words its generally high flag spread postponement, high power dissemination and huge area prerequisite. While picking a multiplier for a computerized framework, the bit width of the multiplier is required to be in any event as wide as the biggest operand of the applications that are to be kept running on that advanced framework. The bit width of the multiplier is, in this way, regularly substantially bigger than its operands, which prompts over the top power scattering and long deferral. This could somewhat be helped by having a few multipliers, each with a particular piece width, and utilizing the specific multiplier with the littlest piece width that is sufficiently huge for the present increase. In numerous applications, the sources of info and the yield of the multiplier have a similar piece width. These multipliers are called as fixed width multipliers. fixed width multipliers are utilized to diminish the region and power involved by the multiplier unit. fixed width multiplier assumes an imperative job in computerized flag handling.

### II. BAUGH-WOOLEY ALGORITHM

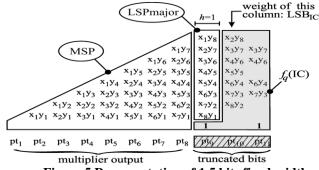

The BW calculation is a generally straight forward method for doing marked duplications. The fixed width multipliers got from BW calculation create n-bit yield item with n-bit multiplier and n-bit multiplicand. It is an effective method to deal with the sign piece. BW multiplier utilizes just FA. All piece items are created in parallel and gathered through a variety of FA and last RCA. The formation of the rearranged halfway item cluster involves three stages: Most Significant Bit (MSB) of the principal N-1 incomplete item columns and all bits of the last fractional item push, with the exception of its MSB, are modified.

A "1" is added to the Nth section.

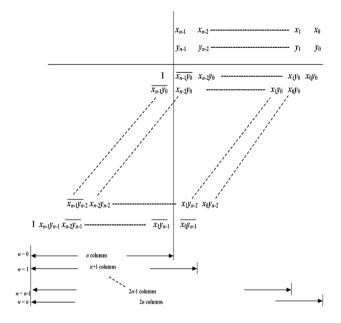

The MSB of the last outcome is nullified. Figure 1 portrays partial product array diagram for n×n BW multiplier.

Figure 1 Schematic of Partial Product Array representation

### III. FIXED WIDTH MULTIPLIER

Parallel multipliers are essential building hinders in mixed media and advanced numerous applications, the sources of info and the yield of the multiplier have a similar piece width. These circuits are indicated in writing as settled width multipliers or settled width multipliers. The clearest approach to outline a settled width multiplier utilizes a full-width n x n multiplier, whose yield is settled width/adjusted to n bits by n releasing the less-huge bits of the items. The settled width property, in any case, can be misused to rearrange the multiplier structure, with the point of enhancing power and speed. Essentially, one can dispose of a portion of the incomplete items in the fractional items cluster to decrease the circuit multifaceted nature, at a cost regarding precision. This is the methodology sought after in all the settled width multiplier models proposed in writing.

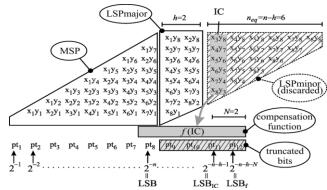

Figure 2 Partial-products matrix of a 8x8 bit multiplier, fixed width with h=2

Figure 2 demonstrates the design of a common fixed width multiplier [3-5]. In this model, without loss of sweeping statement, the information sources x and y are thought to be two unsigned numbers. The halfway items are separated into two subsets. The minimum huge part (LSP) incorporates the less noteworthy sections of the fractional item cluster, while the Most Significant Part (MSP) incorporates the rest of the segments. Thus, LSP is subdivided in LSP major and LSP minor. The LSP major incorporates the most noteworthy sections of LSP (h is a plan parameter that can extend from h = 0 to h = n), while the rest of the neq= n-h segments establish the LSP minor.

As appeared in Figure 2, the incomplete items in LSP minor are dropped, and this is remunerated with the presentation of an appropriate pay work. The remuneration work itself can have when all is said in done, a discretionary accuracy. It will expect that the remuneration work is spoken to with N-1 partial bits as for the heaviness of the IC segment (see Figure 2). Numerous mistake remuneration strategies have been proposed in writing. In the least complex methodologies, the remuneration work is a settled predisposition. Better precision is gotten in the supposed variable-redress (or versatile) settled width multipliers. In these structures, the halfway items in the furthest left segment of LSP minor are utilized to acquire a probabilistic gauge of the aggregate of the components of the LSP minor.

In Figure 2 the fractional items in the furthest left segment of LSP minor are featured in dark and are named Input Correction (IC), while f(IC) is the remuneration work.

The decision f(IC) of is the basic advance in the plan of a settled width multiplier. This capacity ought to be productively actualized in equipment, and ought to give, in the meantime, a great gauge of the whole of the components of the LSP minor. A fixed width multiplier [6-9] dependent on an alternate methodology is displayed. For this situation, the rectification is computed as a component of halfway results of the LSP minor not having a place with the IC. This supposed multiplier, in any case, depends on Multiplexer-based multiplier which isn't suited for tree-based convey spare usage because of halfway items figured as the aftereffect of carry propagate increases.

The majority of the fixed width multipliers proposed to date demonstrate a few confinements. Sometimes, they result in rather expansive estimation mistakes in different cases they require the usage of a moderate as well as power hungry circuit for f(IC).

In this work it demonstrates that the ideal quantized coefficients (as far as mean square mistake) can be acquired the arrangement of a whole number quadratic programming issue. New fixed width multiplier topologies, with various region exactness exchange off, are at that point gotten by changing the quantization plot. Two topologies are specifically chosen as the best ones. The first (named "2 bits settled width multiplier") depends on a uniform coefficient quantization with two bits. The second topology ("1.5 pieces settled width multiplier") depends on a non-uniform quantization where a portion of the coefficients (around one-portion of the aggregate coefficients) are quantized with two bits, while the rest of the coefficients are quantized with a solitary piece. The proposed fixed width multiplier topologies display better precision concerning past arrangements, near the hypothetical lower bound.

The equipment execution of the novel 2 bits and 1.5 bits fixed width multipliers is likewise explored in this paper. It is demonstrated that the multipliers can be ideally acknowledged by presenting a little assistant carry save decrease tree before the last carry propagate adder. The exhibitions of the proposed fixed width multipliers are broadly contrasted and past designs. It is discovered that deepest of the examined cases the proposed topologies are Pareto-ideal, giving the best exchange off among precision and equipment intricacy.

# IV. FIXED-WIDTH MULTIPLIERS PARTIAL-PRODUCTS MATRIX

The 2 bits and 1.5 bits fixed width multipliers [10,11] are effortlessly actualized by summing an altered halfway item network (PPM). Give us a chance to consider, for instance, 2 bits settled width Multiplier with n=8 and h=1. For this situation neq=n-h=7 there is a remarkable ideal answer for the qi coefficients: q0=2.q1=q2=... q7=1.5 .The pay work is given by

$$fq(IC)=LSBIC[2+1.5x3y7+...+1.5x8y2].$$

(1.1)

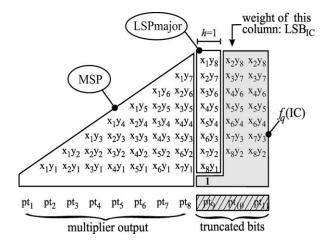

Figure 3 Representation of the 2 bits fixed-width multiplier, for: n=8.h=1.

Figure 3 demonstrates another case of 2 bits fixed width multiplier. For this situation n=8 and h=0. Since n=q=n-h=8 there are different ideal solutions. As saw before it pick the arrangement with q1=q8=1 that marginally disentangles the PPM. The ideal coefficients are: q0=1, q2==q7=1.5, q8=1 and the remuneration work is

$$fq(IC)=LSBIC[1.5+x1y8+1.5x2y7+.+1.5x7y2+x8y1].$$

(1.2)

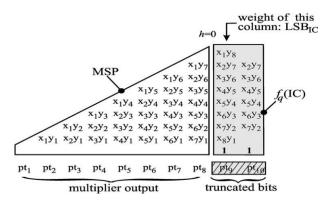

**Figure 4** Representation of 2 bits fixed-width multiplier, for: n=8, h=0.

As it very well may be seen in Figure 4, the fractional items from x2y7 to x7y2 are embedded twice in the PPM, while the two incomplete items x1y8 and x8y1 seem just in the segment with weight LSBIC. The steady factor is executed by embeddings two 1s in the sections with weight LSBIC and LSBIC/2.

The usage of a 1.5 bits settled width multiplier is appeared in Figure 5. For this situation it is accepted n=8, h=1. The ideal coefficients are:

q0=2.5, q1=1, q2=q3=1.5, q4=1, q5=q6=1.5, q7=1, and the remuneration work is

$$\begin{array}{c} fq(IC) = LSBIC.[2.5 + x2y8 + 1.5x3y7 + 1.5x4y6 + x\\ 5y5 + 1.5x6y4 + 1.5x7y3 + x8y2]. \end{array} \tag{1.3}$$

By looking at Figure 4 and 2, it very well may be seen that the PPM of the 1.5 bits multiplier is less difficult that the PPM of the 2 bits multiplier. Truth be told, just four fractional items are embedded in the furthest right segment (rather than seven).

The consistent term is somewhat bigger in the 1.5 bits multiplier, requiring the addition of two 1 s in the two sections with weight 2LSBIC and LSBIC/2.

Figure 5 Representation of 1.5 bits fixed-width multiplier, for: n=8, h=1.

### V. SIMULATION RESULTS

This recreation results demonstrates that different execution of settled width multipliers utilizing direct pay systems and furthermore demonstrates the gadget usage relating settled width multipliers. The instruments utilized for recreation of the calculation is Xilinx ISE.

|                                | 2                                                        | ,000,000 ps |

|--------------------------------|----------------------------------------------------------|-------------|

| Name Value                     | 1,999,996 ps  1,999,997 ps  1,999,998 ps  1,999,999 ps 2 | ,000,000 ps |

| ▶ 🦷 ×[7:0] 11111111            | 11111111                                                 |             |

| ► N y[7:0] 11111111            | 11111111                                                 |             |

| ► 1111110010 x                 | 1111110010                                               |             |

| ▶ N p[63:0] /walace/y[7:0] 111 | 111111111111111111111111111111111111111                  |             |

| ▶ 🧏 s[33:1] 1111111111         | 111111111111111111111111111111111111111                  |             |

| ▶ 🧏 d[33:1] 1111111111         | 111111111111111111111111111111111111111                  |             |

| 1 1                            | ·                                                        |             |

|                                |                                                          |             |

|                                |                                                          |             |

| 1 1                            |                                                          |             |

| 1 1                            |                                                          |             |

|                                |                                                          |             |

| 1 1                            |                                                          |             |

|                                |                                                          |             |

|                                |                                                          |             |

|                                |                                                          |             |

|                                |                                                          |             |

|                                |                                                          |             |

| 1                              |                                                          |             |

|                                |                                                          |             |

|                                | X1: 2,000,000 ps                                         |             |

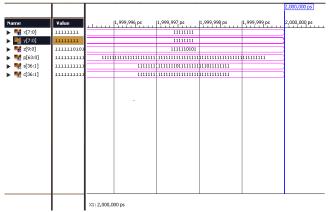

**Figure 6** Simulation Output of Fixed-Width Multiplier (n=8, h=0)

The reenactment waveform of fixed width straight remuneration multiplier utilizing Xilinx reproduction instrument is appeared in Figure 6. Given sources of info are x and y which have 8-bits esteem. The yield is z and it contains 10-bits including 8-bits of settled width bits.

| Name         | Value       |                  | 1,999,994,24  |                                         | 11,999,990 pe | 1,000,000 ps |  |  |  |

|--------------|-------------|------------------|---------------|-----------------------------------------|---------------|--------------|--|--|--|

| ■ ¼ ×(7:0)   | 11111111    |                  |               | 11111111                                |               |              |  |  |  |

| ► ■ 1(7/#)   | ******      |                  |               | 1011010                                 |               |              |  |  |  |

| ► ¾ (10:00)  | 1111111000  |                  |               | 11111110001                             |               |              |  |  |  |

| ▶ № µ(63:0)  | 11111111111 | 111111           |               |                                         |               | 11111111     |  |  |  |

| ► ™ (43:1)   | ********    |                  |               | 111111111111111111111111111111111111111 |               |              |  |  |  |

| ► *** (40:1) | ********    |                  | 1111111111111 |                                         |               |              |  |  |  |

|              |             |                  |               |                                         |               |              |  |  |  |

|              |             | X1: 2,000,000 рв |               |                                         |               |              |  |  |  |

Figure 7 Simulation Output of Fixed-Width Multiplier (n=8, h=1)

Figure 7 demonstrates the reenactment waveform of 2 bit settled width Linear Compensation multiplier utilizing Xilinx instrument. The given sources of info a and b. 8-bits double qualities are given to the info. The yield is z, which have the 11-bits including

settled width bits of 7-bits.

Figure 8 Simulation Waveform of Fixed-Width Multiplier (n=8,h=1)

Figure 8 demonstrates the reproduction waveform of 1.5 piece settled width Linear Compensation multiplier utilizing Xilinx device. The given sources of info an and b. 8-bits parallel qualities are given to the information. The yield is z, which have the 10-bits including settled width bits of 7-bits.

# A. POWER REPORT OF NORMAL AND FIXED WIDTH MULTIPLIER

Table 1 Comparison result of power in multipliers

| POWER<br>REPORT |       | FIXED WIDTH<br>MULTIPLIER |

|-----------------|-------|---------------------------|

| POWER<br>VALUES | 0.056 | 0.049                     |

Table 1 shows the comparison results of power values in multipliers. Fixed width multiplier is less power consumption than normal multipliers. Figure 8 shows the graphical representation of power analysis between the normal and Fixed width multiplier.

### B. COMPARISION OF FIXED WIDTH MULTIPLIER

Table 2 Comparison result of fixed width linear compensation multipliers

| FIXED<br>WIDTH<br>MULTIPLIER | LOGIC<br>UTILIZATION | Number of 4 input LUTs | Number<br>of<br>occupied<br>Slices | Number<br>of Slices<br>containing<br>only | Number<br>of Slices<br>containing<br>unrelated | Total<br>Number<br>of 4<br>input<br>LUTs | Number<br>of<br>bonded<br>IOBs | Average<br>Fanout<br>of Non-<br>Clock<br>Nets |

|------------------------------|----------------------|------------------------|------------------------------------|-------------------------------------------|------------------------------------------------|------------------------------------------|--------------------------------|-----------------------------------------------|

|                              | Uses                 | 103                    | 57                                 | 57                                        | 0                                              | 103                                      | 27                             |                                               |

| 2BIT,H=0                     | Available            | 1,536                  | 768                                | 57                                        | 57                                             | 1,536                                    | 63                             | 2.95                                          |

|                              | Utilization          | 6%                     | 7%                                 | 100%                                      | 0%                                             | 6%                                       | 42%                            |                                               |

|                              | Uses                 | 336                    | 181                                | 181                                       | 0                                              | 336                                      | 50                             |                                               |

| 2BIT,H=1                     | Available            | 1,536                  | 768                                | 181                                       | 181                                            | 1,536                                    | 63                             | 3.05                                          |

|                              | Utilization          | 21%                    | 23%                                | 100%                                      | 0%                                             | 21%                                      | 79%                            |                                               |

|                              | Uses                 | 83                     | 43                                 | 43                                        | 0                                              | 83                                       | 25                             |                                               |

| 1.5BIT,H=1                   | Available            | 1,536                  | 768                                | 43                                        | 43                                             | 1,536                                    | 97                             | 2.91                                          |

|                              | Utilization          | 5%                     | 5%                                 | 100%                                      | 0%                                             | 5%                                       | 25%                            |                                               |

Thus, Comparison result of all the above discussed fixed width multipliers are showed as per the synthesis report. From this table 2 implementation of 1.5-bit fixed width multiplier is efficient compare to other type of fixed width multipliers.

# **C.BOOTH MULTIPLIER**

Despite the fact that Wallace Tree multipliers were quicker than the customary Carry Save Method, it likewise was exceptionally sporadic and thus was confused while drawing the Layouts. Gradually when multiplier bits get past 32-bits huge quantities of rationale entryways are required and henceforth likewise all the more interconnecting wires which makes chip plan expansive and backs off working rate. Corner multiplier can be utilized in various modes, for example, radix-2, radix-4, radix-8 and so forth. Be that as it may, we chose to utilize Radix-4 Booth's Algorithm in light of number of Partial items is diminished to n/2.

### **D.FIR FILTER**

Filters are flag conditioners. The channel capacities by tolerating an information flag, blocking pre-specified recurrence segments and passing the first short those segments to the output. Digital channel takes an advanced information, gives a computerized yield and comprises of advanced segments. A simple channel by complexity works specifically on the simple information

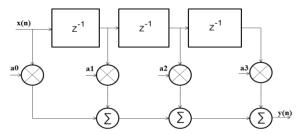

and is fabricate completely with simple segments, for example, resistors, capacitors and inductors. Channels when all is said in done consider as low pass, high pass, band pass and band stop. A low pass is convenient it's utilized for constraining the upper most scope of frequencies in a sound flag. A high pass channel is to dismiss just the recurrence segments cry some edge. The band pass channel is to guarantee the yield motions inside its thin inside the range recurrence range are transmitted. The band stop channels pass both high and low frequencies to hinder a predefined scope of frequencies in the center. A limited drive reaction (FIR) channel is a channel structure that can be utilized to execute any kind of recurrence reaction carefully. An FIR channel is generally executed by utilizing a progression of delay, multipliers, and adders The FIR channel square graph appeared in Figure.9 beneath is of length 4. Figure 10-12 shows the output waveform, area and power analysis report.

Figure 9 Block diagram of FIR filter

# E. Fixed width Multiplier Using FIR Filter

|                 | Value             | Ι. | 1 000 700 |       | 11 000 000 | 100       | 11 000 000 - |         | 11 001 000 00  | 11.00   | 1 100 ex   |              | 001 000  |       | 11 001 300 | 100    |

|-----------------|-------------------|----|-----------|-------|------------|-----------|--------------|---------|----------------|---------|------------|--------------|----------|-------|------------|--------|

| ame             | Value             |    | 1,000,700 | ps    | 1,000,800  | ps .      | 1,000,900 p  |         | 1,001,000 ps   | 1/0     | 1,100 ps   |              | 001,200  | 10    | 1,001,300  | ps.    |

| l <b>g</b> dk   | 1                 | _  |           |       |            | _         |              |         |                | -       |            | _            |          |       |            | $\Box$ |

| la ca           | 0                 | _  |           |       |            |           |              |         |                | _       |            | _            |          |       |            |        |

| ₹ a[9:0]        | 0000000001        |    |           |       |            |           |              |         | 0000000001     |         |            |              |          |       |            |        |

| <b>1</b> b[9:0] | 0000000001        |    |           |       |            |           |              |         | 0000000001     |         |            |              |          |       |            |        |

| <b>¾</b> (9:0]  | 0000000001        |    |           |       |            |           |              |         | 0000000001     |         |            |              |          |       |            |        |

| <b>4</b> 4[9:0] | 0000000001        |    |           |       |            |           |              |         | 0000000001     |         |            |              |          |       |            |        |

| ₩ y[12:0]       | 44                |    |           |       |            |           |              |         | 44             |         |            |              |          |       |            |        |

| ₹ yy[-3:3]      | (11111111110,1111 |    |           |       | [1111111   | 110,11111 | 11100,1111   | 111011, | 1111111110,111 | 1111100 | ,11111110  | 11,1 1       | 1111011] |       |            |        |

| <b>™</b> a[9:0] | 1111111011        | 11 |           |       | 11111      | 11011     |              |         | 11111111110    |         | 1111111100 | 0            |          | 11111 | 11011      |        |

| <b>₩</b> f[9:0] | 1111111011        | 11 | 111111    | 11100 |            |           | 1111111      | 011     |                |         | 111111111  | 0            | 111111   | 1100  | 11111      | 11011  |

| <b>1</b> g[9:0] | 1111111100        | 11 | 111111    | 11110 |            |           | 1111111      | 100     |                |         | 1111111011 | 1            | 111111   | 1110  | 11111      | 11100  |

| ₹ h(9:0)        | 1111111110        | 11 | 111111    | 11011 |            |           | 1111111      | 110     |                |         | 111111100  | 0            | 111111   | 1011  | 11111      | 11110  |

| l@in            | 0                 | 10 | - 11      | 1     | 10         | 00        | 0            |         | 1              |         | 10         | $=$ $\times$ | 11       |       | - 1        | 00     |

| ₹ w1[12:0]      | 0000000001011     |    |           |       |            |           |              | 0       | 000000001011   |         |            |              |          |       |            |        |

| ₩ w2(12:0)      | 0000000001011     |    |           |       |            |           |              | 0       | 000000001011   |         |            |              |          |       |            |        |

| ₹ w3(12:0)      | 0000000001011     |    |           |       |            |           |              | 0       | 000000001011   |         |            |              |          |       |            |        |

| ₹ w4(12:0)      | 0000000001011     |    |           |       |            |           |              | 0       | 000000001011   |         |            |              |          |       |            |        |

| ₹ w5(12:0)      | 22                |    |           |       |            |           |              |         | 22             |         |            |              |          |       |            |        |

| ₩ w6(12:0)      | 22                |    |           |       |            |           |              |         | 22             |         |            |              |          |       |            |        |

|                 |                   |    |           |       |            |           |              |         |                |         |            |              |          |       |            |        |

|                 |                   |    |           |       |            |           |              |         |                |         |            |              |          |       |            |        |

Figure 10 Output waveform

| Device Utilization Summary                     |      |           |             |  |  |  |  |  |

|------------------------------------------------|------|-----------|-------------|--|--|--|--|--|

| Logic Utilization                              | Used | Available | Utilization |  |  |  |  |  |

| Number of Slice Flip Flops                     | 47   | 4,896     | 1%          |  |  |  |  |  |

| Number of 4 input LUTs                         | 590  | 4,896     | 12%         |  |  |  |  |  |

| Number of occupied Slices                      | 330  | 2,448     | 13%         |  |  |  |  |  |

| Number of Slices containing only related logic | 330  | 330       | 100%        |  |  |  |  |  |

| Number of Slices containing unrelated logic    | 0    | 330       | 0%          |  |  |  |  |  |

| Total Number of 4 input LUTs                   | 621  | 4,896     | 12%         |  |  |  |  |  |

| Number used as logic                           | 590  |           |             |  |  |  |  |  |

| Number used as a route-thru                    | 31   |           |             |  |  |  |  |  |

| Number of bonded <u>IOBs</u>                   | 54   | 158       | 34%         |  |  |  |  |  |

| Number of BUFGMUXs                             | 1    | 24        | 4%          |  |  |  |  |  |

| Average Fanout of Non-Clock Nets               | 3.21 |           |             |  |  |  |  |  |

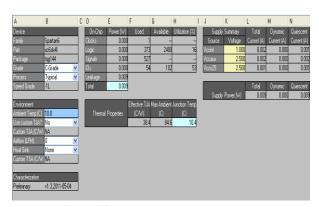

Figure 11 Area analysis

Figure 12 Power analysis

For applying the fixed width multiplier in FIR filter the obtained delay is 6.189ns and frequency is 161.584 MHz.

**Table 3** Signed multiplier comparisons

| MULTIPLIERS                    | AREA<br>(Slices) | POWER(W) | DELAY(ns) | FREQ<br>(MHZ) |

|--------------------------------|------------------|----------|-----------|---------------|

| SIGNED<br>BOOTH                | 141              | 0.093    | 4.361     | 229.<br>305   |

| SIGNED<br>FIXED-WIDTH<br>BOOTH | 116              | 0.041    | 3.114     | 321.14        |

Table 3 shows the comparison of signed Booth multiplier with Fixed width multiplier. It is seen that the area, power and delay decreases by 17.73%, 55.91% and 28.59% respectively.

# F. Comparison of Multipliers Using FIR Filter

Table 4 Multiplier comparisons using FIR filter

| MULTIPLIER                     | AREA (slices) | POWER<br>(W) | DELAY(nS) |

|--------------------------------|---------------|--------------|-----------|

| UNSIGNED<br>FIXED              | 330           | 0.009        | 6.189     |

| SIGNED BOOTH                   | 259           | 0.029        | 5.98      |

| SIGNED<br>FIXED-WIDTH<br>BOOTH | 185           | 0.011        | 5.145     |

# G. Comparative Results of Slices, LUTs and Power for Different Multipliers

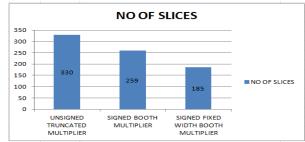

Figure 13 Comparative graph of slices for Different Multipliers

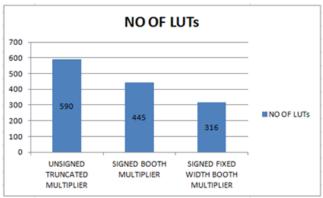

Figure 14 Comparative graph of LUT's for Different Multipliers

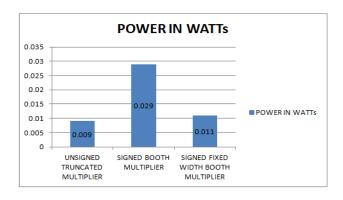

Figure 15 Comparative graph of power for Different Multipliers

Figure 13-15 shows the comparative graph of number of slices, LUT's and Power analysis of different multiplier implemented in FIR filter. Table 4 explains the comparative analysis of area, power and delay for different multipliers implemented in FIR filter. It is noted that though there is a slight increase in power, the area and power are reduced by 43.93% and 16.86% respectively.

### **REFERENCES**

- Antonious. A, El-Guibaly. F and Kidambi. S.S., (1996) "Area-efficient multipliers for digital signal processing applications," IEEE Trans. Circuits and Systems II, Analog Digit. Signal Process, vol. 43, no. 2, pp. 90–95.

- De Caro. D, Garofalo. V, Petra. N, Napoli. E, and Strollo. A.G.M, (2010) "Fixed width binary multipliers with variable correction and minimum mean square error," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 6, pp. 1312-1325.

- Duverne. O.M, Stine. J.E, (2003) Variations on fixed width multiplication," in Proc. Euromicro Symp. Digit. Syst., pp. 112–119.

- Feng. W, Van. L, Wang. S, (2009) "Design of the lower error fixed-width multiplier and its application," IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process, vol. 47, no. 10, pp. 1112-1118.

- Garofalo. V, (2009) "Fixed width binary multipliers with minimum mean square error: Analytical characterization, circuit implementation and applications," Ph. D. dissertation, Dept. Electron. Eng., Univ.

- Kuang. S.R and Wang. J.P. (2006) "Low-error configurable fixed width multipliers for multiply-accumulate applications," Electron. Lett., vol. 42, no. 16, pp. 904–905.

- Magnus Själander. C and Per Larsson-Edefors, (2009) "Multiplication Acceleration Through Twin Precision". In IEEE Transactions on Very Large-Scale Integration (VLSI) Systems, vol. 17, NO. 9.

- Michard. R, Tisserand. A, and Veyrat-Charvillon. N, (2006) "Carry prediction and selection for fixed width multiplication," in Proc. Workshop Signal Process. Syst. (SiPS), Banff, AB, Canada, pp. 339–344.

- Nicola Petra, Davide De Caro, Valeria Garofalo, Ettore Napoli, (2011)

Antonio Giuseppe Mario Strollo," Design of Fixed Width Multipliers with Linear Compensation Function", IEEE Trans. Circuit Syst, vol 58, no.5.

# **AUTHORS PROFILE**

M.Saravanan received the B.E Degree in Electrical and Electronics Engineering from Coimbatore Institute of Technology- Coimbatore, India in 2006 and M.E VLSI Design from Anna University Coimbatore- Coimbatore, India in 2009. He is working as an Associate Professor in the Department of Electronics and Communication Engineering at SNS College of Technology, Coimbatore, India. His research interest includes VLSI design and

Semiconductor devices.

Arun Sekar.R was born in Tamil Nadu, India in 1986.He received his Bachelor's degree from Sri Ramakrishna Engineering College in 2008 and his Master's degree in VLSI Design in 2013.He is currently working as an Assistant professor in the Department of Electronics and Communication Engineering at GMR Institute of Technology, Rajam, Andhra Pradesh. He is a Part-time

Research Scholar under Anna University, Chennai. He had published more than 24 papers in International conferences and 10 reputed Journals. His areas of interest are Low power VLSI design and Image processing. He is a member of ISTE, IETE, ISRD and IEANG

Ramanan S.V Pursuing Ph.D. in Sensor networks at Anna University Chennai. Has completed his PG in ME CS at SNS college of Technology in 2013.He done his UG in BE ECE at SNS college of Technology in 2009. He is working as an Assistant Professor at PPG Institute of Technology for past six years. Has given several guest lectures and seminars in subject domains and awarded as best speaker in the year 2017. Has presented several

papers in International and National Conferences and also published in reputed journals.

M.Srinivasaperumal, working as Assistant professor in Department of Electronics and Communication Engineering at SNS College of technology with 5 years of research and teaching experience. Have completed his under graduation in ECE with distinction and Post-graduation in Communication Systems under Anna University, Coimbatore. Empathetic interest in research motivated him to publish 12 research articles

in reputed International conference and 10 research articles in reputed international journals.