# Comparative Analysis on Designs of Comparators with Different Techniques and **Technologies**

Ujjayini Debnath, Shobha Sharma, Amita Dev, Preeti Singh

Abstract: Comparators are used in Analog to digital convertors (ADC) as their basic element. There are several types of comparators, some of them are preamplifier based comparator, latch based comparator, dual tailed etc. Nowadays in semiconductor industries there is demand for very less power consumption, as well as high operating speed. The purpose of the paper here, is to analyses several comparators circuits and analysis on their power consumptions and delays, and further the proposed version. The design of double tailed comparator consists of two stages. First one is preamplifier stage and another one is latching stage. Basically the proposed versions of comparators are modified for high speed operations and of course for low power consumption with low power supply. For higher speed, NAND structures (latch) have not been used instead of NOR gate. Because NOR are generally slow. This paper depicts some of parameter comparison. These comparator circuits are being improved day by day to specify some attributes depending upon the criteria and of course by using new techniques such as boot strapping, offset elimination, noise reduction, clock gating etc.

Index Terms: Analog to Digital Comparator, delay, dynamic comparator, preamplifier latch, low power.

## I. INTRODUCTION

Comparators are one of the favorable elements in designing of integrated circuits like for digital, analog, and mixed signal as well. The comparator does compare two signals, either it be digital signal or analog signal. The comparator basically based on two phases of operations, reset phase is primary phase, and set stage is the second one (for clocked input type). The one of most prominent criteria for deducing power consumption is that to scale the input voltage supply. This is because of the reason that, due to the complementary-MOS digital circuits, delivery of average power is always proportional to the whole square of the input voltage supplied.

#### Revised Manuscript Received on June 05, 2019

Ujjayini Debnath, Electronics and Communication, Indira Gandhi Delhi Technical University for women, Delhi, India.

Dr Shobha Sharma, Corresponding Author, Faculty, Electronics and Communication, Indira Gandhi Delhi Technical University for women, Delhi

Prof Amita Dev, Pro VC, Indira Gandhi Delhi Technical University for

Preeti Singh, Electronics and Communication, Indira Gandhi Delhi Technical University for women, Delhi, India

## $P = C_L V_{dd}^2 F_d$

Where, the consumption of power is P for a single gate,  $C_L$  is capacitance (switching) of a single gate, is the supply-voltage;  $F_d$  is the cooperating frequency (avg.) of a single gate.

## II. RELATED WORK

As conventional comparator circuit, the double-tailed comparator also compares any two input signal such as currents /voltages, produces digital output. The double-tail comparator also made up of PMOS and NMOS transistors. This CMOS comparator functions as comparing element for a signal with the other fixed signal, which is called as reference signal. This comparator comprises with a differential type amplifier, which has very strong gain stage. The basic component block in analog-digital converters (ADCs) is comparator, which performs the data conversion from analog to digital or digital to analog vice versa

Ultra Low Power convertors are using to enhance the power efficiency and the speed which is used as regenerative stage comparators. This Paper depicts expression and analysis of delay and power of the comparators. This approach is developed for Low-power Low-voltage and quick speed operation. These simulations are based on 180nm, 90 nm, 250 nm, 130nm CMOS Technology etc.

To speed up the power trade, the comparator circuit is not immune. The flash type ADC has high speed as very low delay that uses large aspect ratio MOS transistors and therefore consumes high power.

Therefore, a comparator should be selected based on special application. Hence in ultra-deep submicron/deep submicron technology CMOS techniques, the designing of such high speed comparator circuits are the most problematic when input voltage supply kept small.

Table 1: Parameters and their value for 180 nm CMOS technology [1]

| Sl. No. | Parameters           | Values     |

|---------|----------------------|------------|

| 1       | Technology           | 180nm CMOS |

| 2       | Power<br>Supply      | 1.2 V      |

| 3       | Power<br>Dissipation | 329uW      |

## Comparison on Design of various Comparators Analysis

| 4 | Delay     | 550 Ps  |

|---|-----------|---------|

| 5 | Frequency | 500 MHz |

Table 1 shows some parameter values for a conventional type comparator (figure 1), Generally the double-tailed comparator circuits are very faster, usually faster than the conventional ones. Mostly the higher speed ADCs, such as we can say flash type ADCs, are required high in speed, these Comparators consumes also less power

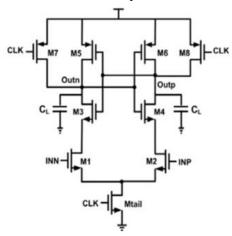

Fig 1: Schematic for a Dynamic Conventional Comparator

The above figure shows Schematic of circuit for a Dynamic Conventional Comparator. In this figure there are two basic parts, which can be divided into phases. One is reset phase, during this CLK is Zero "0",  $M_{tail}$  OFF. Another phase is comparison stage. In this CLK is High or CLK= $V_{\rm dd}$ .

Here in this paper [1], compares delays, power consumption between two comparator structures, one is Dynamic and another is Double-tailed. Another paper has shown a Latch Comparator. The proposed technology is executed in 65nm CMOS Technology. In this paper they have shown that he supply voltage taken to simulate the basic circuit is 1.2 V [2],[4].

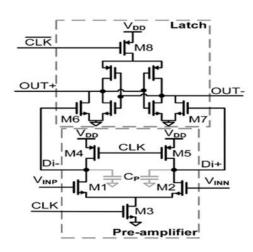

Fig 2: Latch Type Comparator (Double-Tail)

This figure 2 shows Double-tail Latch Type Comparator, which includes capacitors that ensures partial charge and discharge which reduces energy consumption. This approach has no isolation between differential input and regeneration Latch stage, regeneration Latch undergoes some kickbacks. As shown in this picture there are two Tail Capacitors are C<sub>p</sub>,

the corresponding energy w.r.t.  $V_{dd}$  is fixed (2 x  $C_pV_{dd}$ ). When CLK = $V_{dd}$ . Ctail initialailly charges.

This approach has low overhead, Low-power consumption is only due to partial discharge of capacitors. Comparators are used in ADCs (Analog-to-Digital Comparators). These comparators are made-up of CMOS (PMOS and CMOS) and Bi-CMOS [3]. This paper basically shows offset cancellations. This comparator structure has also two stages Preamplifier and Latch. Here offset is less than 300 microvolt. Power dissipation is 1.8 mw. This paper showed some design techniques which provides some advantages such as High-resolution, improved speed, and very less power consumption with obviously minimum complexity.

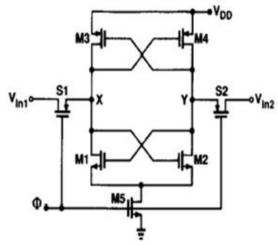

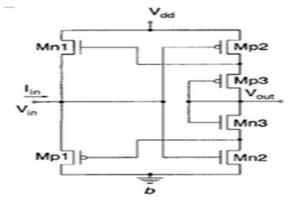

**Fig 3:** CMOS switching Latch circuit used in comparator This paper shows offset cancellation techniques for both stages, Pre-amplifier and Latch with Low-Power Dissipation. This paper worked on CMOS current comparator. This type of comparators represents real-time data processing. This paper shows comparators based on current mirror [5].

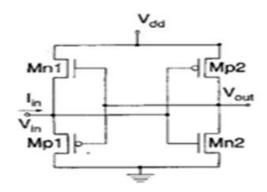

Fig 4: Tarff's circuit.

Fig 5: Another of Proposed Circuit

Table 2: parameters for above structure [5]

| Sl. No. | Transistors | Width um | Length<br>um |

|---------|-------------|----------|--------------|

| 1       | Mn1         | 5        | 2.5          |

| 2       | Mp1         | 24       | 2.5          |

| 3       | Mn2         | 5        | 4.0          |

| 4       | Mp2         | 24       | 4.0          |

| 5       | Mn3         | 20       | 2.0          |

| 6       | Mp3         | 60       | 2.0          |

Table 2 is for another paper [6]. This paper worked on  $0.13\mu m$  or 130nm technology. Voltage supply was 1.2v. Delay .62ns & power dissipation was 1.5nw. Overall purpose of this paper was to reduce power consumption, by minimizing the size of transistors being used [6].

This paper is based on 65nm Technology; purpose of this paper is to increase speed. But, Static power is high though sine is minimized. The paper showed on chip designing of comparator, which produces high frequency signals with 31% higher speed. [7]

Technology node is being used 22nm, this circuits has two advantages- Noise Immunity, Low Leakage Current. Domino logic based Comparator minimizes the parasitic, where two currents are being compared (One Marmoreal Current & another is Leakage) [8]. This paper uses 90nm technology. Here comparator circuit uses cross coupled transistors which improve speed of the circuit [9].

This paper reveals 0.18µm technology using dynamic latch structure. Thus works on high frequency 400MW. It uses a preamplifier stage. This enhances the speed of the comparator circuit [10]. This is done on 90nm technology (GPDK). Comparator has various uses, such ADC, level shifter, window detector, relaxation oscillator, null detector. Here in this paper design comprises of some phases divided into three parts such as - (a) Pre-amplifier Stage (b) Decision Making Stage (c) Buffer Stage at the Output, Power supply required is 1 volt. Circuit obtained minimum offset voltage, better noise immunity [12].

Technology used is 0.18µm. Power supply required for successive approximation ADC using SR latch is 1.5V. Clock frequency is 0.1 MHz, Power consumption 191pW. Proper transistor size helps to achieve higher resolution. Output of the comparator should be stable during clock cycle [11].

#### III. SURVEY ON COMPARATOR

| Paper Name                                                                                              | Technology                | Power                                          | Delay    |

|---------------------------------------------------------------------------------------------------------|---------------------------|------------------------------------------------|----------|

| Analysis/Design of<br>Low-Voltage<br>Low-Power                                                          | 180 nm                    | Dissipation  1.4 mw                            | 358 ps   |

| Double-Tail Comparator.  Design/analysis of high                                                        |                           |                                                |          |

| speed double tailed<br>comparator with<br>isomorphic latch                                              | 180/65 CMOS<br>technology | 1.3 mw                                         | 500 ps   |

| Design a Dynamic<br>latch comparator with<br>reduced kick back                                          | 180 nm                    | 1.0049 mw                                      | -        |

| Design of high speed<br>dynamic double tailed<br>comparator                                             | 250 nm                    | 0.9307 mw                                      | 12.72 ns |

| Comparator Power<br>Minimization Analysis<br>for SAR ADC Using<br>Multiple Comparators                  | Theoretical               | 50–60% less                                    |          |

| A 5 Bit ADC with two comparator                                                                         | 55                        |                                                | 50ps     |

| Substrate noise<br>measurement by using<br>noise selective voltage<br>comparator mixed<br>signal IC     | 50                        |                                                | 0.1-1 ns |

| Concept of superconducting comparator for pipeline ADC                                                  |                           |                                                |          |

| A 1.2 V dynamic bias<br>latch size comparator<br>in 65 nm CMOS with<br>0.4 mV input noise               | 65 nm CMOS                |                                                |          |

| Understanding the potential and limitation of tunnel FET for low voltage analog/ mixed signal circuits. | 10 nm FINFET              | 10% Improved                                   |          |

| Low power 600 Mhz<br>comparator for 0.5 V<br>supply voltage in 0.12<br>um cMOS                          | 120 nm CMOS               | 2.65 mw                                        | 11 ns    |

| A 7.65 mW 5 bit 90 nM<br>1GS/S folded<br>interpolated ADC with<br>calibration                           | 90 nm CMOS                | 7.65 mw                                        |          |

| Ultra Low voltage high<br>speed flash ADC<br>design strategy based<br>on FoM delay product              | 90 nm CMOS                | 4.1 mw Exploring English and Exploring English | 365ps    |

|                                                                                                         |                           | 1 5 T                                          |          |

2955

JIIEE

## **Comparison on Design of various Comparators Analysis**

| One comparator counter based controller for synchronous DC/DC converter                                                                     | MATLAB            |        | 30 ms    |

|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------|----------|

| A current mode Comparator for Digital Calibration of Amorphous Silicon AMOLED Display(AMOLD- AC Matrix organic light emitting diode Display | 800nm             |        |          |

| A Mux Based igh<br>performacce single<br>cycle CMOS<br>comparator                                                                           | 350nm             |        | 50ps     |

| Design Approach using<br>tunnel diodes for<br>lowering Power in<br>differential comparator                                                  |                   | 3.5mw  | F=100GHZ |

| Kickback Noise<br>Reduction Techniques<br>for CMOS latched<br>Comparators                                                                   | 180nm<br>(HSPICE) | 268mw  |          |

| Offset reduction<br>techniques for use with<br>high speed CMOS<br>comparator                                                                | lum               |        |          |

| Design of a low power<br>high speed comparator<br>in 0.13um CMOS                                                                            | 130nM             | 1.5 mw | 0.62 ns  |

## IV. CONCLUSION

Most of these papers have shown the conventional comparators as well as the proposed version and modified versions and explained about the consumption of power and the delay; noise etc. the comparator circuits are implemented in 32nm, 90nm, 180nm CMOS technology. The software used are CADENCE, LTSPICE, and SYNOPSIS, MENTOR GRAPHICS etc. After analyzing all the papers we can come to the conclusion that in today's era of chip scaling (area, power and delay) in Integrated circuit (IC) industry it's highly important to alleviate the Power consumption and to minimize the propagation Delay as well. Thus the several proposed version of these comparators are introduced.

#### ACKNOWLEDGMENT

I express my sincere gratitude to **Dr. Shobha Sharma** (**Asst. Prof.**), for providing me an opportunity to undergo major project in "**Comparison on design of various comparator Analysis**".

I will be very thankful to her, for her all support, all cooperation, and all motivation, which she has provided to me during the Seminar for constant inspiration, presence and blessings. I appreciate that despite of her busy schedule she gave her valuable suggestions and precious time in

accomplishing my report.

#### REFERENCES

- Samaneh Babayan-Mashhadi, Reza Lotfi "Analysis and Design of a Low-Voltage Low-Power Double-Tail Comparator", IEEE Trans. On Very Large Scale Integration (VLSI) Systems, Vol. 22, No. 2, February 2014.

- Harjjot Singh Bindra, Christiaan E. Lokin, Daniel Schinkel, Anne-Johan Annema, Bram Nauta, "A 1.2-V Dynamic Bias Latch-type Comparator in 65-nm CMOS With 0.4-mV Input Noise", IEEE Journal Of Solid State Circuits, Vol. 53, No. 7, July 2018

- Behzad Razavi and Bruce A. Wooley, "Design Techniques For High-Speed, High-Resolution Comparators", *IEEE Journal Of Solid-State Circuits*, Vol. 27, No. 12, December 1992.

- L. Ravezzi and D. Stoppa and G.-F Dalla Betta, "Simple High-speed CMOS Current Comparator", *IEEE 1997 Electronics Letters Online No: 19971250*, 19 August 1997.

- B.B.A. Fouzy, MBI Reaz, MAS Bhuiya, M.T.J. Badal, F.H. Hashim, "Design of a Low Power High Speed Comparator In 0.13 μm CMOS", International conference on advances in Electrical, Electronic & System Engineering, 14-16 Nov, 2016.

- A. Manikandan, J.Ajayan, C.Kavin Avasan, S. Karthik, K.Vivek; "High Speed low power 64 bit comparison Based domino Logic." *IEEE sponsored 2<sup>nd</sup> International Conference on Electronics & Communication Systems (ICECS)*, 2015.

- Mohamed Abbas, Yasuo Furukawa, Satoshi Komatsu, Takahiro. J. Yamaguchi. Kunihiro Ajada; "Clocked Comparator for High Speed Application in 65nm Technology", *IEEE Asian* Solid-State Circuits Conference 8-10 November, 2010.

- Rahul jain, Animesh K. Dubey, Vikrant Varshing Rajendra Kumar Nagaria, "Design of low power high speed Double fast Dynamic CMOS Comparator using Novel Latch Structure" *IEEE Uttar Pradesh Section International Conference*, 26-28 October, 2017.

- Had Aghabeigi, Mehdi Tafaripanah, "High Speed low power Voltage Comparator .18um CMOS process for Flash ADCs" International Conference on knowledge based Engineering & Innovation (KBFJ), Dec 2<sup>nd</sup>, 2017.

- Satyabrata Nanda, Avipsa S. Panda. "Design of Conventional Three-stage CMOS comparator in 90nm CMOS Technology and comparative analysis with its counterparts", *International Conference on Smart Sensor and Systems (IC-SSS)*, 2015.

- Iffa Sharauddin and L.Lee, "Modified SR Latch in Dynamic comparator for Ultra-low Power SAR ADC", IEEE International Circuits and Systems Symposium (ICSYS), 2015.

## **AUTHORS PROFILE**

**Ujjayini Debnath** is perusing her M. Tech in VLSI Technology (Electronics and Communication Engineering) from Indira Gandhi Delhi Technical University for Women (IGDTUW). Her areas of research include Very Large Scale Integration (VLSI) design.

Dr Shobha Sharma, Faculty, Indira Gandhi Delhi Technical University for Women (IGDTUW). Delhi, India. **Corresponding Author**

Prof Amita Dev Pro-VC Indira Gandhi Delhi Technical University for Women (IGDTUW). Delhi, India.