# A Place and Power Effective Square Root Carry Choose Adder Design by 3t-Xor Gate and Typical Boolean Logic

R.Kavitha, G.Kavitha, C.Anuradha, N.Priya

Abstract The Fastest viper among snake that is standard is perceived as Carry pick viper (CSLA). This calls for effective CSLA understudies of territory, deferral and vitality of the framework. In this square is changed CSLA includes 3T-XOR entryway plan and average Boolean rationale (CBL) rearrangements. The 3 Transistor XOR door diminishes the measure of transistors inside the XOR entryway of this viper circuit and following the sane rearrangements we require only one Inverter and one OR door for summation and convey apportion that is operation. Through the multiplexer, we can discover the creation that is comparing with rationale states in regards to the convey in sign. Predicated on this alteration SQRT CSLA design have been thought about and created utilizing the customary, Binary to Excess-1 (BEC) adjusted, CBL changed SQRT CSLA models. The proposed engineering accomplishes the advantages as far as pause, p and territory ower.

Keywords: CSLA, RCA, 3T-XOR Gate, BEC, Boolean Logic.

## I. INTRODUCTION

TODAY, there are lots of Electronic applications uses adders for functionality of digital system and function that is arithmetic. They are found in multipliers, Digital sign processors to perform algorithms like FFT, IIR, and FIR filters, Microprocessors to perform million guidelines per moments are done, thus the rate of procedure in many component that is essential design. The performance is in electronic adders restricted to the carry propagation period of the adder sum each bit in adder is created sequentially just following the past bit place is summed and propagation of the carry towards the position that is next. In several systems which can be computational can be used to mitigate the carry propagation wait by producing separate providers which are numerous generate the amount by picking provider sign. But CSLA just isn't area efficient since it utilizes numerous pairs of Ripple carry adders [1] to come up with carry and sum by considering carry in=0,and carryin=1,then finally the choose that is multiplexer amount and carry[2].

#### Revised Manuscript Received on July 22, 2019.

**R.Kavitha**, Deparment of Computer Science and Engineering, Bharath Institute of Higher Education and Research, Tamilnadu,India. Email: kavis\_happy@yahoo.co.in

**G.Kavitha**, Deparment of Computer Science and Engineering, Bharath Institute of Higher Education and Research, Tamilnadu,India. Email: kavithag90@gmail.com

C.Anuradha, Department of Computer Science and Engineering, Bharath Institute of Higher Education and Research, Tamilnadu,India. Email: anuradha.ak23@gmail.com

**N.Priya**, Deparment of Computer Science and Engineering, Bharath Institute of Higher Education and Research, Tamilnadu,India. Email: priyabiher@gmail.com

The prevailing modified SQRT CSLA u sing Binary to Excess-3 converter instead of RCA for Cin=1 in regular CSLA accomplished reduced energy and area usage and somewhat increases in wait. In another modified CSLA method utilized with the Common Boolean logic simplified the duplicate adder cells in carry pick adder by using NOT and gate that is OR selecting output based on past carry- out signal [3].

This paper is arranged the following; Section II explains the SQRT that is regular CSLA Section III explains modified SQRT CSLA together with step-by-step framework of Binary to Excess-3 Converter and Common Boolean logic correspondingly. Part IV deals modified SQRT CSLA by blended gate that is 3T-XOR CBL. Area V explains the proposed Architecture. In Section VIArea delay and, power result are analysed and concludes.[4][5]

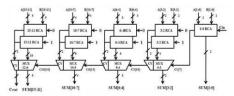

Figure 1: 16 Bit Regular SQRT CSLA.

The square that is regular CSLA h as twin ripple carry adder with 2:1 multiplexer. Principal d rawback of regular CSLA has area that is large to multiple pairs of RCA. The normal 16 bit CSLA shown in figure1 [1], its divided in to five teams with various bit size of RCA through the framework is always to decrease the area an power usage that is d. The carry down determined from very first phase offered as carry input to your stage that is next of for production carry and amount. The choice is completed through multiplexer [1]. One input to your multiplexer from RCA with Cin=0 and another input from RCA with Cin=1.

| Binary[3:0] | Excess-1[3:0] |

|-------------|---------------|

| 0000        | 0001          |

| 0001        | 0010          |

| 0010        | 0011          |

| -           | -             |

| -           |               |

| 1101        | 1110          |

| 1110        | 1111          |

| 1111        | 0000          |

|             |               |

|             |               |

|             |               |

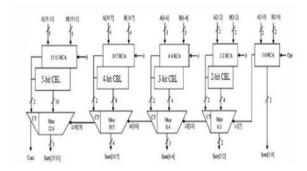

# II. MODIFIED SQRT CSLA OPERATING BEC

In modified CSLA RCA that is dual been replaced with Binary to extra -1

converter carry sign Cin=1, which paid down the location and energy usage of regular CSLA. N+1 BEC is required [2] in an effort to replace n-bit RCA.[6][7][8] The dwelling and dining table that is practical of BEC is shown in Table 1[2].

| A|||64|| | B|||64|| | A|||64|| | B||64|| | A||64|| | A

Figure 2: 16 Bit Modified S QRT CSLA with BEC.

Table 1: 4-Bit BEC Practical Table.

The Boolean expressions of 4-Bit BEC is detailed a s,  $X0=\sim B0$

$X1 = B0 \land B1$

$X2 = B2 \land (B0\&B1)$

$X3 = ^ that is b3B0&B1&B2)$

The modified 16 CSLA that is bit utilizing is shown in Figure 2, Group[9][10]

3 of modified 16 bit CSLA shown in figure has gate count of 61 and the wait is s which are 18n. BEC replaces the p arallel RCA with Cin=1. Principal downside in this technique d elay increased in comparison with regular CSLA.[11][12]

BEC MODIFIED CSLA OPERATING CBL

Drawbacks of BEC modified CSLA is overcome by changing[13][14]

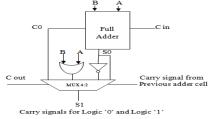

BEC with common logic that is boolean. CBL eliminates replicated adder cells into the CSLA which saves numerous transistor counts and achieves power[3] that is low. The production of summation sign the carry in sign of logic[15][16]

'0' is inverse of its carry in signal for logic '1'; the modification carried

away as opposed to BEC is shown in figure 3,

Figure 3: Common Boolean logic in Comprehensive adder

# III. MODIFIED CSLA OPERATING XOR THAT IS 3-T ATE AND CB

XOR gates will be the building that's basic of adder. Within our system that is proposed XOR in adder circuits are

changed with 3-T XOR gate, this has that energy usage of the circuit decreases with big enhance in range switching Transistors (MOSFETS) found in the look of 16 bit CSLA.[17][18]

Figure 4: 3-T XOR gate

The dwelling that is basic f 3 -T XOR gate is shown in figure 4 along side its area count and p ropagation d elay. [19][20]Nonetheless 3-T XOR gate has reduced energy usage in comparison with XOR that is 12-T normal XOR gate,[21][22][23] following the modification by 3-T X OR, 2nd phase of adder RCA is changed with CBL for simplification of carry in logic '0' and logic '1' by OR and Inverter gates.[24][25][26]

#### IV. EXPERIMENTAL RESULTS

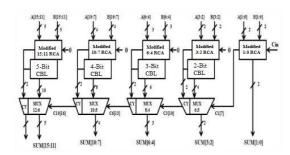

In proposed technique RCA that is initial adder gate is changed with 3-T XOR [27][28][29] gate which creates energy that is low and wait. Internal framework of proposed SQRT CSLA is shown in figure 6. Following the generation of carry signals for offering selection that is multiplexer BEC is changed by common Boolean logic, CBL simplification is composed of one OR gate plus one Inverter gate.[30][31][32]

Figure 5: The Proposed 16-Bit CSLA making use of 3-T XOR and CBL

Through the multiplexer, we can pick the production outcome that is true in line with the logic state of input carry signal. In 16 bit quantity that is architecture of utilized for team 3 is 36 (complete adder, Half adder, Multiplexer, never, OR gate). One input visits the from that is multiplexer RCA for Cin=0 as well as other input from typical logic block that is boolean. Group 3 executes 3 bit addition carried out by twoComprehensive adders and another Half adder, through 2:1 multiplexer then the execute

sign is propagating to your adder mobile that is next.[33][34]

The modified X gate that is OR transistor count, energy usage and power delay product performance of CSLA, in comparison with 12-T XOR gate 9 lower transistors has been utilized which Reduces arp and ea propagation wait. The decrease that is total gate and transistor count for every single team is calculated as, [35][36]

Group 1: it has one Comprehensive adder, each adder that is filled with two3-T XOR gates then your transistor count decrease is 18 (2\*9),

Group 2 : It contains one whole a half and dder adder, with 2-bit CBL, Total XOR gate utilized = 3(2+1); Lowering of Transistor count = 27(3\*9).

Group 3: it includes two adder that is complete half adder with 3-bit CBL, Total XOR gate utilized = 5 (2\*2+1); Decrease in Transistor count =45 (5\*9).

Group 4: it includes three adder that is complete half adder with 4-bit CBL, Total XOR gate utilized = 7 (3\*2+1); Lowering of Transistor count = 63 (7\*9).

Group 5: it has four f adder that is full half adder with 5-bit CBL, Total XOR gate utilized = 9 (4\*2+1); Decrease in Transistor count = 81 (9\*9).

To ensure that in proposed system 320 switching transistors is paid off has set alongside the formerly created CSLA that is 16-bit has just 180 transistors.

# V. REVIEW OF PROPOSED SYSTEM

Proposed and altered reproduction of CSLA was finished using Xilinx reenactment gadget and Spartan 3E once the objective gadget.

The primary disadvantages of adjusted CSLA u sing BEC and CBL is expanded pause and Transistor check, this would be overwhelmed by our design that is suggested that the transistor tally, region, deferral and vitality use contrasted with the customary and altered CSLA.[38][39]

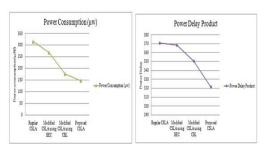

Figure 6(a): Area and Delay Comparison of adders

Figure 6(b): energy product comparison that is delay.

Its clear from dining table 2 that the transistor count in CBL modified CSLA is paid off by 57.6per cent whenever contrasted to modified CSLA practices,[37] whenever contrasted with other people modified CBL shows 20.6% wait decrease and 45% energy usage . The proposed design is simulated in Xilinx with 12.5 MHz waveforms with autumn and increase time of 5 ns. Figure 6(a) & 6(b) shows the contrast of numerous carry choose adders in graphical as a type of the dining table 2. The graph shows the proposed system creates energy that is minimal, wait and area as in contrast to regular [2] and modified CSLA BEC that is using and CBL [40]

The 3 2- bit CSLA is performed by cascading two 16-bit CSLA and 64-bit CSLA is performed by cascading two CSLA that is 32-bit[41][42].

## VI. SUMMARY

The approach proposed in this paper to reduce quantity of transistors, energy and wait use of square root CSLA architecture. The quantity that is paid down of in this design provides maximum reduced amount of transistors and wait. Regular CSLA utilizes two RCA phases for carry in logic '0 and '1' which shows more energy consumption and delay with a high transistor count, it occupies more area that is chip. The square that is modified CSLA decreases transistor count, wait and energy usage by in comparison to change CSLA u sing BEC and CBL with boost in wait by usage of 12-T XOR gate and Binary to Excess-1 converter. This paper proposes a technique which decreases total amount of transistors in gates, area, wait and energy usage than regular, modified square root CSLA utilizing BEC and CBL by way of 3-T XOR gate and Common Boolean logic simplification. It might b age interesting to create of proposed square that is 128-bit CSLA with 3 -T XOR gate and Common Boolean logic simplification.

#### **REFERENCES**

- KumaraveA., Rangarajan K., Algorithm for automaton specification for exploring dynamic labyrinths ,Indian Journal of Science and Technology, V-6,I-SUPPL5,PP-4554-4559,Y-2013

- [2] P. Kavitha, S. Prabakaran "A Novel Hybrid Segmentation Method with Particle Swarm Optimization and Fuzzy C-Mean Based On Partitioning the Image for Detecting Lung Cancer" International Journal of Engineering and Advanced Technology (IJEAT) ISSN: 2249-8958, Volume-8 Issue-5, June 2019

- [3] Kumaravel A., Meetei O.N., An application of non-uniform cellular automata for efficient cryptography, 2013 IEEE Conference on Information and Communication Technologies, ICT 2013, V-, I-, PP-1200-1205, Y-2013

- [4] Kumarave A., Rangarajan K.,Routing alogrithm over semi-regular tessellations,2013 IEEE

Conference on Information and Communication Technologies, ICT

- 2013,V-,I-,PP-1180-1184,Y-2013

- [5] P. Kavitha, S. Prabakaran "Designing a Feature Vector for Statistical Texture Analysis of Brain Tumor" International Journal of Engineering and Advanced Technology (IJEAT) ISSN: 2249-8958, Volume-8 Issue-5, June 2019

- [6] Dutta P., Kumaravel A., A novel approach to trust based identification of leaders in social networks, Indian Journal of Science and Technology, V-9, I-10, PP--, Y-2016

- [7] Kumaravel A., Dutta P., Application of Pca for context selection for collaborative filtering, Middle - East Journal of Scientific Research, V-20, I-1, PP-88-93, Y-2014

- [8] KumaravelA., Rangarajan K., Constructing an automaton for exploring dynamic labyrinths, 2012 International Conference on Radar, Communication and Computing, ICRCC 2012, V-, I-, PP-161-165, Y-2012

- [9] P. Kavitha, S. Prabakaran "Adaptive Bilateral Filter for Multi-Resolution in Brain Tumor Recognition" International Journal of Innovative Technology and Exploring Engineering (IJITEE) ISSN: 2278-3075, Volume-8 Issue-8 June. 2019

- [10] Kumaravel A., Comparison of two multi-classification approaches for detecting network attacks, World Applied Sciences Journal, V-27, I-11, PP-1461-1465, Y-2013

- [11] Tariq J., Kumaravel A., Construction of cellular automata over hexagonal and triangular tessellations for path planning of multi-robots, 2016 IEEE International Conference on Computational Intelligence and Computing Research, ICCIC 2016, V-, I-, PP--, Y-2017

- [12] Sudha M., Kumaravel A., Analysis and measurement of wave guides using poisson method, Indonesian Journal of Electrical Engineering and Computer Science, V-8, I-2, PP-546-548, Y-2017

- [13] Ayyappan G., Nalini C., Kumaravel A., Various approaches of knowledge transfer in academic social network ,International Journal of Engineering and Technology, V-,I-,PP-2791-2794, Y-2017

- [14] Kaliyamurthie, K.P., Sivaraman, K., Ramesh, S.Imposing patient data privacy in wireless medical sensor networks through homomorphic cryptosystems 2016, Journal of Chemical and Pharmaceutical Sciences

- [15] Kaliyamurthie, K.P., Balasubramanian, P.C. An approach to multi secure to historical malformed documents using integer ripple transfiguration 2016Journal of Chemical and Pharmaceutical Science92.

- [16] A .Sangeetha, C.Nalini, "Semantic Ranking based on keywords extractions in the web", International Journal of Engineering & Technology, 7 (2.6) (2018) 290-292

- [17] S.V.GayathiriDevi, C.Nalini, N.Kumar, "An efficient software verification using multi-layered software verification tool "International Journal of Engineering & Technology, 7(2.21)2018 454-457

- [8] C.Nalini, Shwtambari Kharabe, "A Comparative Study On Different Techniques Used For Finger – Vein Authentication", International Journal Of Pure And Applied Mathematics, Volume 116 No. 8 2017, 327-333, Issn: 1314-3395

- [19] M.S. Vivekanandan and Dr. C. Rajabhushanam, "Enabling Privacy Protection and Content Assurance in Geo-Social Networks", International Journal of Innovative Research in Management, Engineering and Technology, Vol 3, Issue 4, pp. 49-55, April 2018.

- [20.] Rajabhushanam, V. Karthik, and G. Vivek, "Elasticity in Cloud Computing", International Journal of Innovative Research in Management, Engineering and Technology, Vol 3, Issue 4, pp. 104-111, April 2018.

- [21] Rangaswamy . Rajabhushanam c, "CCN-Based Congestion Control Mechanism In Dynamic Networks", International Journal of Innovative Research in Management, Engineering and Technology, Vol 3, Issue 4, pp. 117-119, April 2018.

- [22] Kavitha, R., Nedunchelian, R., "Domain-specific Search engine optimization using healthcare ontology and a neural network backpropagation approach", 2017, Research Journal of Biotechnology, Special Issue 2:157-166

- [23] Kavitha, G., Kavitha, R., "An analysis to improve throughput of high-power hubs in mobile ad hoc network", 2016, Journal of Chemical and Pharmaceutical Sciences, Vol-9, Issue-2: 361-363

- [24] Kavitha, G., Kavitha, R., "Dipping interference to supplement throughput in MANET", 2016, Journal of Chemical and Pharmaceutical Sciences, Vol-9, Issue-2: 357-360

- [25] Michael, G., Chandrasekar, A.,"Leader election based malicious detection and response system in MANET using mechanism design approach", Journal of Chemical and Pharmaceutical Sciences(JCPS) Volume 9 Issue 2, April - June 2016.

- [26] Michael, G., Chandrasekar, A.,"Modeling of detection of camouflaging worm using epidemic dynamic model and power spectral density", Journal of Chemical and Pharmaceutical Sciences(JCPS) Volume 9 Issue 2, April - June 2016

- [27] Pothumani, S., Sriram, M., Sridhar, J., Arul Selvan, G., Secure mobile agents communication on intranet, Journal of Chemical and Pharmaceutical Sciences, volume 9, Issue 3, Pg No S32-S35, 2016

- [28] Pothumani, S., Sriram, M., Sridhar, Various schemes for database encryption-a survey, Journal of Chemical and Pharmaceutical Sciences, volume 9, Issue 3, Pg NoS103-S106, 2016

- [29] Pothumani, S., Sriram, M., Sridhar, A novel economic framework for cloud and grid computing, Journal of Chemical and Pharmaceutical Sciences, volume 9, Issue 3, Pg No S29-S31, 2016

- [30] Priya, N., Sridhar, J., Sriram, M. "Ecommerce Transaction Security Challenges and Prevention Methods- New Approach" 2016, Journal of Chemical and Pharmaceutical Sciences, JCPS Volume 9 Issue 3.page no:S66-S68.

- [31] Priya, N.,Sridhar,J.,Sriram, M."Vehicular cloud computing security issues and solutions" Journal of Chemical and Pharmaceutical Sciences(JCPS) Volume 9 Issue 2, April - June 2016

- [32] Priya, N., Sridhar, J., Sriram, M. "Mobile large data storage security in cloud computing environment-a new approach" JCPS Volume 9 Issue 2. April - June 2016

- [33] Anuradha.C, Khanna.V, "Improving network performance and security in WSN using decentralized hypothesis testing "Journal of Chemical and Pharmaceutical Sciences(JCPS) Volume 9 Issue 2, April - June 2016.

- [34] Anuradha C, Khanna V, "A novel gsm based control for e-devices" Journal of Chemical and Pharmaceutical Sciences (JCPS) Volume 9 Issue 2, April - June 2016.

- [35] Anuradha C, Khanna V, "Secured privacy preserving sharing and data integration in mobile web environments" Journal of Chemical and Pharmaceutical Sciences (JCPS) Volume 9 Issue 2, April - June 2016.

- [36]Sundarraj, B., Kaliyamurthie, K.P.Social network analysis for decisive the ultimate classification from the ensemble to boost accuracy rates 2016 International Journal of Pharmacy and Technology83.

- [37]Sundarraj, B., Kaliyamurthie, K.P.A content-based spam filtering approach victimisation artificial neural networks 2016 International Journal of Pharmacy and Technology83.

- [38]Sundarraj,B.,Kaliyamurthie,K.P. Remote sensing imaging for satellite image segmentation 2016 International Journal of Pharmacy and Technolog 83.

- [39]Sivaraman, K., Senthil, M.Intuitive driver proxy control using artificial intelligenc2016 International Journal of Pharmacy and Technology 84.

- [40]Sivaraman, K., Kaliyamurthie, K.P Cloud computing in mobile technology 2016 Journal of Chemical and Pharmaceutical Sciences 92.

- [41] Sivaraman, K., Khanna, V. Implementation of an extension for browser to detect vulnerable elements on web pages and avoid click jacking 2016 Journal of Chemical and Pharmaceutical Science 92...

#### **AUTHORS PROFILE**

**Dr. R.Kavitha**, Associate Professor, Department of Computer Science & Engineering, Bharath Institute of Higher Education and Research, Chennai, India

**G.Kavitha** Assistant Professor, Department of Computer Science & Engineering, Bharath Institute of Higher Education and Research, Chennai, India

**C.Anuradha** Assistant Professor, Department of Computer Science & Engineering, Bharath Institute of Higher Education and Research, Chennai, India

N.Priya, Assistant Professor, Department of Computer Science & Engineering, Bharath Institute of Higher Education and Research, Chennai, India