# A Procedure For Avoid Overrun Error in Universal Synchronous Asynchronous Receiver Transmitter (Usart) by Utilizing Dummy Join and Interrupt Latency Method

S. Sangeetha, S.R. Srividhya, K. Anita Davamani, S. Amudha

ABSTRACT:In parallel interaction quantity of line between receiver and transmitter is dependent upon range bits to be sent, to transmit one byte 8 lines are needed b etween transmitter and receiver which raise the expense. Nevertheless as a result of overlapping between lines cross talk will take place, to conquer this blem that is professional interaction US ART is employed. US ART is a computer device that is competent to transform parallel to serial during the transmitter serial and end to parallel during the receiver age nd. Nonetheless US ART suffer from overrun mistake, parity mistake and mistake that is framing blem. In this paper author has professional t that is posed m ethods in other words dummy register and interrupt latency through which we can avoidoverrun mistake in United States ART.

### I. INTRODUCTION

Most for the microprocess or based systems are designed for parallel data transfer, because that's the test that is fast to accomplish it. In parallel co that is 1 quantity of lines needed to transfer data depends upon quantity of bits to be transferred in other words. to transfer 1 byte of information 8 lines are expected from trans mitter and receiver, nevertheless to trans fer information over long distance parallel data trans mis s ion requires a lot of cables that is e xpensive and its particular difficult to keep up.[1, 2, 3].

Then its contributes to get across talk if two line overlap for each other. Where as , in s co that is erialization

information can be trans ferred over a long distance between two systems as it reduces distortion of signals . Consequently, information become s ent for very long distances is converted from parallel kind to serial typeso it could be s ent on a s cable [1] that is ingle. Se rial information gotten from disthat is very long is converted to parallel form s o that it can easily be trans ferred on the microcomputer buses .

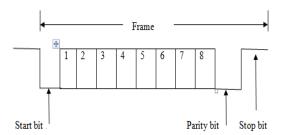

Serial information can be s s which are ently or as ynchronously us ing a device called United States Of America RT (univers al s ynchronous as ynchronous receiver trans mitter) [4,5,6]. It has built in baud price generator also it permits duple that is full trans mis s ion and reception [7, 8]. In a synchronous communication there is different clock between trans mitter and receiver to make s ynchronization between trans mitter and receiver we make use of start bit and s bit that is top. In asynchronous information trans fer, data is trans mitted with regards to figures. The co mbination of s bit that is tart character and s top bit is called fra me personally. Various s ystemsuses s which are various bits such as 1, 1.5 and 2. The s tart and stop bit carry no informat ion, but are needed age that is becaus of ynchronous nature of data [9, 10]. He re s bit that is tart us ed to point the receiver in regards to the start of the framework whereas end bits are us edto point the finish for the frame [11, 12].

Figure 1: Frame format

### Revised Manuscript Received on April, 2019.

**S.Sangeetha,** Department of CSE, Bharath Institute of Higher Education and Research, Chennai, Tamilnadu, India.

S.R.Sri Vidhya, Department of CSE, Bharath Institute of Higher Education and Research, Chennai, Tamilnadu, India.

K. Anita Davamani, Department of CSE, Bharath Institute of Higher Education and Research, Chennai, Tamilnadu, India.

**S. Amudha,** Department of CSE, Bharath Institute of Higher Education and Research, Chennai, Tamilnadu, India.

## II. EXISTING METHOD TO SEND AND RECEIVE CHARACTER IN USART

USART cons is t of two buffer registers s uch as trans mitter SBUF and r SBUF that is accept. Information is s tored in trans mitter SBUF register and parity bit is s tored in TB8 of SCON res is ter after which data is trans mitted and then Trans mitter interrupt (T I) is s et in SCON, its programmer or us er res pons ibility to clear TI to trans mit character that is next [13, 14]. To understand just how figures which are numerous been s ent a counter could be used [15, 16]. The trans mitter shall s tay low until another character is preparing to be read. Receiver will recognize valid s bit that is tart then receiver dis card s tart bit and information is s tore in receiver SBUF register and parity bit is s tore in RB8 and then Receiver Interrupt (RI) is s et in SCON to point information is gotten, its programmer or us er res pons ibility to clear RI to receiver ne xt character [17, 18].

#### III. CASE RESEARCH

By the because s essment of s everal res earch papers associated work many authors had attempted to overcome this mistake that is overrun various trend and also have suggested a couple of practices. Central Processing Unit s hould be run at a ma ximu m pos s iblespeed, to speed the execution up of USART interrupt. We can avoid the mistake that is inundated due t o interrupt latencies by reducing the baud price of USART [19, 20]. We are able to over come this mistake by maintaining the USART ISR (Interrupt s ervice routine) efficient and as s hort as poss i that is ible. the full time taken fully to e xecute ISR must be les s compared to the time taken up to get ne xt data byte. A uthormade an attempt to overcome this overrun mistake by us ing a dummy register and interrupt latency technique by maintaining this in view [21]

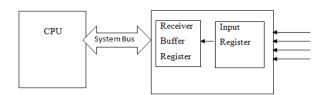

## IV. OVERRUN P ROB LEM IN UNITED STATES ART

In USART the receiver s ection cons is t of two register that is input regis receiver and ter buffer reg is ter. Input register gets information in s form that is erial convert it in synchronous type and production is s tored in receiver buffer [22, 23] Central Processing Unit is s u pposed to learn this character before next character is gotten, but then next gotten character replaces the earlier one when Central Processing Unit efforts to learn character it checks out s econd character ins tead of reading firs tcharacter this will be called over run mistake if Central Processing Unit does not see the character [24, 25]

## V. P RO POS ED METHO D T O AVO ID O VERRUN ERROR IN USART

Figure 2: Receiver s ection in United States Of America

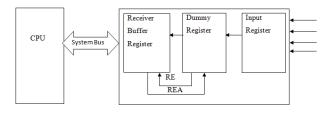

A strategy to avoid overrun mistake proble m which want to increase the general efficiency in s erialcommunication in this paper author made an effort to propos e. The figure s hownbelow illustratesmodificat ion to main-stream USARTreceiver s ection. Input register s tore s erial information and convert it in to parallel then this synchronous information is s tored in dummy register, then your dummy reg is ter creates a c ontrol s in other words that is ignal. Receiver bufferreg is ter Empty (RE) to check always whether Receiver buffe r register is empty. Then its generate acknowledge (REA) to inform t hat its empty and able to accept information, then dummy register s end information in to receiver buffe r register [26, 27] if Receiver buffer register is empty. If receiver buffer register is full in other words. Central Processing Unit d id maybe not look over information from receiver buffer register and suggest while brand new information comes then input register converts it into synchronous and then data is s tore in dummy regis ter. Now du regis that is mmy check whether receiver buffer is empty, however now dummy register doesn't any acknowledge because receiver buffer register is complete then brand new information is s tored in dummy register in the place of over writ ing it in receiver buffer register [28, 29, 30]. Now whenever Central Processing Unit make an effort to read information [31, 32] it checks out information from enjoy r buffer reg is ter and immediately it REA that is generate ignal to just accept brand new information that is s tored in dummy register [33, 34]

Figure 3: Proposed Receiver section in United States Of America RT

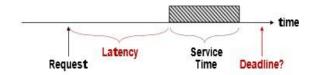

Information can be sent and browse from several products on an bas that is interrupt or on a polled bas is . In polling technique the procedure or constantly test whether it needs attention the devices to understand. It really is an method that is ineffective processor time is was tedo nunnecessary polls [35, 36]. In contrast an interrupt is absolutely nothing but disruption to CPU whichcauses Micro procedure or even to utilize diffe lease task and later come back to its tas which are past. Interrupt Latency means enough time distinction between getting reques which can be interrupt from interrupt source and serviceoffered to it. [37, 38]. Throughput and interrupt latency have actually invers connection that is age is throughput associated with microprocessorincreases by reducing interrupt latency. In

## International Journal of Innovative Technology and Exploring Engineering (IJITEE) ISSN: 2278-3075, Volume-8, Issue-9S3, July 2019

this paper author made an effort in order to avoid mistake that is overrun ing interrupt latency [39, 40]. If Central Processing Unit g ives high priority to USART interrupt i.e CPU reduces United States Of America RT interrupt time that is latency. Consequently CPU reads character fasterfro mreceiver bufferreg is ter prior to the character that is brand new [41].

Figure 4: Interrupt Latency in order to avoid mistake that is inundated

### VII. CONCLUSION

In this paper writer propos ed t wo different techniques that dummy register and interrupt latency to prevent overrun mistake in Univers al Synchronous As ynchronous Receiver Trans mitter (United States Of America RT), we could improve the effectiveness of gotten information by using this method.

### REFERENCES

- Kumarave A., Rangarajan K., Algorithm for automaton specification for exploring dynamic labyrinths, Indian Journal of Science and Technology, V-6, I-SUPPL5, PP-4554-4559, Y-2013

- P. Kavitha, S. Prabakaran "A Novel Hybrid Segmentation Method with Particle Swarm Optimization and Fuzzy C-Mean Based On Partitioning the Image for Detecting Lung Cancer" International Journal of Engineering and Advanced Technology (IJEAT) ISSN: 2249-8958, Volume-8 Issue-5, June 2019

- Kumaravel A., Meetei O.N., An application of non-uniform cellular automata for efficient cryptography, 2013 IEEE Conference on Information and Communication Technologies, ICT 2013, V-,I-,PP-1200-1205, Y-2013

- Kumarave A., Rangarajan K.,Routing alogrithm over semi-regular tessellations,2013 IEEE Conference on Information and Communication Technologies, ICT 2013,V-,I-,PP-1180-1184,Y-2013

- P. Kavitha, S. Prabakaran "Designing a Feature Vector for Statistical Texture Analysis of Brain Tumor" International Journal of Engineering and Advanced Technology (IJEAT) ISSN: 2249-8958, Volume-8 Issue-5, June 2019

- Dutta P., Kumaravel A., A novel approach to trust based identification of leaders in social networks, Indian Journal of Science and Technology, V-9, I-10, PP--, Y-2016

- Kumaravel A., Dutta P., Application of Pca for context selection for collaborative filtering, Middle - East Journal of Scientific Research, V-20, I-1, PP-88-93, Y-2014

- Kumaravel A., Rangarajan K., Constructing an automaton for exploring dynamic labyrinths, 2012 International Conference on Radar, Communication and Computing, ICRCC 2012, V-, I-, PP-161-165, Y-2012

- P. Kavitha, S. Prabakaran "Adaptive Bilateral Filter for Multi-Resolution in Brain Tumor Recognition" International Journal of Innovative Technology and Exploring Engineering (IJITEE) ISSN: 2278-3075, Volume-8 Issue-8 June, 2019

- Kumaravel A., Comparison of two multi-classification approaches for detecting network attacks, World Applied Sciences Journal, V-27, I-11, PP-1461-1465, Y-2013

- Tariq J., Kumaravel A., Construction of cellular automata over hexagonal and triangular tessellations for path planning of multirobots, 2016 IEEE International Conference on Computational Intelligence and Computing Research, ICCIC 2016, V-,I-,PP--,Y-2017

- Sudha M., Kumaravel A., Analysis and measurement of wave guides using poisson method, Indonesian Journal of Electrical Engineering and Computer Science, V-8, I-2, PP-546-548, Y-2017

- Ayyappan G., Nalini C., Kumaravel A., Various approaches of knowledge transfer in academic social network, International Journal of Engineering and Technology, V-,I-,PP-2791-2794, Y-2017

- 14. Kaliyamurthie, K.P., Sivaraman, K., Ramesh, S. Imposing patient data privacy in wireless medical sensor networks through homomorphic cryptosystems 2016, Journal of Chemical and Pharmaceutical Sciences 9 2.

- Kaliyamurthie, K.P., Balasubramanian, P.C. An approach to multi secure to historical malformed documents using integer ripple transfiguration 2016 Journal of Chemical and Pharmaceutical Sciences 9 2.

- A.Sangeetha, C.Nalini, "Semantic Ranking based on keywords extractions in the web", International Journal of Engineering & Technology, 7 (2.6) (2018) 290-292

- S.V.GayathiriDevi, C.Nalini, N.Kumar, "An efficient software verification using multi-layered software verification tool "International Journal of Engineering & Technology, 7(2.21)2018 454-457

- C.Nalini, Shwtambari Kharabe, "A Comparative Study On Different Techniques Used For Finger – Vein Authentication", International Journal Of Pure And Applied Mathematics, Volume 116 No. 8 2017, 327-333, Issn: 1314-3395

- M.S. Vivekanandan and Dr. C. Rajabhushanam, "Enabling Privacy Protection and Content Assurance in Geo-Social Networks", International Journal of Innovative Research in Management, Engineering and Technology, Vol 3, Issue 4, pp. 49-55, April

- Dr. C. Rajabhushanam, V. Karthik, and G. Vivek, "Elasticity in Cloud Computing", International Journal of Innovative Research in Management, Engineering and Technology, Vol 3, Issue 4, pp. 104-111, April 2018.

- K. Rangaswamy and Dr. C. Rajabhushanamc, "CCN-Based Congestion Control Mechanism In Dynamic Networks", International Journal of Innovative Research in Management, Engineering and Technology, Vol 3, Issue 4, pp. 117-119, April 2018

- Kavitha, R., Nedunchelian, R., "Domain-specific Search engine optimization using healthcare ontology and a neural network backpropagation approach", 2017, Research Journal of Biotechnology, Special Issue 2:157-166

- Kavitha, G., Kavitha, R., "An analysis to improve throughput of high-power hubs in mobile ad hoc network", 2016, Journal of Chemical and Pharmaceutical Sciences, Vol-9, Issue-2: 361-363

- Kavitha, G., Kavitha, R., "Dipping interference to supplement throughput in MANET", 2016, Journal of Chemical and Pharmaceutical Sciences, Vol-9, Issue-2: 357-360

- Michael, G., Chandrasekar, A.,"Leader election based malicious detection and response system in MANET using mechanism design approach", Journal of Chemical and Pharmaceutical Sciences(JCPS) Volume 9 Issue 2, April - June 2016.

- Michael, G., Chandrasekar, A.,"Modeling of detection of camouflaging worm using epidemic dynamic model and power spectral density", Journal of Chemical and Pharmaceutical Sciences(JCPS) Volume 9 Issue 2, April - June 2016.

- Pothumani, S., Sriram, M., Sridhar, J., Arul Selvan, G., Secure mobile agents communication on intranet, Journal of Chemical and Pharmaceutical Sciences, volume 9, Issue 3, Pg No S32-S35, 2016

- Pothumani, S., Sriram, M., Sridhar, Various schemes for database encryption-a survey, Journal of Chemical and Pharmaceutical Sciences, volume 9, Issue 3, Pg NoS103-S106, 2016

- Pothumani, S., Sriram, M., Sridhar, A novel economic framework for cloud and grid computing, Journal of Chemical and Pharmaceutical Sciences, volume 9, Issue 3, Pg No S29-S31, 2016

- Priya, N., Sridhar, J., Sriram, M. "Ecommerce Transaction Security Challenges and Prevention Methods- New Approach" 2016 ,Journal of Chemical and Pharmaceutical Sciences, JCPS

### A Procedure For Avoid Overrun Error In Universal Synchronous Asynchronous Receiver Transmitter (Usart) By Utilizing Dummy Join And Interrupt Latency Method

- Volume 9 Issue 3.page no:S66-S68.

- Priya, N.,Sridhar, J.,Sriram, M."Vehicular cloud computing security issues and solutions" Journal of Chemical and Pharmaceutical Sciences(JCPS) Volume 9 Issue 2, April - June 2016.

- Priya, N., Sridhar, J., Sriram, M. "Mobile large data storage security in cloud computing environment-a new approach" JCPS Volume 9 Issue 2. April June 2016

Anuradha.C, Khanna.V, "Improving network performance and

- Anuradha.C, Khanna.V, "Improving network performance and security in WSN using decentralized hypothesis testing "Journal of Chemical and Pharmaceutical Sciences(JCPS) Volume 9 Issue 2, April - June 2016.

- Anuradha.C, Khanna.V, "A novel gsm based control for e-devices" Journal of Chemical and Pharmaceutical Sciences(JCPS) Volume 9 Issue 2, April - June 2016.

- Anuradha.C, Khanna.V, "Secured privacy preserving sharing and data integration in mobile web environments" Journal of Chemical and Pharmaceutical Sciences(JCPS) Volume 9 Issue 2, April - June 2016

- Sundarraj, B., Kaliyamurthie, K.P. Social network analysis for decisive the ultimate classification from the ensemble to boost accuracy rates 2016 International Journal of Pharmacy and Technology 8

- Sundarraj, B., Kaliyamurthie, K.P. A content-based spam filtering approach victimisation artificial neural networks 2016

International Journal of Pharmacy and Technology 8 3.

- Sundarraj, B., Kaliyamurthie, K.P. Remote sensing imaging for satellite image segmentation 2016 International Journal of Pharmacy and Technology 8 3.

- Sivaraman, K., Senthil, M. Intuitive driver proxy control using artificial intelligence and Technology

2016 International Journal of Pharmacy 4.

- Sivaraman, K., Kaliyamurthie, K.P. Cloud computing in mobile technology 2016 Journal of Chemical and Pharmaceutical Sciences 9 2.

- Sivaraman, K., Khanna, V.Implementation of an extension for browser to detect vulnerable elements on web pages and avoid click jacking 2016 Journal of Chemical and Pharmaceutical Sciences 9 2.

### **AUTHORS PROFILE**

**S.R.Srividhya** Assistant Professor, Department of Computer Science & Engineering, Bharath Institute of Higher Education and Research, Chennai, India

**S.Sangeetha**, Assistant Professor, Department of Computer Science & Engineering, Bharath Institute of Higher Education and Research, Chennai, India

K. Anitha Davamani, Assistant Professor, Department of Computer Science & Engineering, Bharath Institute of Higher Education and Research, Chennai, India

**S.Amudha,** Assistant Professor, Department of Computer Science & Engineering, Bharath Institute of Higher Education and Research, Chennai, India