# Himabindu Veldurthi, S.Saraswathi, T.Anil Kumar

Abstract: In this archive, the H-bridge hybrid modular converter (HBHMC) with fluffy rationale controller for Grid applications is proposed. HBHMC work modes, FBSM voltage balance adjustment procedure and HBHMC-based HVDC framework control for arrange application. It utilizes a waveform circuit (WSC) comprising of full scaffold submodules (FBSM) at yield of main H bridge converter (MHBC). A nitty gritty examination is made among HBHMC and other half and half procedures dependent on the quantity of switches and capacitors among PI and the diffuse controller. The activity of the HVDC framework dependent on HBHMC for adjusted and lopsided three-stage system conditions. This article shows the similar investigation among PI and the FUZZY controller. This archive was actualized in MATLAB/SIMULATOR.

Keywords:- H-bridge hybrid modular converter (HBHMC), HVDC, matrix, secluded staggered converter, MATLAB programming.

# I. INTRODUCTION

The measured staggered converter is set to wind up one of the important supported strategy for HVDC systems reliant on VSC [1] - [4]. This is on a very basic level as a result of its central focuses, for instance, estimated quality, adaptability, low conduction adversities, low symphonious filtering need and low dv/dt, it allows the transformer with low separation. In any case, the MMC has imperatives, for instance, the essential for a colossal number of capacitors and devices an the incomprehensibility of blocking/limiting the weakness current if there ought to be an event of DC side defect and the proximity of streams gushing in each branch. of the MMC without using a DC electrical switch [5] - [10]. Stream current altogether influences the evaluations of converter parts, capacitor voltage waves, and influence disasters. A control of the stream current is imperative to diminish these impacts of system [11]-[13].

Revised Manuscript Received on November 30, 2019.

\* Correspondence Author

**Himabindu Veldurthi\***, Department of Electrical and Electronics Engineering, Anurag Group of Institution ,Email:himabindulaxmi5@gmail.com

**S.Saraswathi**, Department of Electrical and Electronics Engineering, Anurag Group of Institution Email: saraswathieee@cvsr.ac.in

**Dr.T.Anil Kumar,** Electrical and Electronics Engineering, Anurag Group of Institution. Email: Thalluruanil@gmail.com

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license <a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>

Moreover, when a DC insufficiency happens, a high flaw current streams in feedback diodes related between each IGBT of the MMC [5]. there are some ways to deal with oversee managing this issue is to utilize a DC electrical switch beginning late proposed In the following thought, rather than HBSM, another SM being able to pass on the inverse uttermost point voltage is utilized, which squares/limits the importance of the issue stream if there should be an occasion of a DC side imperfection. In the third thought, the converter has changed the arrangement itself and utilizing the FBSM, the constrainment of the defect current is come to. This get-together of converters is called HMC. HMC consoles are for the most part made out of two fragments, a DS and a WSC. The DS switches are un mitigated related in strategy and the WSC is surrounded by interfacing FBSM stacks in game-plan.

Among the HMC supports, the HCM reassure has a DC acclimation to internal dissatisfaction limit, a decreased number of MSs in the WSCs and a fourth of the measure of MS capacitors stood apart from that of the MMCs, understanding an impression diminished and lower hardships. Notwithstanding, it shows higher episodes in DS because of badly arranged exchanging and requires low sales consonant channels to direct low vitality beat because of poor DS and WSC synchronization. Likewise, to change capacitor SM voltages, either a more prominent number of MSs or DSs should be exchanged at a higher rehash, acknowledging higher hardships. The AAMMC, proposed in, has highlights, for example, DC acclimation to non-fundamental frustration limit, a gigantic piece of the measure of SM messages stood apart from the MMC comfort, and lower hardships. Parallel connection MMC is another technic of HVDC applications considering the decreased number of segments and DS programming exchanging.

# II. H-BRIDGE HYBRID MODULAR CONVERTER

### A. Single-Phase System

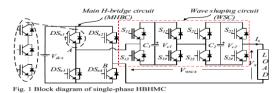

The HBHMC of a single arrangement appears in Fig. 1. Like the different HMCs discussed above, this converter also has rule of two parts, an MHBC and a WSC. The MHBC contains four switches (DSx1-DSx4), which are the strategic relationship of semiconductor changes that are absolutely controllable to support a high-voltage dc-partner orchestration (Vdcx). These switches are worked in the rehash key. MHBC switches direct current to the positive DC terminal, the negative DC terminal,

or rotate freely through DSx1 and DSx2 or through DSx3 and DSx4. To make a sinusoidal performance voltage over the heap, the WSC is used with MHBC performance. The WSC is an FBSM game plan relationship and these are exchanged at a higher repetition. The MHBC performance voltage conditions can be + Vdcx, 0 or - Vdcx as combined in Table I. For ease of reference, only two related FBSMs are seen in the MHBC game plan as it appeared in Fig. 1. In the event that the voltage of each FBSM capacitor makes sense of how Vdcx / 2, five levels of performance voltage (Vx) can be obtained (+ Vdcx, + Vdcx / 2, 0, - Vdcx / 2 and - Vdcx)

TABLE I SWITHING STATES OF MHBC IN HBHMC

| $DS_{xI}$ | $DS_{x2}$ | $DS_{x3}$ | $DS_{x4}$ | MHBC output voltage |

|-----------|-----------|-----------|-----------|---------------------|

| 1         | 0         | 0         | 1         | $+V_{dcx}$          |

| 0         | 1         | 1         | 0         | -V <sub>dex</sub>   |

| 0         | 0         | 1         | 1         | 0                   |

| 1         | 1         | 0         | 0         | 0                   |

### **B.** Three-Phase System

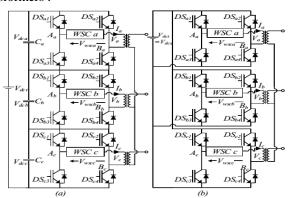

To acquire the three-step frame, three HBHMC cards (Fig. 1) can be connected as a model (HBHMC game plan) or parallel (HBHMC parallel). (Figures 2 (an) and (b)). The three MHCBs of the three-component converter work on key repetition with performances displaced in time by 120 ° relative to each other. For the HBH TM strategy, three DC capacitors are required to divide the pre-eminent DC interface voltage (Vdct) in a similar manner, the goal being that 3Vdcx = Vdct (Figure 2 (a)). For the HBH TM plane, the MHBC yields are 0,+ Vdct / 3, - Vdct / 3, and for the parallel HBHMC, the yields are + Vdct, 0 or - Vdct (Figures 2 (year) and 2 (b)). For an N number of FBSM bound to the WSC arrangement stage, the capacitor voltage of the HBHMC plane of each SM is managed in Vdct / 3N and in HBHMC mode in parallel, it is monitored in Vdct / N. These transformers.

Fig. 2 (a) Illustration of a half-composite and half-isolated converter for the three-plane H-interface scheme (HBHMC procedure), (b) representation of an explicit parallel-parallel converter H parallel to three orchestras (parallel-HBHMC).

### C. Modes of Operation

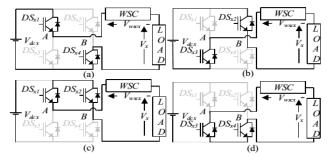

The average steadfast state HBHMC action can be grouped into two modes operation depending upon the MHBC states. 1)Powering Mode:

In this mode of operation, the MHBC execution is a square wave and the WSC is dependable to get the dazed presentation voltage waveform of the HBHMC execution. This mode is known as the control mode since the centrality is traded between the CC affiliation and the structure of the constrained air framework. In this mode, DSx1 is empowered for the +ve half cycle of the deceleration voltage and DSx2 is debilitated, and for the -ve half cycle, DSx1 is impaired and DSx2 is empowered. Here, x locations arrange a, b or c. In this mode, the presentation voltage of the stage converter x (Vx) relies upon the voltage related with the immediate current by association (Vdcx) and the voltage over the terminals of the WSC (Vwscx). For the HBHMC course of action, Vdcx = Vdct/3 and for Parallel-HBHMC, Vdcx = Vdct. The proportionate circuit outlines for the +ve and -ve half-cycles of the charging mode are represented in FIGS. 3 (an) and (b) independently. Figs 1 and 3, Vx and Vwscx for N FBSM in the CSM are transmitted as pursues

$$V_x = (DS_{x1} - Ds_{x2})V_{dex} - V_{wsex}....(1)$$

$$V_{wscx} = \sum_{j=1}^{N} (S_{j1} - S_{j2}) * V_{cj} \dots (2)$$

where DSx1 and DSx2 are the exchange conditions of the upper MHBC switches of the stages x, Sj1 and Sj2 are the exchange conditions of the jBSF WSC and Vcj is the voltage of the jth FBSM capacitor in the WSCs of the x phase of HBHMC. The MHBC DSx1 switches are corresponding to DSx3 and DSx2 is connected to DSx4. As a result, Sj1 is essential for Sj3 and Sj2 is connected to Sj4 in the FBSM. For a number N of FBSM in the WSC, if the capacitor voltage of each SM (Vcj) is Vdcx / N and subsequently depends on the switch expressed, the FBSM execution voltage is + Vdcx / N (coordinate decisively), - Vdcx / N (on the contrary introduced) or zero (maintained a strategic distance from), as in MHBC.

# 2) Isolation Mode:

In this mode, the DC voltage source escapes and the power current streams unreservedly in MHBC. Starting now and into the foreseeable future and soon, there is no vitality trade between the CC affiliation and the cooling structure. The proportional circuit lines for the division mode are outlined in FIGS. 3 (c) and (d). In this mode, it is the -ve of the voltage on the WSC (figures 3 (c) and (d)) and given by,

$$V_x = -V_{wscx} \dots (3)$$

Where Vwscx is the voltage crosswise over WSC.

Fig. 3circuit outlines of HBHMC for various strategies for development (a) +ve half cycle of controlling mode, (b) - ve half cycle of fueling mode, (c) and (d) withdrawal modes.

# III. CAPACITOR VOLTAGE EQUIPMENT IN **HBHMC**

For the development of the converter, it is basic that the total power retention by WSC be zero. Simultaneously, the capacitor voltages run of the mill of each WSC sm must stay indistinguishable and unsurprising.

# A. WSC voltage balancing from HBHMC

It is normal that the quality of the output voltage of the converter is quite incredible and that the negotiation effects of the converter are neglected. The converter organizes the voltage output x (Vx) can be transported as,

$$V_x(t) = V_m \sin(wt + \varphi_1) \dots \dots \dots \dots (4)$$

where Vm is the abundance of the stage voltage, ω the negative repetition, 1 is equal to 0,  $2\pi/3$ ,  $-2\pi/3$  for steps a, b and c exclusively. It is believed that the output current of the phase x of the converter is sinusoidal with the abundance of current Im and with a safe threshold movement of 2 and is reported as follows

$$I_x(t) = I_m \sin(wt + \varphi_1 - \varphi_2) \dots \dots \dots \dots (5)$$

The adjustment list mi of the HBHMC can be communicated

$$mi = \frac{v_m}{v_{dex}} \dots \dots \dots (6)$$

The fast power that passes through the CSM in step x can be indicated as follows:

$$P_{\text{wscx}}(t) = V_{\text{wscx}}(t)I_{x}(t)....(7)$$

# 1) Powering Mode:

In (1) and (4), the WSC voltage of stage x to control the activity method is indicated as follows:

$$V_{wscx}(t) = S_x V_{dcx} - V_m \sin(wt + \varphi_1)....(8)$$

where Sx is 1 when DSx1 is enabled and DSx2 is off and is -1 when DSx1 is disabled and DSx2 is enabled. By substituting the estimates Ix and Vwscx of (5) and (8) in (7), the fast power of step x of the WSC is solved as follows

$$P_{wscx}(t) = (S_x V_{dcx} - V_m \sin(wt + \varphi_1)) I_m \sin(wt + \varphi_1 - \varphi_2)$$

$$P_{wscx}(t) = V_m I_m \begin{pmatrix} \frac{S_x}{mi} \sin((wt + \varphi_1 - \varphi_2)) \\ +\frac{1}{2}(\cos(2wt + 2\varphi_1 - \varphi_2) - \cos\varphi_2) \end{pmatrix}$$

...(10)

more than one main product cycle with the declaration of the essential exchange between the WSC server and the stack (Wwscx).

$$W_{wscx} = \int_{-\varphi_{1}/_{W}}^{2\pi-\varphi_{1}/_{W}} P_{wscx}(t) dx$$

$$W_{wscx} = \frac{V_m I_m \cos(\varphi_2)}{w} \left[ \frac{4}{mi} - \pi \right] \dots (11)$$

It is clear from (11) that the essential character exchanged by the CSM is exactly zero where =  $4/\pi$ . For values other than 4  $/\pi$ , the volume exchanged by the WSC is positive or negative, causing an increase or decrease in the WSC capacitor voltage only. The WSC (Digital Policy Law). 4 /  $\pi$ , the action restriction strategy is shown.

### 2) Isolation Mode:

In mode, the WSC capacitors of (3) and (4), the transverse voltage at stage x WSC can be transmitted as follows

$$V_{wscx}(t) = -V_m \sin(wt + \varphi_1)...(12)$$

Substituting (5) and (12) in (7), the prompt intensity of stage x of the converter in confinement mode is determined as

$$P_{wscx} = (-V_m \sin(wt + \varphi_1))I_m \sin(wt + \varphi_1 - \varphi_2) \dots \dots \dots \dots (13)$$

$$P_{wscx}(t) = V_m I_m I_0^{-1} (\cos(2wt + 2\varphi_1 - \varphi_2 - \cos\varphi_2)) \dots \dots (14)$$

Consequently, the vitality traded by WSC more than one crucial cycle is determined as

$$W_{wscx} = \int_{-\varphi_1/w}^{2\pi-\varphi_1/w} P_{wscx}(t) dt = -\frac{\pi}{w} V_m I_m cos\varphi_2.....(15)$$

All things considered, clearly the basic traded by WSC can be constrained by the genuineness of the pipe and controls for 0  $\leq$  mi  $\leq$  4/ $\pi$ . To pick one of these two methods of activity without expanding the business reiteration of MHBC among the fundamental techniques, two philosophies (HCI and AZCI strategies) are proposed to alter the capacitor voltage. The undeniable delimitation of these two strategies is demonstrated as follows.

# a) Half Cycle Isolation Method:

As appeared in Figure 4 (a), the HCI mode choice compares to the standard SM capacitor voltage WSC (Vavg) SM. At each zero intersection inspiration driving the reference voltage (Vxref), this ordinary capacitor voltage is disengaged and the reference capacitor voltage (Vrefavg), which is transmitted to Vdcx/N. On the off chance that Vavg n 'This isn't not auto controlled, it's anything but a self-check, DX1 and DX4, DX2 and DX3, for the positive and negative cycles of the yield voltage, without obstructions. Obviously, in the event that you are a higher priority than Vrefavg, the MHBC switches empower the send mode (Dx1 and Dx2 or Dx3 and Dx4). The mode statement is made as delineated in FIG. 4 (a).  $P_{wscx}(t) = (S_x V_{dcx} - V_m \sin(wt + \varphi_1)) I_m \sin(wt + \varphi_1 - \varphi_2)$ . The Politage waveforms on various events become Figure 4

Fig. 4 HCI frame; (a) A square control panel to select the containment and control modes, and (b) HBHMC voltage waveforms at different times.

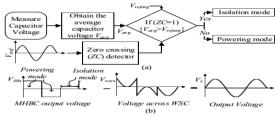

### b) Across Zero Crossing Isolation Method:

In this method, instead of maintaining the dynamic segregation mode during the whole part of the fundamental cycle, which builds the capacitor. A square control system that addresses this procedure appears in Figure 5 (a). In this method, to choose the period of time during which the suppression mode is dynamic, the capacitor voltage of the WSC mill (Vavg) and the reference voltage (Vrefavg) are separated.

This error is found in a PI controller, as shown in Figure 5 (a), and the performance of the PI controller (e) is separated and the performance voltage reference (Vxref) to verify the separation signals and that of the mode. The waveforms of the inverter's performance voltage at different times of the converter are illustrated in Figure 5 (b). The converter performance voltage (Vx) with reference to Fig. 1 is given by  $V_x = V_{ABx} - V_{WSCx}......(16)$

where VABx is the presentation voltage of MHBC. VABxis + Vdcx for half positive cycle and - Vdcx for half negative cycle. For the situation where the transverse voltage in the WSC is protected (permanently combined) in a positive and negative half-cycle (installed in a conflict) in the negative half-cycle, the exposure voltage will generally not be Vdcx. This takes into account how the WSC voltage is added to the DC voltage to obtain the display voltage, as described recently (16). Since the most absurd voltage of the WSC is

maintained at Vdcx, the movement of the converter can

ideally be associated up to the night synopsis of 2. The best

change register is limited to 4 /  $\pi$ .

Vectors

Obtain the average capacitor voltage

Vance Powering mode

Vance Vectors

Value Veltoge ocross WSC

Output Voltage

Fig. 5 AZCI methodology; (a) Square control format for the selection of extraction and filling modes, and (b) Voltage waveforms at different times of HBHMC.

# **B. FBSM Individual Capacitor Voltage Balance At WSC** In the previous subsection, it is conceivable to maintain the usual WSC capacitor voltage as expected by properly selecting the extraction and stimulation procedures for the development of HBHMC. In any case, this does not guarantee the relative voltages of the capacitors for all FBSMs. In each adjustment of the converter's performance voltage level when it is necessary to avoid an SM, in case a safe SM is chosen, some capacitors can be deceived and others released, their vitality does not extend in the same way between each of they. To maintain the relative voltage of each capacitor, a classification and connection structure is provided with the HBHMC flow chart shown in FIG. 7)

Fig. 7. Classification flow diagram and obtaining of FBSM input signal from WSC.

To control the system for converter activity, Vwscxref is obtained by subtracting the converter performance voltage reference signal (Vxref) from the MHBC performance voltage reference (VABxref). For the separation technique for

development, Vwscxref is the negative of Vxref (Figs. 3-5). After having acquired the reference signal Vwscxref, it is separated and the triangular conveyor plans the signals in stages (because the floor system provides the inclination of the line consonant in the line of the stationary line), to decide which FBSM number It is included in the CSM. If Vwscxref is safe, n FBSM measurements are integrated unambiguously to obtain the ideal positive voltage at the WSC. In addition, n FBSMs are poorly integrated if Vwscxref is negative to obtain the ideal negative voltage at the WSC. It admits that all capacitor voltages are classified from the smallest to the most respectable and, looking at the FBSM, are listed in the scale request at this stage, subordinate to the header, fuse or hijacking the current SM, in the same way as in the Fig. 7. As necessary, this system guarantees an equivalent charge flow for all SM capacitors.

# IV. VALIDATION AND APPLICABILITY OF HBHMC IN SYSTEM OF HVDC

### A. Standalone Mode

The proposed converter and related control boards, a self-controlled example of obviously HBHMC development with two FBSM (N = 2) per plan (Fig. 1), are replicated utilizing PSCAD. FBSM and CC interface limit appraisals are picked. The most amazing voltage contrast is 10% of its particular reference voltage. These evaluations of SM capacitors arrive at the greater part of the limit by conceding  $25 \, \text{kJ/MVA}$  and  $5.2 \, \text{kJ/MVA}$  for HCI and AZCI outlines, as it were..

|         | TABLE III                          |       |  |  |  |  |

|---------|------------------------------------|-------|--|--|--|--|

|         | PARAMETERS OF THE SIMULATED SYSTEM |       |  |  |  |  |

| Sr. No. | Parameter                          | Value |  |  |  |  |

| 1.      | dc-link voltage ( $V_{dct}$ )      | 450 V |  |  |  |  |

| 2.      | Submodule voltage                  | 75 V  |  |  |  |  |

| 3.      | No of submodules/Phase             | 2     |  |  |  |  |

| 4.      | Submodule Capacitance              |       |  |  |  |  |

|         | For HCI method                     | 177µF |  |  |  |  |

|         | For AZCI method                    | 36 µF |  |  |  |  |

| 5.      | dc-link capacitance/phase          |       |  |  |  |  |

|         | For HCI method                     | 56 μF |  |  |  |  |

|         | For ACZI method                    | 40 μF |  |  |  |  |

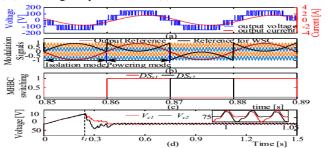

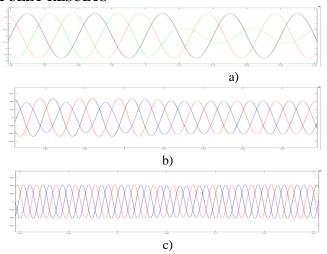

The proposed converter, obliged by strategies for the AZCI structure, shows up on the other hand with the MMC, which requires limit impedance stores of 39 kJ/MVA. To empower over modulation to keep HBHMC, the HBHMC procedure is imitated for mi = 1.2 and the current and yield voltage waveforms of the related converter of the three originators are showed up in Figs. 10 (an) and (b), autonomously. Here, the AZCI procedure is used to control the voltage of the WSC capacitors. The standard sign of coordination using the AZCI framework is displayed in FIG. 10 (c). It might be found in Fig. 10 (c) that around the vertex of beyond what many would consider possible reference, the WSC reference is negative in the positive half cycle and positive in the negative half cycle of quite far reference. This is done so the yield voltage of the converter is more irrefutable than Vdcx, as explained previously in Sec. III-A (Fig. 5). From Figure 10 (an) it seeks after that the degree of the presentation voltage levels has extended from five (for me  $\leq 1$ ) to seven in the significance of the change movement method.

Moreover, the size of the converter yield voltage has been lessened correspondingly, as ought to be evident by looking. (A) with Figs. 8 years) and 9 (a).

Fig. 8 HCI of the HBHMC strategy Waveforms (An) Output voltage, current waveforms, (B) Modulation signals for the HCI technique, (C) MHBC exchanging signals, (D) Isolated WSC capacitor.

Fig. 9. HBHMC waveforms that utilization the AZCI framework (a) limit voltage, limit current waveform, (b) balance signals for the ACZI technique, (c) MHBC trade sign, (d) voltages of individual capacitors of the waveform circuit.

Fig. 10. HBHMC model that works mid = 1.2 (A) three-segment yield voltage waveforms, (B) ace yield current waveforms (C) that change the ACZI framework signals.

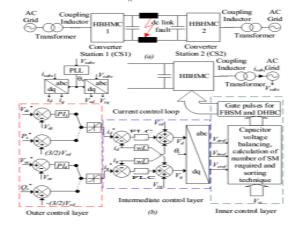

the signals of the conveyor, as can be seen in Figs. 8-10. As such, the waveform quality of the inverter's performance voltage does not prevent even in the over-modulation district. Duplication makes it possible to reach FIGS. 8-10 support the abundance of proposed control structures, activity of course HBHMC activity. HBHC  $^{\rm TM}$  based HVDC frame control can be divided into three specific layers, namely, the extensively engaged and external internal control layers as shown in Figure 11 (b). In this way, subordinate to the useful conversion station, the current reference i d \* is transmitted by a labor controller or the DC interface voltage controller. Other The control plane shown in Fig. 11 (b) can be used in the same way for HVDC parallel based HVDC structure.

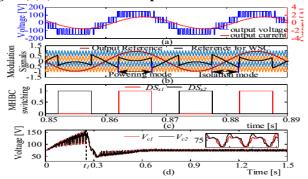

# 1) Series-HBHMC HVDC System Operation:

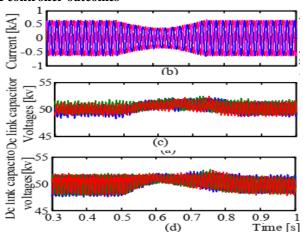

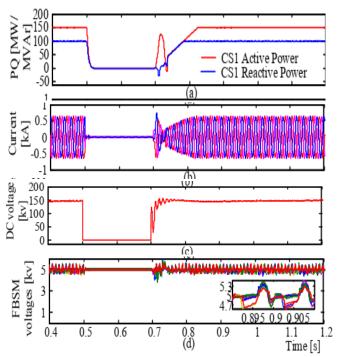

The HBHMC HVDC Activity Plan of FIG. 11 (a), with the unmistakable control layers appeared in FIG. 11b), mirrors a three-section structure to test your client's veneer utilizing theory systems and the abnormal and fragile improvement power of this subsection. In transformer station 1 (CS1), the dynamic and open vitality efficiencies of the converter are controlled, while in the alteration station 2 (CS2), the DC interface voltage and the power control drills are executed. . . Answer. Figure 12 shows the collected amusement when, at t = 0.5 s, the current of the dynamic power bend of CS1 is caught. For instance, s \* shifts from M150 MW to +150 MW. The removal rate P s \* is 1.2 MW/ms. The immediate power waveforms that are went with to the introduction terminals CS1 and CS2 are appeared in Fig. 12 (a). The cooling run flows of three complicit affiliations are appeared in Figure 12 (b). Figs. 12 (c) and 12 (d) show the capacitor voltages of CS1 and CS2 transparently

| PARAMETERS OF THE STUDY HBHMC-HVDC SYSTEM |                                         |            |  |  |

|-------------------------------------------|-----------------------------------------|------------|--|--|

| Sr. No.                                   | Parameter                               | Value      |  |  |

| 1.                                        | dc-link voltage $(V_{dct})$             | 150 kV     |  |  |

| 2.                                        | Submodule voltage                       | 5 kV       |  |  |

| 3.                                        | No of submodules/Phase                  | 10         |  |  |

| 4.                                        | dc-ink capacitance                      | 150μF      |  |  |

| 5.                                        | Submodule Capacitance                   | 0.5 mF     |  |  |

| 6.                                        | Grid voltage for HVDC                   | 220 kV     |  |  |

| 7                                         | Single phase transformer voltage rating | 127kV/35kV |  |  |

TABLE IV

Fig. 11. (a) HVDC Structure Diagram (b) HVDC Square Control Diagram

The capacitor voltages compare to 33% of the prompt and direct interface voltage. Furthermore, the voltage wave periods of the WSC capacitor of CS1 and CS2 are depicted in FIGS. 12 (e) and 12 (f) freely. When the absolute whole of what has been pronounced, we find in Figure 12 that vitality speculation is bored with less individuals destitute in the cooling stream of execution, the capacitor voltages of the DC interface and the capacitor voltages of the WSC converter. At  $t=1.0~\rm s$ , the response power reference of CS1 (\*) changes from - 100 MVAr to +100 MVAr, with 1.2 MVAr/ms slanted. The waveforms of the response and the dynamic forces at the introduction terminals CS1 are depicted in Fig. 14 (an) and take a reticle on the voltage waveforms of the DC interface capacitor and the floor.

The voltage waveforms of the WSC capacitor are shown in the figures. 14 (b) and 14 (c), straightforwardly. What's more, at  $t=1.5\,$  s, the response power reference CS2 changes from +100 MVAr to - 100 MVAr and open-wave dynamic power structures are created at the inverter's exhibition terminals. The DC interface voltage and the WSC capacitor periods of CS2 are shown in FIGS. 15 (a), 15 (b) and 15 (c), without hindrances.

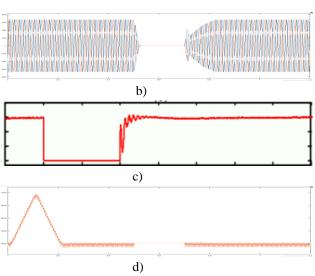

# 2) Control Of Arrangement HBHMC HVDC System Under DC Fault Condition:

The properties of HBHMC are its rectangular DC ability with no space edge. Since HBHMC utilizes FBSM, it is entirely sensible to apply a switch point voltage further from a persistent edge issue, close to these lines that power/divert the present significance of the issue. The accompanying circuits are typically dynamite and appalling voltage cycles, of which the 1/2 cycles show up in Figs. 15 (an) and (b), as I would like to think. Figure 16 shows the outcomes as the casing is shown on the pivot to present the CC distortion (Figure 11 (a)). Prior to the need occasion, the course of action of Figure 11 (an) is in a rational state and it bodes well to work with \* = 150 MW and Q s = one hundred MVAr in CS1 (Figure 11 (b)). FIG. 16 (a) shows that the related power references CS1 are seen before zero.5 s in the execution of the diversion. At t = 0. Five s, a power disappointment of the consistent side hub yield is performed, which keeps going 200 ms. After the flaw occasion, it tends to be found in Figure 16 (a). Figure 16 (c) shows the ceaseless point of view voltage of the converter, which should drop to 0 for the scope of the transmit time interim. . Fig. 16 (d) shows the FBSM capacitor voltages of class a,. In the wake of deleting the shortcoming at t = zero.7s, the switch actuation sign for every one of the change stations is opened and the reference control settings (s \*, s \*, figure 11). (b)) usually increment from zero to pre-twisting. From start to finish, it very well may be seen from Figure 16 (b) that the converter finds the information flows for a brisk designation of time when the converter is opened.

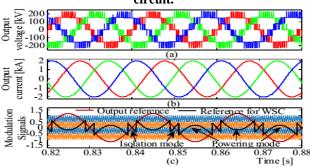

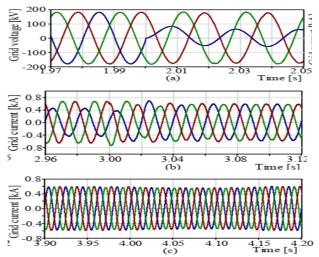

# 3) Control of Arrangement HBHMC HVDC System under Voltage Unbalance Condition:

In past reproductions, HBHMC was outfitted with the manual for anticipate basic states of three adjusted parcels. Regarding the HBHMC social open door circuit (Fig. 2 (a)), the 3 capacitor voltages (Vdca, Vdcb, Vdcc) of the three

### PI controller outcomes

Fig. 12. Converter responses for the HVDC device when the dynamic energy flow is changed from - 150MW to 150MW in CS1 (a) burning imperative in CS1 and CS2, (b) rhythmic movements of the 3-territory cooling system in CS1, (c) DC associated voltages CS1, (d) DC hyperlink voltages CS2, (e) WSC FBSM capacitor voltages in CS1, and (f) WSC FBSM capacitor voltages in CS2 area.

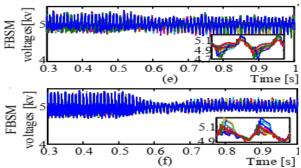

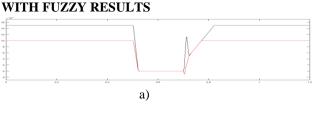

**FUZZY** controller results

Fig. 13converter responses for the HVDC machine, while dynamic quality went from-150 MW to 150 MW in CS1 (year) of extravagant power in CS1 and CS2, (b) three-part cooling frame currents in CS1, (c) CS1 dc interface voltages, (d) dc2 hypertext link voltages, (e) FSCM capacitor voltages of the WSC region in CS1 and (f) FSCM capacitor voltages of the WSC stage in CS2

Fig. 14. The CS1 responses while the CC problem occurs between 0.5 seconds and 7 seconds (a) the power and reception requirements at the time of the CC deficit include, (b) a contemporary cooling at the time of continuous angle emission, (c) DC interface voltage lower than the fault condition, (d) FBSM capacitor voltages in zone a. The individual steps could depend on the specific degrees of power transferred to the structure.

Fig. 15. The CS1 responses while the CC problem occurs in the range of 0.5 to 0.7 seconds (a) the quality of work and the reactivity on the DC side are not satisfactory, (b) the cooling ahead of the plane at the same time in terms of DC current) interface voltage occurs at a given stage of the fault, (d) FBSM capacitor voltage of zone a.

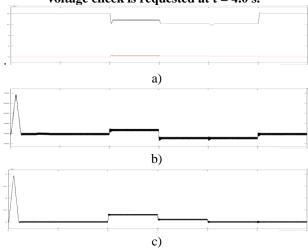

Individual steps may depend on the specific degrees of solidarity transferred to the structure. Figs. 16 and 17 introduction. Figure 16 (a) proposes system voltages of 3 pieces after an imbalance in  $t=2.0\,\mathrm{s}$ . As soon as the HBHMC is presented to the voltage imbalance system and no imbalance installation / regulation is activated (i.e.,  $T=2.0\,\mathrm{to}$  zero), the air conditioning control system will operate downstream (Fig. Sixteen (b )) and the DC capacitor. The voltages (Fig. 17 (b)) of the HBHMC series increase with an imbalance before  $t=3\,\mathrm{s}$ . 16 (b) and 17 (b) that, despite the way in which the secondary currents of the forced air system continue to be balanced by techniques for the undeniable component of a terrible game plan controller, the capacitor voltages associated with The direct current is now disproportionately higher (iE, from  $t=3.0\,\mathrm{to}\,4.0$ ).

Fig16. (an) Imbalance in voltage set-up in t=2.0~s, (b) the network flows when a fine and disgusting current control is controlled at t=3.0~s and (c) the network circulates while the voltage control The capacitor starts at t=4.0s

Fig. 17. Measures to be taken by the HBHMC to cool the imbalance voltage on the side: (a) reactive energy, energy, (b) DC hyperlink capacitor voltages, and (c) fundamental estimates of capacitor voltages WSC.

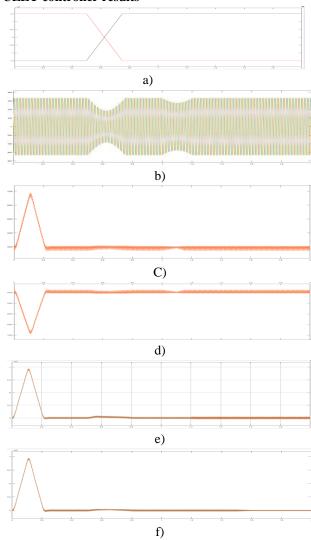

### **FUZZY RESULTS**

Fig. 18 (a) Unbalanced condition in the tension of the structure at  $t=2.0~\mathrm{s}$ , (b) cross-section currents when they are effective, the low current check is sanctioned at  $t=3.0~\mathrm{s}$ , and (c) sets the currents while the capacitor voltage check is requested at  $t=4.0~\mathrm{s}$ .

Fig. 19. The response of HBHMC actions to the AC side voltage modifies: (a) the working power and the open power, (b) the capacitor voltages of the DC interface and (c) the Normal estimates of DC voltage.

WSC condenser. When the controller is penalized at t = 4.0 s within the deviation, the capacitor voltages level. Figure 15 (c) shows in a similar way that the converter current remains balanced after the activation of each of the additional controllers. In this way, each of the control objectives had been met. Figure 16 (a) shows the strategically displaced dynamic and reactive power for the HBHMC to be structured.

# V. COMPARISION BETWEEN PROPOSED AND EXISTING METHOD

As we've got discussed in advance, Existing technique is PI controller HVDC circuit technique is Fuzzy Controlled HVDC circuit. Figure 12 (c) & (D) and Figure thirteen (c) & (D) indicates the DC-hyperlink voltages of the CS1 and CS2 respectively. Fluctuations in Figure 12 are extra in comparison with parent thirteen, so calculation of mistakes and rectification is less green with PI controller.

Figure 14(a) & 15(a) shows the Active and reactive energy and Figure 14(d) &15(d) shows voltage throughout capacitor. Gradual increment of Active energy shown in 14(a), while

Sudden incremental in 15(a). High voltage fluctuation in 16(d) & less voltage fluctuation in 15(d). Figure 17 and 19 describes about results in PI and Fuzzy. Figure 17 (d) & (e) having more fluctuations in comparison with determine 19 (d) & (e)In above assessment Fuzzy controller showing less fluctuations compared with PI.

## VI. CONCLUSION

An H-bridge hybrid multilevel converter techniques of HBHMC for Gird programs. In the Application of Fuzzy controller in H-Bridge hybrid multilevel topology turned into carried out. Better Results have been determined with Fuzzy controller than PI. Fluctuations in voltage throughout dc-link had been decreased.

### REFERENCES

- A. Lesnicar and R. Marquardt, "A dynamic geography of multinivel measured convertidor custom fitted to an amplia gama de potencias", inProc. Power Tech Conf., 2003, vol. 3, p. 1-6.

- S. Allebrod, R. Hamerski and R. Marquardt, "New convertible multi-arrange lifts and elevators for HVDC transmission", inProc. IEEE Power Electron. Experts Conf., 2008, p. 174-179.

- J. Dorn, H. Huang and D. Retzmann, "Nuevos de convertio de volta de voltae para aplicaciones y hechos HVDC", inProc. CIGRE, Osaka, Japón, 2007.

- R. Marquardt, "Secluded staggered converter: a typical idea for hvdc arranges and broadened ceaseless bundles", Proc. In t. Power Electron Conf., 2010, p. 502-507. [5] L. X. Tang y B. T. Ooi, "Ubicación y aislamiento de defectos de CC in multi-terminal CC sistemas", IEEE Trans. Power Del., Volumen 22, no. 3, páginas 1877-1884, julio of 2007.

- R. Marquardt, "Topologies of multinivel particular convertior con hindrance of cortocircuito corriente de CC", Proc. IEEE Power Electron. Y ECCE Asia, 2011, p. 1425-1431.

- J. Yang, J. Fletcher, J. Furthermore, O. Reilly, "Análisis y ubicación de cortocircuitos y fallas a tierra in CC redraded links in VSC", IEEE Trans. Indiana Electron., Volumen fifty nine, no. 10, p. 3827-3837, octubre of 2012.

- K. Friedrich, "Application moderne de VSC HVDC PLUS dans l. A. Topologie de convertisseur modulaire à plusieurs niveaux", dans Proc. IEEE Int. Symp. Indiana Electron., 2010, pages 3807 à 3810

- C. Franck, "Disjoncteurs CCHT: une dissect pour identifier les futurs besoins de recherche", IEEE Trans. Power Delivery, vol. 26, non. 2, pages 998-1007, avril 2011.

- X. Li, Song Q, Liu W. H, Xao R, Xu X Li, "Protección de falla no everlasting en líneas aereas corriente persevered in MMC basado in sistemas HVDC, "IEEE Trans. Entrega de Potencia, Vol. 28, no. 1, pp. 483-490, enero de 2013

- Q. Tu, Z. Xu and L. Xu, "Decreased Switching Frequency Modulation and Circulation Suprasion for Modular Multilevel Converters", IEEE Trans. Power Del., Volume 23, no. 3, pp. 2009-2017 2011.

- R. Picas, J. Pou, S. Ceballos, VG Agelidis and M. Saeedifard, "Minimización de las fluctaciones de voltaje del condensador de a secluded multinivel convertidor mediante el tráfico flujo de fluo", in proc. IEEE Industrial Elect. Conf. (IECON), Montreal, June 2012, p. 25-28.

- P. Josep, S. Ceballos, G. Konstantinou, V. Agelidis, R. Picas and J. aragoza, "Metodos of inyección de corriente circulante basados en información instantánea para el convertidor measured multinivel", IEEE trans. In Indust. Choose., Volumen 2, páginas 777-788, 2015.

# **AUTHORS PROFILE**

Himabindu Veldurthi Received B Tech Degree in Electrical and Electronics Engineering From G.Narayanamma Institute of technology & Science College Jawaharlal Nehru Technological University Hyderabad, India 2017.she Was worked as lecturer in Polytechnic for a period of 6 Months,

Journal Website: www.ijitee.org

she is currently pursuing MTech in Anurag Group of Institutions (CVSR), Hyderabad, India in Power Electronics and Electrical Drives.

S.SARASWATHI received B.TECH degree from Sri Kottam Tulasi Reddy Memorial College of Engineering (JNTUH) in the year 2006 and received M.Tech in the stream of Electrical Power in Srinidhi Institute of Science And Technology .Currently working as a

Associate Professor in Anurag Group of Institutions (cvsr) since 9 years. And her areas of interest are Power Systems, Electrical Circuits and Control Systems.

**DR.T. ANIL KUMAR** working as a Professor and Head of EEE Department in Anurag Group of Institutions. He obtained his B.Tech from Kakatiya University, MTech and Ph.D from JNTUH University He is having 19 years of teaching experience. He has organized and attended various workshops and conferences at

National and International levels.