# Managing Inrush Current using Hot Swap and ORing FET

Raji.C, Mohan Kumar Velumani, S. N. Prasad

Abstract: Critical, high availability systems will always rely on redundant power for continuous operation when the default power fails or becomes unavailable. When the back-up system kicks in, there will be a huge inrush current depending on load. The consequences of inrush current can be reduction of output voltage, tripping of protective devices, damage to sensitive devices either on at the load or on the back-up system itself and eventually system failure. This dissertation studies the effects of inrush current on an already existing Redundant Power Distribution System (RPDS). A review of existing technique to control inrush current is presented. A new solution has been implemented on the Redundant Power Distribution System such that the functionality of overall system is preserved. Finally, performance of existing solution on RPDS and new solution are compared. Keywords: inrush current, RPDS

#### I. INTRODUCTION

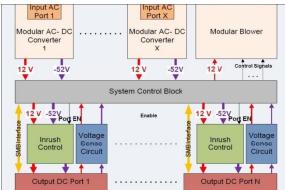

Redundant power is a critical component in high availability systems. Redundant Power Distribution System (RPDS) is a standalone system that provides power to such high availability systems (subsequently referred to as Load Units) when the Load Unit's default power supply fails or becomes unavailable. RPDS provides DC power to Load Units over two voltage rails: +12V and -52V. These voltages are generated by modular AC-DC converters. RPDS has 'N' number of output DC ports, but only few ports can be powered simultaneously. Custom cables are used to connect DC power ports with Load Units. When a Load Unit's power supply fails or becomes unavailable, RPDS starts powering the Load Unit such that it does not gets power-cycled. RPDS system can handle a maximum power of 650W on +12V rail and 1700W on -52V rail. Each DC power port is capable of delivering a maximum power of 300W on +12V rail and 850W on -52V rail. RPDS can provide power to any of the N connected Load Units. The maximum number of Load Units that can be powered simultaneously depends on the power available on RPDS.

Revised Manuscript Received on November 30, 2019. Correspondence Author

Prof. Raji. C\*., Assistant Professor, Department of VLSI, REVA University, Bangalore, India.

Mr. Mohan Kumar Velumani, Department of VLSI, REVA University, Bangalore, India.

Dr. S. N. Prasad, Professor, School of ECE, REVA University, Bangalore, India. Email: prasadsn@reva.edu.in

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license http://creativecommons.org/licenses/by-nc-nd/4.0/

Retrieval Number: A4874119119/2019@BEIESP DOI: 10.35940/ijitee.A4874.119119

Journal Website: www.ijitee.org

RPDS communicates with Load Units over System Management Bus (SMB) interface. RPDS is the slave and Load Units are always the master. The custom DC cable contains the required connections for SMB interface. The firmware residing on RPDS keeps monitoring the voltages on Load Units. When the voltages drop below a threshold value, RPDS starts powering the Load Units. RPDS does not have any mechanism to know if a Load Unit's power

It is the responsibility of Load Unit's system software to send appropriate command to RPDS to stop the power delivery to Load Unit. Power delivery from RPDS is stopped such that Load Unit never gets power-cycled. Such start or stop of power delivery without the

Load Unit getting power cycled is called Reliable Crossover.

Block diagram of RPDS is shown in Figure 1. This dissertation focusses only on the "Inrush Control" section shown in the block diagram.

Figure 1: Block diagram of RPDS

## A. Various Inrush Current Limiting Techniques:

Passive Techniques

- Inductors

- Resistors

- NTC Thermistors

Active Techniques

- Bypass Switch

- **MOSFET**

### **B. Existing Solution on RPDS**

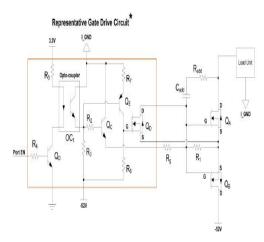

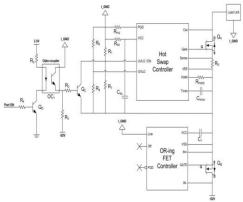

Figure 2 shows the existing solution circuit on RPDS taken from [2] and the design equations are shown from 1.1 - 1.5. Cadd, Radd and Rg control the inrush current. Rg and R1 resistor divider sets the gate drive voltage.

## Managing Inrush Current using Hot Swap and OR-ing FET

Cadd adds on to Cgd capacitance and increases the Miller plateau and in-turn controls the inrush current. QC controls the turn-on. QE and QD ensures faster discharge of Cadd at turn off. RPDS's design was dependent on load capacitance and was originally designed for Load Units with low capacitance. As the Load Units became more sophisticated, the load capacitance also increased.

For large load capacitances, Cadd becomes large. A large Cadd capacitance means larger turn-on and turn-off time.

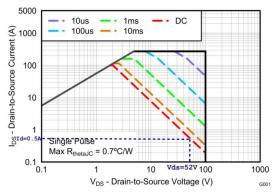

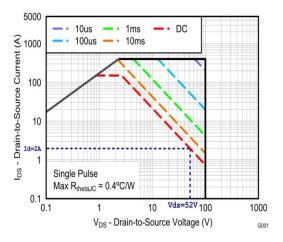

Larger turn-on time means, RPDS cannot start backing-up immediately and there are possibilities of Load Unit being reset. Hence value of Cadd had to be restricted. With the restricted value, RPDS had no issues providing back-up power when the Load Unit's default power fails or suddenly becomes unavailable (as the load capacitances are already charged). But when powering a completely off Load Unit, Safe Operating Area (SOA) of switching element (QA) present on -52V rail in RPDS's DC port was violated. Over a period of time, the nMOSFET failed, leading to a system failure. The existing solution was simulated and tweaked. But the nMOSFET's SOA was still violated.

Fig 2: Existing circuit on RPDS

Simulation result comparisons with nMOSFETs having same package, footprint and highest SOA available also resulted in SOA violations [2].

$$I_{lnrush} = C_{load} * (V_{dd} / dt) * dt = C_{load} * (V_{dd} / I_{lnrush})$$

(1.1)

$$V_{plt} = V_{th} + (I_{Inrush} / g_{fs})$$

(1.2)

$$I_g = C_{add} * (d_{VDS} / dt)$$

1.3)

$$R_{\text{g}} = \left(V_{\text{GG}} - V_{\text{plt}}\right) / I_{\text{g}}; \; \text{Set} \; V_{\text{plt}} < V_{\text{GG}} < V_{\text{GSMax}} \eqno(1.4)$$

$R_1 = V_{GG} R_g / (52 - 0.7 - V_{CESat} - V_{GG});$ Choose  $R_{add}$  such that  $R_g \gg R_{add}$

(1.5)

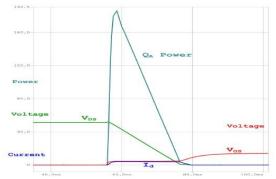

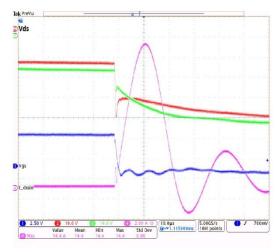

Fig 3: Simulation of existing circuit for a load capacitance of 1200uF

Fig4: Simulation of existing circuit for load capacitance of 200uF.

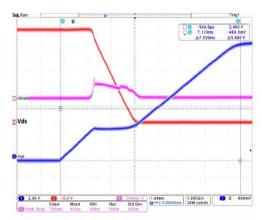

Fig 5: MOSFET switching on-board capture for 200uF load.

Fig 6: MOSFET switching on-board capture for 1200uF load: part failure.

Journal Website: www.ijitee.org

Published By:

& Sciences Publication

Fig 7: MOSFET switching on-board capture for 1200uF load: part failure.

Fig 8: SOA of existing nMOSFET

Fig 9: SOA of nMOSFET having same package footprint and highest SOA available.

#### C. Design Specification for new solution

- Nominal output voltage -52V

- Load current: 17.5A (continuous, per port). This is the max current drawn by Load Unit.

- Peak load current: 19A (continuous, per port).

- Ability to handle load capacitance in excess of 1000uF

- UVLO Threshold: -44V

- OVLO Threshold: -57V

- MOSFET package should remain the same (internal requirement)

- Zero SOA violations

- Ability to protect RPDS against power into short and hot short on Load Unit

# II. NEW INRUSH CURRENT LIMITING SOLUTION

The below figure 10 shows the new inrush current limiting solution that was implemented on RPDS (hot-swap and ORing FET controller). An example of hot-swap controller is LTC4252 and OR-ing FET controller is LTC4371 both are of Linear Technology make.

Fig 10: New inrush limiting solution circuit.

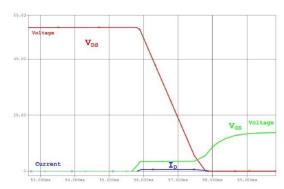

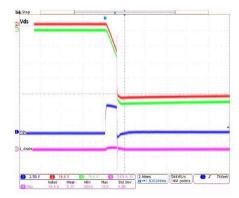

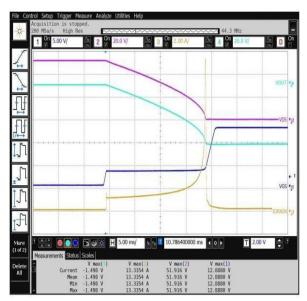

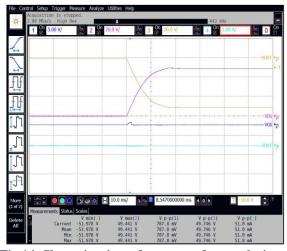

The new circuit as shown in Fig 10 handled different Load Units gracefully. A turn on capture with a load of  $1200\mu F$  is shown in Figure 11. The initial current rise observed was around 1.5A and the turnon / inrush limiting time was ~20ms. Both these are almost like the theoretically calculated values. This turn-on time is much slower compared to the existing solution, but the delay is acceptable since it is at power-up. Maximum current spike of 13.3A was observed at the end of turn-on time i.e., when the MOSFET was completely on and VDS is almost zero. This spike is well within the SOA curve of the MOSFET. The load current drops almost to zero soon after turning on. This is a characteristic of the load. The software running takes bare minimum power during initial boot-up and draws full power only after complete boot-up.

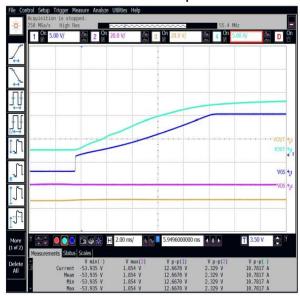

Figure 12 shows RPDS backing-up a Load Unit when the Load Unit's default power supply shuts down. The turn on is much faster since the load capacitances are already charged. Miller plateau is not observed on VGS curve since the MOSFET Cgd is already discharged. VDS remains flat (0V) because there is -52V available on both RPDS and the Load Unit. As can be observed from Figure 12, RPDS successfully backed-up the load unit without the Load Unit being power cycled. Figure 13 shows the capture of QB in reverse powered condition, i.e., when Load Unit is powered-on and RPDS is powered-off. As can be seen OR-ing FET controller pulls the gate down in this condition. Voltage appears at the source terminal of QB from the Load Unit through the body diode of QA. The same happens with the existing circuit. QA's body diode allows current to pass through when reverse powered and QB blocks the current from flowing into the system.

## Managing Inrush Current using Hot Swap and OR-ing FET

OVLO and UVLO limits were tested using a standalone DC supply. The observed limits were VUVH = 44V, UVL = 42V, VOVH = 56V and VOVL = 55V. Circuit performance with load capacitance up to 1800uF worked fine without any issue. The turn-on time observed varied up to 30ms. For load capacitance greater than  $1800\mu F$ , the  $C_{timer}$  value needed to be tweaked.

The short circuit performance of the new solution is shown in Figure 14. The circuit performance was not what was expected. During a short circuit event, the rise in current is very sharp. The design with Hot-Swap Controller is not fast enough to detect this current rise and shut down the MOSFET. The figure shows a failure graph and the MOSFET was damaged during the event. Subsequent tries on multiple units resulted in the same failure on every unit. Circuit performance with higher load capacitance greater than  $2000\mu F$  also resulted in similar damage. Investigation is ongoing to come-up with a new circuit that can survive a short circuit event and higher load capacitance.

Fig 11: Turn on capture with new solution and a load of 1200μF

Fig 12: RPDS backing-up a Load Unit

Fig 13: OR-ing FET controller shutting off QB in reverse powered condition

Fig 14: Short circuit performance of new solution.

# III. CONCLUSION

Huge Inrush currents as redundant power systems are operational leads to reduction of output voltages, damage to sensitive devices. The New Inrush Current Limiting solution with Hot-Swap Controller and OR-ing FET combination is definitely an upgrade over the existing circuit. The HSC dynamically adjusts the turn-on time depending on load to make sure the inrush current is with the limits set by RS and RPWR resistors. The circuit can be easily tweaked for a new MOSFET for any kind of load. The UVLO and OVLO settings are new features which are not present in the existing solution. Future enhancements would be to add short circuit surviving capabilities.

#### REFERENCES

- E. J. Lee, et al., "Comparative Analysis of Active Inrush Current Limiter for High-Voltage DC Power Supply System" Oct 2012, 2012 IEEE Vehicle Power and Propulsion Conference (VPPC).

- C. S. Mitter, "Active Inrush Current Limiting Using MOSFETs", Motorola Inc. 1995

- Vrej Barkhordian, "Power MOSFET Basics", International Rectifier, 2003

- Alek Kaknevicius and Adam Hoover, "Managing Inrush Current", Texas Instruments, Aug 2014

- 5. OrCAD Capture 16.6, fast, intuitive PCB schematics design solution.

- 6. "How to stop Inrush Current", Ametherm

- 7. LTC4371, Negative Voltage Ideal Diode OR-ing Controller

- 8. LTC4252, Negative Voltage Hot-Swap Controller.

#### **AUTHORS PROFILE**

Prof. Raji. C. Asst Prof, School of ECE, REVA

University, Bangalore. M. Tech in VLSI and

Embedded Systems, (PhD). Research Areas:

Digital VLSI, Analog VLSI, Artificial Neural

Networks, Fault tolerant circuits.

raji.c@reva.edu.in

Mr.Mohan Kumar Velumani, is Hardware System Designer and is presently working as Tech Lead at Stanley Black and Decker. He pursued his MTech in VLSI Design & Embedded Systems from REVA University, Bangalore. co.mohankumar@gmail.com

**Dr.S.N.Prasad,** Professor, School of ECE, has over 22 years of teaching and 5 years of Research experience. His Research areas are Neural Networks, AI, ML etc. prasadsn@reva.edu.in

Retrieval Number: A4874119119/2019©BEIESP DOI: 10.35940/ijitee.A4874.119119

Journal Website: www.ijitee.org