# Multi-Core Eight Bit Ternary Content-Addressable Memory Design Based Image Learning System

## S. Bhargav Kumar

Abstract: In this research work, the image is learned to find features to make use of during its analysis and a genetic apices based low power Ternary Content-Addressable Memory (TCAM) is designed to implement the proposed image learning system. A technique called Content Matching Search Register is proposed in this work to perform the image learning operations in proposed TCAM architecture. This paper proposes an ImOFF algorithm for image analysis. The focus of this multi-core TCAM (MC-TCAM) is to make fast computations and search based designs. The focus application of this research work is in the design of low power On-board Embedded-VLSI chip to perform image analysis. Proposed multi-core eight bit Ternary TCAM (MCEB-TCAM) is analyzed using IC design tools in 90nm technology, using Verilog hardware description language and usage of Cadence for layout generation and parasitic extraction of the circuit components.

Keywords: Feature learning, TCAM, Image Analysis, Cadence, pixels.

# I. INTRODUCTION

With the increasing complexity in image projection [1] [2] [15] a vast variety of analysis methods and approaches have emerged. Recent advances in image analysis provide high resolution images of the texture structure, so that accurate image illusion model representations can be practically measured. Requires image-based illusion analysis, providing valuable information for projection and representation during image rendering problems, to avoid image benchmarks for both projection - orientation and localization of the image object of interest. A shape reference descriptor, which minimized the coefficient assignment problem, but did not take into account neighborhood points. Under several schemes, a different projection setting was used to solve the matching problem, to detect shapes in the projected images, to improve the corresponding recovery of the projected image. They are used to project image data into a constraint processing, providing an open-ended problems under sequential approximations.

Revised Manuscript Received on November 30, 2019.

\* Correspondence Author

**S.Bhargav Kumar\***, Electronics & Communication Engineering (ECE) Department, Jawaharlal Nehru Technological University Hyderabad, Hyderabad, India. Email:sbhk.kumars@gmail.com

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license <a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>

CAMs [3-5] were designed based on a broad under two categories: first only for search function and second write function with search function. In contrast to these two functions, these days CAMs were predominantly used in parallel processor, to perform various types of parallel data processing with words and addresses. In proposed EB-CAM, this makes an importance to create a compact, highly parallel processing system that requires high levels of performance.

### II. PROPOSED METHODOLOGY

A TCAM [7] [8] has three modes of operation, namely: Read, Write and Compare. Since TCAM has a compare operation feature, it performs this feature in two parts: storage and a comparison. By comparing the input data in memory within a single clock cycle predicts the performance and efficiency of a TCAM, resulting in better search time comparatively with the other memory search algorithms. On this contrast, a TCAM which has a feature of high clock levels of performance to achieve high bit or word content searching is proposed in work.

Set of rules to be followed in solving the TCAM design problems are:

- a. The size of the design is with 90nm scaling, which reduces the parasitic losses.

- b. The parallelism is 8 bit level, to improve the performance of Read Write Cycle Operations.

- c. The power is reduced through genetic apices method, extracting the minimum power utilized at each section of design and that power is maintained as a stable power through-out the design.

### A. Content Matching Search Register

By giving new data through shift address register Content (In) Search Address Register at each clock cycle, a valid Content (Out) Search Address Register result output for each clock cycle. Each bit location in the shift address register is connected to all the matching cells in the corresponding row wise column distributor as indicated by horizontal lines. Until the Match\_Ack goes high, output Content (Out) Search Address Register of the Content Encode Register is not updated.

During a low Clock\_Enable operation (shift data in Content Matching Search Register), there should be no shifts in Content (In) Search Address Register and the Search\_Enable and Match\_Ack should be low.

# Multi-Core Eight Bit Ternary Content-Addressable Memory Design Based Image Learning System

This will ensure that the outputs of all words are kept inactive.

During a high Clock\_Enable operation (match data in Content Matching Search Register), MCEB-TCAM during the first clock of Clock\_Enable, bit-by-bit the content data is loaded into Content (In) Search Address Register, during the second clock of Clock\_Enable, Search\_Enable is enabled to initiate the readwrite technique to search the content for predicting the matched\_content or not\_matched content, during the third clock of Clock\_Enable, Match\_Ack goes high then the output of Content (Out) Search Address Register is updated and during the third clock of Clock Enable, Match Ack goes high, contents with Content (In) Address Register will be verified for matching with Content Encode Register Address, then the output of Content (Out) Match Address Register will be verified with Match\_Lines and Not Match\_Lines lines.

And during the successive clocks using readwrite circle (RW\_C) circuit the readwrite technique will continue Content to perform faster content searching process.

CMOS based TCAM [9] are having low scaling capacity, performance degradation as data size increases, longer switching times and inefficient in terms of cost or power [10]. With proposed approach of design, TCAM can perform fastest [11] [13] content packet scanning against the sophisticated content patterns.

Now, provide an insight to proposed approach,

- a) Highest match result

- b) Low power consumption

- c) High level of Contentism

- d) High Efficiency

## B. Operation of Multi Core Eight Bit TCAM architecture

Search\_Content() in real time operation contains multiple content, need multi-cycle operation proportional MCEB-TCAM locations. Compare to conventional TCAMs implementation [12] [14], MCEB-TCAM performs the comparison Content using multiple memory locations, using only one Content Encode Register by increasing the speed of comparison for Match\_Valid() for MTrue() and MFalse(). Proposed MCEB-TCAM VLSI Design Architecture Implementation accomplish eight stages of Contentism.

Stage 1: uses single memory location in Content Encode Register to compare each single bit memory block location.

Stage 2: uses a memory Content comparisons, to initiate the MTrue() and MFalse() acknowledgment with an integer match valid S-status of Match\_Valid(). In this stage the value of S is 1, corresponding to two Content and results in MCEB-TCAM of Search\_Content() two-bit comparisons.

Stage 3: approach will enable the eight-bit content search bus for the MCEB-TCAM memory blocks. Each memory block will be decoded by eight-bit content search status register bits.

Stage 4: uses a eight bit write operation in eight-bit encoder operations, to perform 64 bits read operation. This stage reduces the clock utilizations and improves the clock performance.

Stage 5: performs Content memory comparisons between 64 bit Search\_Content() with 64 it MCEB-TCAM address locations simultaneously in eight clock cycles only.

Stage 6: combines 64 bits in Content way with 8 64 bits, combined with the Content Encode Register with the minimum Content search of 512 bit content search in eight clock cycles only

Stage 7: gives an 512X512 Content content search performance increasing the clock performance by utilizing 16 clock cycle only.

Stage 8: performs the logical ORed operation of proposed standard multi-cycle MCEB-TCAM operation implementation.

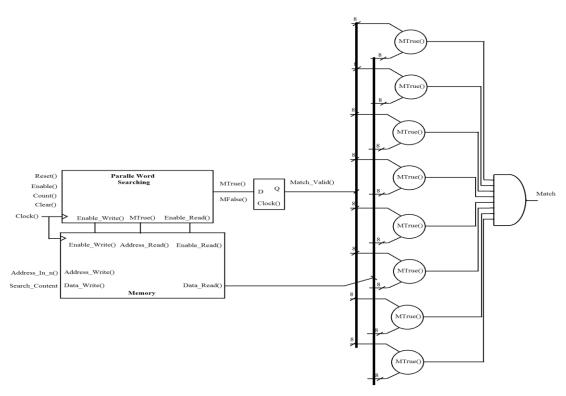

For eight cycles operation, as shown in figure 1, the process is

Process 1: During multipleMatch\_Operation(), the search of MCEB-TCAM for multi-cycle match to an input Search\_Content() is performed by simply searching sequentially through all the memory locations i.e., reading the Search\_Content(), comparing the Search\_Content() and Enable() is performed to Data\_Read() a valid MTrue() for mulipleMatch Operation(). In this operation, MTrue() and Match\_Valid() is asserted.

Process 2: If no MTrue() is found, Match\_Valid() is not asserted, but Match\_Valid() is asserted for all the addresses compared in the search operation. Match\_Valid() indicates the read cycle completion.

Process 3: During the multipleMatch\_Operation(), considering multiple MCEB-TCAM content locations, the output of Single Bit MCEB-TCAM architecture is indicated by single bit operation MCEB-TCAM, resulting in either 1-bit match or 0-bit match, using one-bit Content encode register at each MCEB-TCAM location. Content Encode Register stores the content of match validation, each Match\_Valid() with MTrue() stores a 1-bit eight-bit register and each Match\_Valid() with MFalse() stores a 0-bit eight-bit register. The storage single-bit eight-bit register is a distributed register, for multipleMatch\_Operation(), all the MTrue() and MFalse() results will be logical ORed to result Search\_Content() MCEB-TCAM single-bit operation.

Process 4: Match\_Valid() will indicate the assertion of MTrue() and MFalse() to content address matching during search operation and results to status of Match\_Operation() and NonMatch\_Operation(). When Search\_Content() match is found, performs Match\_Operation(), resulting into validation Match\_Valid(), indicating MTrue() with Match acknowledgement.

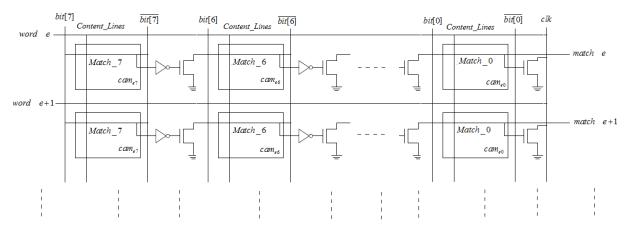

A block diagram of Proposed MCEB-TCAM Design is shown in figure 2. Single Cell content and is used to perform the cumulative eight bit comparison of eight bit cells implemented as shown in Proposed MCEB-TCAM Design. MCEB-TCAM consists of 64K word x 288-b memory call array including an address decoder, a Content encoder, registers, I/O buffers, and control circuits for external circuits. A Search\_Enable signal is used to use an automatic content search refreshing operation in MCEB-TCAM. A Content Search Register is used to decode the Content Match, Address Match and Match Status signals.

Journal Website: www.ijitee.org

Each of 2048 MCEB-TCAM cells consist of 16 memory cells which to store the content label and match bits. The Search\_Content() is applied is compared with every bit stored in the MCEB-TCAM cell, if match bit='1', then MCEB-TCAM will perform the Content\_Comparison operation with stored value in MCEB-TCAM cells.

A Match\_X is performed by looking at the Bit and select lines of MCEB-TCAM. If the data mis-matches with the contents of MCEB-TCAM cell and the Match\_X is pulled low, the stored match bit becomes '1'.

In other conditions, the stored match bit becomes '0' for data matching with the content of MCEB-TCAM cell and by making Match\_X is pulled to high.

Fig. 1. MC Eight Bit TCAM Architecture

#### III. RESULTS AND DISCUSSIONS

MCEB-TCAM is designed and simulated using IC design tools in 90nm technology. After designing MCEB-TCAM at the architectural level, behavioral and functional verifications

will be done using the Verilog hardware description language, with layout generation and parasitic extraction of the circuit components of all proposed MCEB-TCAM using Cadence are shown in table 1 and 2.

Fig. 2. Proposed MC Eight Bit TCAM design using Dual-TCAM blocks

Table 1: MCEB-TCAM (8192-bit) Performance Statistics

|                    | Desig         | n          | Implementation | Performance |             |  |

|--------------------|---------------|------------|----------------|-------------|-------------|--|

|                    | Combinational | Sequential | Device (%)     | Max.        | Min.        |  |

|                    | Modules       | Modules    |                | Frequency   | Cycle (ns)  |  |

|                    |               |            |                | (MHz)       |             |  |

| 512x8 Distributed  | 2158          | 2017       | 50             | 170         | 15.5(Write) |  |

| RAM                |               |            |                |             | 16.3(Read)  |  |

| 1024x8 Distributed | 5139          | 4421       | 98             | 210         | 19.9(Write) |  |

| RAM                |               |            |                |             | 817(Read)   |  |

| 2048x8 Distributed | 10589         | 8125       | 197            | 291         | 29.6(Write) |  |

| RAM                |               |            |                |             | 1,150(Read) |  |

Table 2: MCEB-TCAM (8192-bit) Design Statistics

|             | Power Consumption (For 2.5 ns search time) |          |          |         |                     |          |        |            |         |  |  |

|-------------|--------------------------------------------|----------|----------|---------|---------------------|----------|--------|------------|---------|--|--|

|             | V <sub>bias</sub>                          | $V_{ML}$ | $I_{ML}$ | Current | Voltage             | $I_{ML}$ | %Q     | %          | %       |  |  |

|             |                                            |          |          | Source  | difference          | drop-off | (full  | Speed(full | Energy/ |  |  |

|             |                                            |          |          | Enabled | between             |          | match  | match &    | Search  |  |  |

|             |                                            |          |          | Time    | ML <sub>H</sub> and |          | & miss | miss       |         |  |  |

|             |                                            |          |          |         | $ML_L$              |          | match) | match)     |         |  |  |

| 512x8       | 0-0.6V                                     | 0.04V    | 2μΑ      | 1.2ns   | 295 mV              | 2.3ns    | 65     | 51         | 65      |  |  |

| Distributed |                                            |          |          |         |                     |          |        |            |         |  |  |

| RAM         |                                            |          |          |         |                     |          |        |            |         |  |  |

| 1024x8      | 0-0.6V                                     | 0.40V    | 17.8 μΑ  | 2.4 ns  | 391 mV              | 18.4 ns  | 91     | 81         | 91      |  |  |

| Distributed |                                            |          |          |         |                     |          |        |            |         |  |  |

| RAM         |                                            |          |          |         |                     |          |        |            |         |  |  |

| 2048x8      | 0-0.6V                                     | 0.87 V   | 77.4 μΑ  | 2.8 ns  | 498 mV              | 79.8 ns  | 92     | 95         | 93      |  |  |

| Distributed |                                            |          |          |         |                     |          |        |            |         |  |  |

| RAM         |                                            |          |          |         |                     |          |        |            |         |  |  |

### IV. CONCLUSIONS

In this research work, MCEB-TCAM is designed and simulated using IC design tools in 90nm technology. After designing MCEB-TCAM at the architectural level, behavioural and functional verifications is made using the Verilog hardware description language of proposed MCEB-TCAM using Cadence is made.

In the proposed Search Register method, at the block level all the pixel values of image are analyzed and bit level extraction is performed. At the design level, the image of 8 bits are applied through genetic apices to extract the maximum number of features values to learn the system. At the simulation level, the learned features are tested with the images, to identify the features to be allocated to those tested images. The proposed MCEB-TCAM design allocates a variable bias voltage power for image feature search based on content matching and the number of mismatched bits are analyzed. In content matching, search and TCAM model operations utilizes very less power of total 0.2 bias voltage, for a power reduction to improve the clock speed performance. The suggested MCEB-TCAM design can be implemented in a 256K word x 576-b MCEB-TCAM for a 90nm 1.2-V CMOS logic process, for a 3.5 ns search time on 8Mbit MCEB-TCAM word, the proposed design utilizes minimum 50% less power comparatively with other distributed RAM's

# REFERENCES

S.Bhargav Kumar " A Survey and an Approach for Content-Addressable Memory Design Based Fast Image-Feature Learning System " IOSR

- Journal of VLSI and Signal Processing (IOSR-JVSP), vol. 9, no. 4, 2019, pp. 01-05.

- S. D. Kumar and N. M. Sk, "A Novel Ternary Content-Addressable Memory (TCAM) Design Using Reversible Logic," 2015 28th International Conference on VLSI Design, Bangalore, 2015, pp. 316-320.

- P. Junsangsri, F. Lombardi and J. Han, "A memristor-based TCAM (Ternary Content Addressable Memory) cell," 2014 IEEE/ACM International Symposium on Nanoscale Architectures (NANOARCH), Paris, 2014, pp. 1-6.

- S. Jayashree and N. Shivashankarappa, "Deep packet inspection using ternary content addressable memory," International Conference on Circuits, Communication, Control and Computing, Bangalore, 2014, pp. 441-447.

- K. P. Gnawali, S. N. Mozaffari and S. Tragoudas, "Low Power Spintronic Ternary Content Addressable Memory," in IEEE Transactions on Nanotechnology, vol. 17, no. 6, pp. 1206-1216, Nov. 2018.

- A. F. Fonseca, D. L. Willian, T. R. B. S. Soares, L. G. C. Melo and O. P. V. Neto, "CAM/TCAM NML: (Ternary) content addressable memory implemented with nanomagnetic logic," 2017 30th Symposium on Integrated Circuits and Systems Design (SBCCI), Fortaleza, 2017, pp. 174-179.

- K. Lee, G. Ko and J. Park, "Low Cost Ternary Content Addressable Memory Based on Early Termination Precharge Scheme," 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 2019, pp. 1-4.

- 8. M. A. Foysal, M. Z. Anam, M. S. Islam, I. Tahmid and K. Mondal, "Performance analysis of ternary content addressable memory (TCAM)," 2015 International Conference on Advances in Electrical Engineering (ICAEE), Dhaka, 2015, pp. 105-108.

- W. Choi, K. Lee and J. Park, "Low Cost Ternary Content Addressable Memory Using Adaptive Matchline Discharging Scheme," 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, 2018, pp. 1-4.

Journal Website: www.ijitee.org

- H. Riaz, A. A. Bhatti, M. A. Tahir and M. Sarwar, "High speed content addressable memory with reduced size and less power consumption," 2016 International Conference on Design and Technology of Integrated Systems in Nanoscale Era (DTIS), Istanbul, 2016, pp. 1-6.

- M. Irfan and Z. Ullah, "G-AETCAM: Gate-Based Area-Efficient Ternary Content-Addressable Memory on FPGA," in IEEE Access, vol. 5, pp. 20785-20790, 2017.

- A. Ahmed, K. Park and S. Baeg, "Resource-Efficient SRAM-Based Ternary Content Addressable Memory," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 25, no. 4, pp. 1583-1587, April 2017.

- M. A. Bahloul et al., "Design and analysis of 2T-2M Ternary content addressable memories," 2017 IEEE 60th International Midwest Symposium on Circuits and Systems (MWSCAS), Boston, MA, 2017, pp. 1430-1433.

- 14. S. Tabassum, F. Parveen and A. B. M. H. Rashid, "Low power high speed Ternary Content Addressable Memory design using 8 MOSFETs and 4 memristors - hybrid structure," 8th International Conference on Electrical and Computer Engineering, Dhaka, 2014, pp. 168-171.

- 15. Md. Hameed Pasha and S.Bhargav Kumar, "A Novel Genetic Apices based Power Estimation for a Distinctive Analog IC Design" ICRSTEM 2019:: International Conference on Research Trends in Science, Technology, Engineering & Management, at Jayamukhi Institute Of Technological Sciences, JNTU Hyderabad, Narsampet on 10 May 2019.

- J. Sorin, "Low-Power Content Addressable Memory," in Computer, vol. 51, no. 3, pp. 8-9, March 2018.

- 17. A. Gangadhar, R. R. Sirisha and K. Babulu, "Implementation of content addressable memory with high speed and low power consumption," 2015 Conference on Power, Control, Communication and Computational Technologies for Sustainable Growth (PCCCTSG), Kurnool, 2015, pp. 230-233.

#### **AUTHORS PROFILE**

Mr. S.Bhargav Kumar working as Assistant Professor in Sridevi Women's Engineering College, Hyderabad. Having 12 years of teaching experience (UG & PG) in engineering colleges and 2 years of experience as a trainer for project trainees. Completed B.Tech. in Electronics & Communication Engineering (ECE) and M.Tech. in Very-large-scale integration (VLSI) System Design (VLSISD) from

Jawaharlal Nehru Technological University Hyderabad, affiliated colleges. Also holds M.B.A. in Human Resource (HR) from Indira Gandhi National Open University (IGNOU), New Delhi. Published more than 15 papers in National & International Conferences and Journals. Trained on MATLAB and Simulink, and Open educational resources (OER). Having Life Time ISTE Membership. Research areas of interest are Machine Learning Systems, VLSI Low Power Design, Image Analysis and Biomedical Signal Analysis.