# Simulation and Implementation of Single Phase Quasi Z-Source Series Resonance DC DC Converter for Photovoltaic Application

### Laxmi Balappa Bavage

Abstract: The paper presents quasi-Z source series resonant dc-dc converter with high performance for PV applications. Their multimode operation property features wide input voltage and load regulation range. Multimode operation achieved by pulse width modulation and phase shift modulation which gives boost and buck operating modes. Paper includes experimental setup which ensures 13volts ripple free output voltage.

Keywords: DC-DC converter, module-level power electronics (MLPE), module-integrated converter, quasi-Z-source (qZS) converter, renewable energy, resonant converter, photovoltaic (PV)

#### I. INTRODUCTION

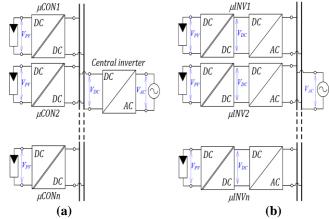

Solar photovoltaic (PV) installation is increased in residential by decreasing PV modules cost and fee-in-tariff system. All PV systems connected to grid. Single PV module integration is used for residential and smart grid application. There are numerous designs of the PV microinverter. Nonisolated, i.e. transformerless topology is simple and commonly used for low voltage. For high voltage applications isolation transformer is used for grid level voltage matching. Later, galvanic isolation is used in single and two stage topologies with addition system of maximum power point tracking (MPPT). After that number of soft switching topologies is proposed for PV module integrated converter. Resonant soft switching is modern trend used for superior results in PV application. Module Level Power Electronics have many applications in photovoltaic system. Module level power electronics devices are incorporated into solar PV system to improve its performance in certain conditions. PV modules are connected with microconverter and microinverter. DC DC microconverter connected to the PV panel for tracking MPP locally. Microinverter connected to grid side allows parallel connection of PV to grid. A two-stage topology is used, which consists of a boost converter and a SRC (Series Resonant converter). The boost converter steps the changing PV voltage Vpv to an intermediate constant voltage bus V<sub>dc,mid</sub>. A DC-to-DC converter is an electronic circuit which converts a source of direct current (DC) from one voltage level to another. The DC output voltage is controlled by varying duty cycle.

Revised Manuscript Received on August 30, 2020.

\* Correspondence Author

Laxmi Balappa Bavage, Student, Department of Electrical Engineering, AISSMS IOIT, Pune, India.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC BY-NC-ND license (<a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>)

Fig 1.(a) common dc bus and microinverters (μINV) (b) grid-side connection.

To improve the performance, many modifications were done to the baseline Quasi-Z-Source Series Resonant Dc-Dc Converter (qZSSRC). To reduce the conduction losses in the input stage of the converter, the synchronous qZS network is implemented. The n-channel MOSFET is placed instead of the diode and is synchronized with the inverter switches such that it conducts only during the active states of the inverter. An important modification of the qZS network is a coupled inductor instead of two discrete inductors. Due to this modification of inductor power density of converter is more and there is reduction of ripple in input current of converter. As compared to the baseline qZSSRC, the proposed converter contains the fully integrated series resonant tank at the secondary side (secondary resonance). Voltage Doubler Rectifier is connected to the secondary side. In VDR first capacitors are resonant capacitors and other is buffer capacitor. These capacitors have different voltage and current stresses.

Previous methods are having drawbacks which are overcome in proposed work.

- 1. To reduce conduction losses in input stage of converter.

- 2. To prevent conduction of diode during shoot through state due to capacitor short circuit, MOSFETs are used with some dead time.

- 3. Drawbacks of previous topic are less power density and high ripple in converter. Present topology improves power density and reduce ripple in converter input current.

- 4. In present topology capacitor is used in voltage doubler rectifier, which acts as filter and double line frequency voltage buffer.

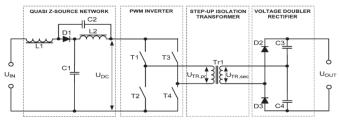

Fig.2 Basic Series Resonant quasi-Z-source DC-DC converter (qZSSRC)

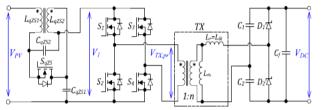

Fig. 3. Quasi Z-source Series Resonant DC-DC Converter

# II. BLOCK DIAGRAM AND OPERATION PRINCIPLE

#### A. Block diagram of proposed system

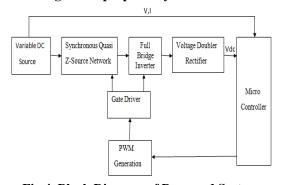

Fig.4. Block Diagram of Proposed System

# B. Operating Principle of Single Phase Efficient QuasiZ-Source Series Resonant DC DC Converter

The converter consists of the qZS network, a full-bridge inverter (S1–S4 ),a step-up isolation transformer and the voltage doubler rectifier. Series resonant tank is formed by leakage inductance of isolation transformer and VDR capacitor. Capacitors in the VDR charged and discharged in parallel manner, forms resonance capacitor with equivalent capacitor Cr.

$$C_r = C_1 + C_2$$

(1)

To improve the performance some modifications are done is basic qZSSRC which are mentioned in chapter 1 introduction. For wide range of input voltage regulation with more efficiency converter operate in multimode. Due to combination of shoot through PWM and ordinary phase shift modulation we get buck and boost operating modes. Input voltage variation range is  $0.5V_{pv}$  to  $1.5V_{pv}$ .

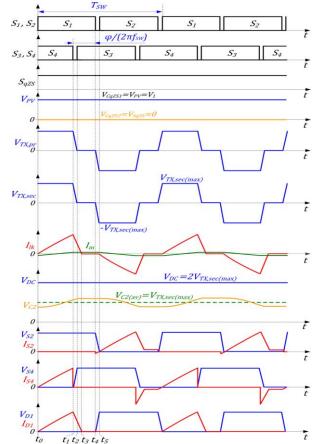

Normal Mode: In this operating point, the duty cycle of the inverter switches is close to 0.5. The switch  $S_{qZS}$  is conducting constantly. Fig.5 shows steadystate waveforms in normal mode of operation. Operation is divided into different time zones. In time  $t_0 < t < t_1$ , switch S1, S4 are turned on and input voltage  $V_{pv}$  applied to the primary winding of the isolation transformer. Switching frequency is equal to the resonant frequency ( $f_{SW} = fr$ ), the current of the  $L_{lk}$  and the

voltage of the parallel combination of C1 and C2 fully resonate, so we get pure sinusoidal waveforms. As switching frequency and resonant frequency is same, at t1 current is zero and switch S1,S4 and VDR diode D1 gets off. But relatively small magnetizing current present in S1,S4 switch. At time  $t_1 < t < t_2$ , switch S1,S4 off and there is dead-time of the inverter. Output capacitance of S1,S4 charges and of S2,S3 discharges due to magnetizing inductance of isolation transformer. Magnetizing inductance and dead time must set properly so at  $t_2$ , switch S2,S3 turned on at zero voltage switching condition. Dead-time is large enough to discharge the capacitor. The average voltage of VDR capacitors is half the output voltage and voltage ripple given by,

$$\Delta V_{\text{cc(normal)}} = P.T_{\text{SW}}/4.V_{\text{DC}}.Cr$$

(2)

Gain in normal mode is given by expression,

$$G_{\text{normal}} = V_{\text{DC}}/2 \text{ n.} V_{\text{PV}}$$

$$= 1 \tag{3}$$

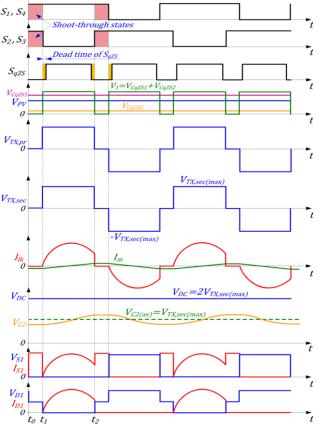

Buck Mode: Converter operates in buck mode when input voltage is higher than predefined nominal voltage. In buck mode, output voltage is controlled by phase shift modulation at resonant frequency. Gain is depends on the phase shift angle and quality factor. Fig.6 shows steadystate waveforms in buck mode.

In time  $t_0 < t < t_1$ , switch S1, S4 are turns on and input voltage gets applied to primary of isolation transformer. The current of the  $L_{lk}$  and the voltage of the parallel combination of C1 and C2 fully resonate and magnetizing current increases to its maximum value.

At time t<sub>1</sub><t<t<sub>2</sub>, switch S4 off with zero voltage switching and converter in dead time. Resonance is suddenly interrupted but current present in the leakage and magnetizing inductance of transformer. Therefore, output capacitance of S3 discharges and S4 output capacitance is charges. Due to this at t2, ZVS turns on S3. During t<sub>2</sub><t<t<sub>3</sub>, switch S3 is on and converter comes in zero state. Zero state is due to short circuiting of primary of isolation transformer by top switches of inverter S1,S3. Transformer voltage is zero but current is unchanged. In time duration t<sub>3</sub><t<t<sub>4</sub>, leakage inductance current becomes zero and converter goes in discontinuous conduction mode at t<sub>3</sub>. Power does not transfer from input side to output side. In t<sub>4</sub><t<t<sub>5</sub>, S1 turns off near combination of zero current switching and zero current switching (due to magnetizing current), and converter into dead time at t4. Due to magnetizing current output capacitance of S1 charges and output capacitance of S2 discharges and body diode of S2 conduct. Diode conduction results in ZVS which turns on S2 at t5. After t5 converter goes in negative half cycle and negative V<sub>pv</sub> to the primary of isolation transformer. Gain in buck mode is given by expression,

$$G_{\text{buck}} = V_{\text{DC}}/2.\text{n.}V_{\text{PV}}$$

$$=0.5 \left[ A \left( \frac{2}{\pi \cdot Q} - 1 \right) + \sqrt{\left( \frac{2}{\pi \cdot Q} - 1 \right)^{2}} \cdot A^{2} + A \cdot \frac{8}{\pi \cdot Q} \right]$$

(4)

Published By: Blue Eyes Intelligence Engineering and Sciences Publication

Retrieval Number: J74980891020/2020©BEIESP DOI: 10.35940/ijitee.J7498.0891020

Journal Website: www.ijitee.org

Boost Mode: The converter operates in boost mode when input voltage is less than predefines voltage value. When shoot through state is generated output voltage controlled by PWM. Shoot through state is generated by symmetrical overlap of active states. By increasing the duty cycle more than 0.5 shoot through state is generated. Switching frequency is same as resonant frequency. In shoot through all switches conduct simultaneously gives dc voltage gain and is shootthrough state time duration. Here dead time is not present in inverter. Steadystate waveforms in boost mode are as shown in fig.7.

In time duration  $t_0$ <t<t1, at  $t_0$ , for shoot through state all switches of an inverter turned on. Before t0  $S_{qzs}$  is turned off and its body diode is reverse biased. During shoot through state current in the qzs inductor increases linearly to its maximum value.

At t1, switch S2,S3 are turned off. After dead time synchronous switch  $S_{qzs}$  is turned on and begins active state. Switches S1,S4 are conducting which are diagonal switches and from qzs network we get stepped up voltage which is applied to primary of isolation transformer.

$$V_{TX,pr(max)} = V_{CqZS1} + V_{CqZS2}$$

(5)

The current of the  $L_{\rm lk}$  and the voltage of the parallel combination of C1 and C2 are resonating. Inductor current of quasi z source network reduces to minimum.

At  $t_2$ , switch S2,S3 are on and  $S_{\rm qzs}$  turned off. Resonance is finished and converter is in second shoot through state same as  $t_0$  to  $t_1$ . Switches are hard switched in boost mode and VDR diode operates under ZCS condition. To prevent circuit damage due to simultaneous conduction of inverter switches and synchronous switch during shoot through dead time is given before turn on and off  $S_{\rm qzs}$ . Body diode of  $S_{\rm qzs}$  conducts during dead time. Due to this dead time interval circuit shift from shoot through state to active state safely.

Voltage gain in boost mode depends on shoot through duty cycle  $D_{st}$ .

$$G_{boost} = V_{DC}/2.n.V_{PV}$$

=1/(1 - 2D<sub>ST</sub>) (6)

Fig.5.Steady-state waveforms operating in the normal mode

Fig.6 Steady-state waveforms operating in the buck mode

Fig.7 Steady-state waveforms operating in the boost mode

Retrieval Number: J74980891020/2020©BEIESP DOI: 10.35940/ijitee.J7498.0891020

Journal Website: <u>www.ijitee.org</u>

#### III. SIMULATION AND EXPERIMENTAL RESULTS

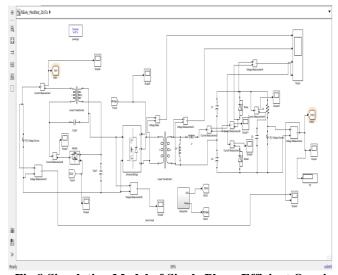

#### A. Simulation Model of Proposed System

Fig.8 Simulation Model of Single Phase Efficient Quasi Z-Source Series Resonant DC DC Converter

Fig.9 Constant value of Output voltage in Buck mode when Input is 25volts

Fig 10 Constant value of Output voltage in Boost Mode when Input is 5volts

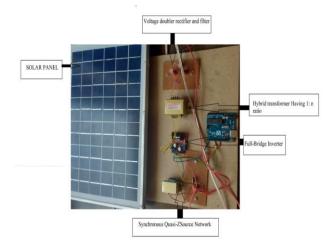

B. Hardware Setup

Journal Website: www.ijitee.org

A prototype of the Resonant QZS is implemented is as shown in Fig. 11. Experimental parameters are the same and are tabulated in Table I.

Fig.11. Hardware Model of Proposed System

**Table- I: Circuit Parameters**

| Tuble 1. Circuit I arameters                       |                |  |  |

|----------------------------------------------------|----------------|--|--|

| Component                                          | Specifications |  |  |

| S <sub>1</sub> - S <sub>4</sub> , S <sub>qzs</sub> | IRF540         |  |  |

| $D_1, D_2$                                         | 1N4007         |  |  |

| $C_{qzs1}$ , $C_{qzs2}$                            | 1000 μF        |  |  |

| $C_1, C_2$                                         | 1000 µf        |  |  |

| $L_{1k}$                                           | 10 mH          |  |  |

Table- II: Name of the Table that justify the values

| Modes             | Normal    | Виск      | Boost         |

|-------------------|-----------|-----------|---------------|

| INPUT<br>VOLTAGE  | 15volts   | 5VOLTS    | 25VOLTS       |

| OUTPUT<br>VOLTAGE | 13.4volts | 13.4volts | 13.4<br>VOLTS |

### IV. CONCLUSION

The prototype model is designed for the PV MLPE applications. In this paper we achieved wide range of input and voltage regulation. This is done by multimode operation of converter and synchronous qZS network and series resonant tank integrated. In proposed hardware, high efficiency is achieved due to VDR diode. The proposed prototype is designed in voltage range of 15volts. Output of prototype is constant at any variation in input. In testing of hardware input range is varied between 0volts to 40volts. Prototype consist silicon MOSFET and schottky barrier diodes for high efficiency.

#### REFERENCES

- S. B. Kjaer, J. K. Pedersen, and F. Blaabjerg, "A review of single phase grid-connected inverters for photovoltaic modules," IEEE Trans. Ind. Appl., vol. 41, no. 5, pp. 1292–1306, Sep./Oct. 2005.

- Andrii Chub, Dmitri Vinnikov, "Single-Switch Galvanically Isolated Quasi-Z-Source DC-DC Converter" in IEEE 5th International Conference on Power Engineering, Energy and Electrical Drives, 2015

- L. Liivik, A. Chub, D. Vinnikov, and J. Zakis, "Experimental study of high step-up quasi-Z-source DC-DC converter with synchronous rectification," in Proc. 9th Int. Conf. Compat. Power Electron., Jun. 24–26, 2015, pp. 409–414.

- L. Liivik, A. Chub, J. Zakis, and I. Rankis, "Analysis of buck mode realization possibilities in quasi-Z-source DC-DC converters with voltage doubler rectifier," in Proc. IEEE 5th Int. Conf. Power Eng. Energy Elect. Drives, May 11–13, 2015, pp. 1–6.

- Vinnikov and I. Roasto, "Quasi-Z-source-based isolated DC/DC converters for distributed power generation," IEEE Trans. Ind. Electron., vol. 58, no. 1, pp. 192–201, Jan. 2011.

- L. Liivik, D. Vinnikov, and T. Jalakas, "Synchronous rectification in quasi- Z-source converters: Possibilities and challenges," in Proc. IEEE Int. Conf. Intell. Energy Power Syst., Jun. 2–6, 2014, pp. 32–35...

- D. Vinnikov, A. Chub, I. Roasto, and L. Liivik, "Multi-mode quasi-Z-source series resonant DC/DC converter for wide input voltage range applications," in Proc. IEEE Appl. Power Electron. Conf. Expo., Mar. 20–24, 2016, pp. 1–7.

- 8. Book "Power Electronics" by P.S. Bhimra

#### **AUTHORS PROFILE**

Laxmi Bavage received the Bachelor degree in electrical engineering from Jaywantrao Sawant College of engineering, Pune, India in 2017 and appearing for Master degree in electrical engineering specialization in power electronic and drive from All India Shri Shivaji Memorial

Society's Institute of Information Technology, Pune, India. Her research interests include Power converters.

Retrieval Number: J74980891020/2020©BEIESP DOI: 10.35940/ijitee.J7498.0891020 Journal Website: www.ijitee.org