# CMOS-NAND Based Gate Driver Card of IGBT for Fault Diagnosis in VSI

Sonali. C. Rangari, Gunwanti. S. Shende, Mohan. M. Renge

Abstract: In industrial application, over loading condition, short circuit is the dominant fault in the motor drives. There are many reasons for the fault but due to this insulated gate bipolar transistor (IGBT) gets damaged which affect the whole system. Protecting IGBT and hence protecting motor drive system at fault condition is the crucial and insistent part of the protection. The short circuit and open circuit fault in an IGBT can be detected by several techniques. The paper presents an idea to deals with the short circuit fault such as fault under over load condition in the typical applications like winder machine. In this paper both the fault diagnosis and clearance of the fault are done. Fault diagnosis is based on the voltage between the collector and the emitter (VCE) of the IGBT which can be done by actual short circuit between these points in the simulation. Voltages of healthy and faulty condition are analyzed. In the fault clearance, CMOS-NAND based circuitry is used called EH10 card for inverter. It shows that this card has ability to detect the fault across the switch and give the signal to microcontroller for its clearance by making GATE signal of the IGBTs zero. This protection of Inverter using realization of CMOS-NAND based GATE driver card is verified using MATLAB simulation results.

Keywords: Voltage Source Inverter, Short Circuit Fault, IGBT fault Diagnosis, EH10 card.

#### I. INTRODUCTION

As the technology grows there is a notable advancement in the world of power semiconductor switches. The IGBT (Insulated Gate Bipolar Transistor) has several advantages over other semiconductor switches. It is commonly used in high power application in the industrial drives. There are many conditions when short circuit fault is occurred in the industrial motor drive. However, one of the main causes of the damage is the IGBT switch in the inverter circuitry. Hence, the fault occurred in the IGBT can be in two cases: Hard Switching Fault (HSF) and Fault under Load (FUL). In HSF, the short condition occurred when the device is shorted with the DC limb, whereas in FUL, the device is shorted in

Revised Manuscript Received on August 30, 2020.

\* Correspondence Author

**Sonali. C. Rangari** \*, department of electrical engineering, Shri Ramdeobaba College of engineering and management, Nagpur, India. E-mail: <a href="mailto:rangaris@rknec.edu">rangaris@rknec.edu</a>

**Gunwanti. S. Shende**, department of electrical engineering, Shri Ramdeobaba College of engineering and management, Nagpur, India. E-mail: <a href="mailto:shendegunwanti21@gmail.com">shendegunwanti21@gmail.com</a>

**Mohan. M. Renge**, department of electrical engineering, Shri Ramdeobaba College of engineering and management, Nagpur, India. E-mail: <a href="mailto:rengemm@rknec.edu">rengemm@rknec.edu</a>

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/)

on - condition. The behavior of the FUL fault is more severe than the HSF [7]. For example, in a single leg of a three phase inverter, when FUL short circuit condition is incident on the upper side then the lower IGBT will be defined as having HSF condition.[6]. The gate driver circuits are designed to protect the IGBTs. This gate driver circuit gives power amplification at the time of switching the devices. The driver circuits are also designed to generate the turn-off signals for the controller which intended to stop the healthy PWM pulses, once the fault has occurred. This paper presents the realization of such gate driver card (EH10) which operates in a same fashion. The decision of the fault condition is taken on the basis of the voltage across the collector and the emitter of the individual IGBT within the inverter circuitry. However, the decision to continue the Load or not can be taken on the basis of the change in voltage due to short circuit in each switch of the inverter [9]. The basic scheme of the overall gate driver circuit is based on receiving the SPWM pulses from the main controller of the motor driver unit. The electrical isolation is provided to the gate driver circuit using opto-couplers. Further, the SPWM pulses are given to the gate of IGBT through the EH10 card. If short circuit fault is occurred then the circuit designed to detect the fault in the inverter. The fault signal is feedback to the Micro-controller to interrupt the healthy SPWM pulses. This sensed fault signal is again isolated by another opto-coupler and hence, the gate pulses are stopped for all the switches of the inverter. Thus, the outputs of the inverter become zero and fault condition is resolved.

## II. METHODOLOGY

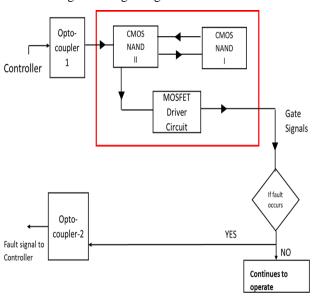

The presented algorithm is based on the circuit having two CMOS-NAND ICs to process the pulses coming from the first opto-coupler. The card itself has ability to detect the fault within the inverter circuit by analyzing the voltage across each switch. If the fault occurs at any switch at any instance, the detection circuit senses the fault and gives feedback to the controller to stop the healthy pulses through second opto-coupler. The controller then blocks the healthy pulses for all switches. The fault detection logic is the decision-making logic whether SPWM pulses have to be continued or not. On the basis of the schematic diagram as shown in fig.1, starting from the controller, the pulses of 1 V is given at the cathode pin of first opto-coupler. Further, the pulses are process through the CMOS NAND ICs. The NAND ICs are used to generate the pulses for two different purposes i.e. to drive the MOSFET driver circuit and to keep

the fault detection circuit continuously on till the motor drive system is in operation.

Retrieval Number: J75830891020/2020©BEIESP DOI: 10.35940/ijitee.J7583.0891020

Journal Website: www.ijitee.org

# CMOS-NAND Based Gate Driver Card of IGBT for Fault Diagnosis in VSI

The MOSFET driver circuit is used to give the higher switching frequency and power amplification for the gate switching. At the terminal of the gate pulses, basic protection is given to deal with heavy current spikes with help of resistors. Now, if the short circuit fault occurs on any of the IGBT of the inverter, the voltage across the switch is sensed. Depending on the voltage VCE, fault signal is generated and given to the opto-coupler-2. This signal is transferred to the controller as a fault signal by the opto-coupler-2 and the pulses for all the switches are stopped. The CMOS NAND ICs are used to operate on higher voltage range so this circuit is used for higher voltage range.

Fig. 1. Schematic diagram of the gate driver circuit

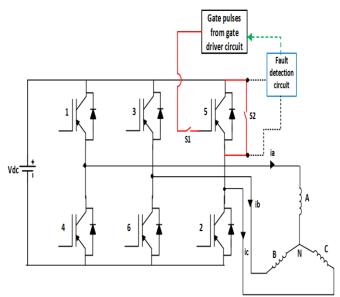

To realise the defined algorithm, it can be implemented in the inverter circuit. Referring to the fig. 2, gate pulses are given to the IGBT through switch s1 from the driver circuit. To create the fault switch s2 is closed. The voltage across collector and emitter of the IGBT is sense by the fault detector circuit. The fault detector circuit has NPN transistor and RC circuit to judge the fault situation. In driver circuit, NAND ICs are implemented in such a way that it give always high pulse to the base of the transistor and the voltage across the switch is applied to the collector the transistor while emitter of the transistor is grounded. Thus, the voltage across the transistor is given to the RC circuit to filter out the pulsed voltage across the switch. The capacitor voltage is kept on charging and discharging till the switch is healthy. If s2 then the switch get short and voltage across the switch is zero. This led to discharge the capacitor to zero volts. Here the fact comes into the picture that, every switch has its ON state transition voltage which keeps it on: if the capacitor voltage falls below that on state voltage then the octo-coupler gives the high signal at fault pin of the Micro-controller.

The fault detection circuit involves the RC circuit, hence for fault detection requires some time. The time constant for the RC circuit for higher voltages will be more as it depends on the supply voltage of the Inverter. Here the inverter is supplied by the 100 V supply and the load is considered as the RL load, where R=  $10\Omega$  and L=23 mH. The on- state transition voltage for the IGBT is considered as 4 V, that means whenever the fault is there, the voltage across the IGBT becomes zero and the voltage across capacitor falls

below 4 V, as soon as the voltage falls below the 4 V comparator gives high pulse to the octo-coupler-2. And the controller receives fault signal. As the current capacity of the IGBT increases, the on- state transition voltage for the IGBT will also increase. Hence, this logic for the fault detection can be applied for different value of on-state transition voltage provided that the RC time constant has to be designed for that value to detect the fault. And stop the system as early as possible. The RC circuit will increase components of circuitry and cost too.

Fig. 2. Schematic diagram of the implemented circuit in thr inverter system.

Usually, in healthy condition, the gate pulses for the switches are derived by the comparing the sine wave and the triangular carrier wave. But during fault condition, the gate pulses for the IGBTs should be stopped i.e if s2 is closed then s1 should be open (refer Fig.2). This scheme is applied to all switches of the inverter so that the output of the inverter becomes zero. To do so, one method can be implemented that making no comparison of sine wave and the triangular carrier wave.

### III. SIMULATION RESULTS

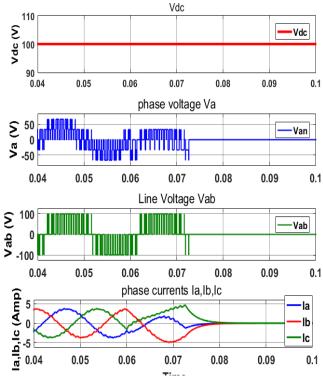

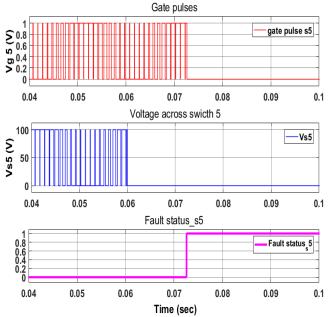

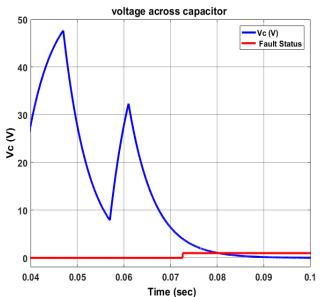

Now, by creating the fault on the switch 5 of the inverter following results are obtained. The Fig. 3 (a) shows the result of input voltage of the inverter Vdc, and output of inverter such as phase voltage Van, line voltage Vab, and phase currents of the inverter. Fig.3 (b) gate pulses of switch 5, voltage across the switch 5, fault status of switch 5. And Fig.3(c) shows the Voltage across the capacitor of fault detector circuit. Fig.3 shows the results before and after the fault situation. The fault occurred on switch 5 at the instance of 0.06 sec, it can be observed from the Fig. 3 (b) the gate pulses of the switch 5 becomes zero after 14 msec after the fault occurrence. Therefore, we can conclude that the fault condition can be detected by the controller after 14 msec of the occurrence. This fault detection time depends upon the capacitor value and the time constant of the RC circuit used for the filtration of the pulsating voltage across the switch as shown in Fig 3(c).

Retrieval Number: J75830891020/2020©BEIESP DOI: 10.35940/ijitee.J7583.0891020 Journal Website: www.ijitee.org

Fig. 3(a). Inverter output (Phase voltage Va, Line voltage Vab, current of three phases Ia,Ib,Ic)

Fig. 3(b). Gate pulses, voltage across switch, fault status of switch 5

Fig. 3(c). Voltage across Capacitor of fault detection circuit and fault status

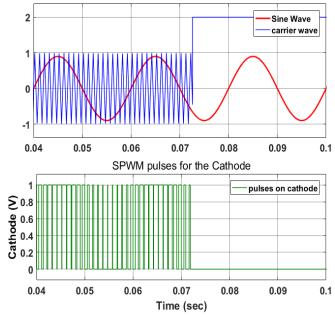

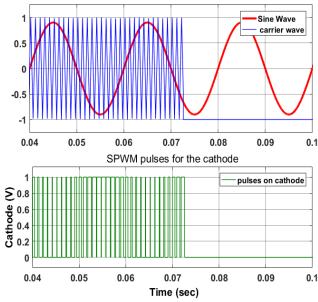

The modulation for the upper switch and the lower switch is designed in such a way that if fault occurs on any of the switch then carrier wave for the upper switch will become constant at greater value than the amplitude of the sine wave here it is taken as 2. Hence, there is no comparison and resulting pulses becomes zero as shown in Fig 4(a). Similarly, the carrier wave for the lower switch will become constant at lower value say -1 than the negative amplitude of the sine wave. And there is no comparison between sine wave and triangular carrier wave.

Fig. 4(a). SPWM pulses for the upper switches of the inverter

# CMOS-NAND Based Gate Driver Card of IGBT for Fault Diagnosis in VSI

Fig. 4(b). SPWM pulses for the lower switches of the inverter

#### IV. CONCLUSION

Simulation result shows that CMOS-NAND Based EH10 card is very effectively diagnosed the fault and gives the signal to Microcontroller. As the Microcontroller sense the fault, it stops the pulses to the IGBT. Hence, the VSI isolates the load from the supply. With this further damage to the other system can be secure. With the removal of VSI, damaged IGBT can be replaced & hence the whole system can be restored for the further task.

## REFERENCES

- E. Flores, A. Claudio, J. Aguayo, L. Hernández "Fault Detection Circuit Based on IGBT Gate Signal"IEEE LATIN AMERICA TRANSACTIONS, VOL. 14, NO. 2, FEB. 2016

- Vijay Bolloju, Jun Yang, "Influence of Short Circuit conditions on IGBT Short circuit current in motor drives," 978-1-4244-8085-2/11/\$26.00 ©2011 IEEE

- Marjan Alavi1. Ming Luo, Danwei Wang, Haonan Bai, "IGBT Fault Detection for Three Phase Motor Drives using Neural Networks", IEEE conference 2016

- Fuhrmann, J., Eckel, H.-G., & sebstian Klauke, "Short-circuit behavior of series-connected high-voltage IGBTs", 2016 18th European Conference on Power Electronics and Applications (EPE'16 ECCE Europe). doi:10.1109/epe.2016.7695445

- Chuannuo, X., Xuezhen, C., & Tongqing, Z "An Analysis Model and Test Monitoring Device for IGBT Intermittent Fault", 2020 5th International Conference on Control and Robotics Engineering (ICCRE). doi:10.1109/iccre49379.2020.9096472

- Min-Sub Kim, Byoung-Gun Park, Rae-Young Kim, and Dong-Seok Hyun "A Novel Fault Detection Circuit forShort-circuit Faults of IGBT", 978-1-4244-8085-2/11/\$26.00 ©2011 IEEE pp- 359-363, 2011.

- Salvatore Musumeci, Rosario Pagano, Angelo Raciti, Leonard0

Fragapane, Maurizio Melito " Experimental Investigation On The

Short Circuit Behaviors of Robust IGBT Devices " Fourth IEEE

International Caracas Conference on Devices, Circuits and Systems,

Aruba, April 17-19, 2002

- A. Bhalla, S. Shekhawat, J. Gladish, J. Yedinak, G. Dolny "IGBT Behavior During Desat Detection and Short Circuit Fault Protection" Proceedings of 1998 International Symposium on Power Semiconductor Devices & ICs, Kyoto.

- S. Mohsenzade, M. Zarghany, and S. Kaboli "A Series Stacked IGBT Switch with Robustness against Short Circuit Fault for Pulsed Power Applications" DOI 10.1109/TPEL.2017.2712705, IEEE Transactions on Power Electronics.

- Rahul Chokhawala and Guissepe Castino,"IGBT fault current limiting circuit", IEEE industry magazine September/October 1995

#### **AUTHORS PROFILE**

**Dr. Sonali C. Rangari** is currently working as Assistant professor in Electrical Engineering Department, Shri Ramdeobaba College of Engineering and Management, Nagpur. She was received her B.E.degree in Electrical Engineering in 2002 from Nagpur University, the M.Tech. degree in Integrated Power System from Visvesvaraya National Institute of Technology Nagpur in

2008, and the Ph.D. degree from the Department of Electrical Engineering, Visvesvaraya National Institute Of Technology Nagpur, in 2018 in the area of Multiphase Induction Motor.

**Gunwanti Shende** is PG scholar in the stream of electrical engineering having branch specialization of power electronics and power system, she receives Bachelor Degree in electrical engineering in the year 2017. During the academic year she have publications in the journal of Helix the scientific explorer and IJSRST respectively.

**Dr. Mohan M. Renge** received the M.E. degree in electrical engineering from the Walchand College of Engineering, Sangli, India, in 1988, and the Ph.D. degree from the Visvesvaraya National Institute of Technology, Nagpur, India, in 2010. He is currently a Professor with the Department of Electrical Engineering, Ramdeobaba College of Engineering and

Management, Nagpur, India. His research interests include the electric drives, multilevel converters, and flexible-ac transmission systems devices.

Published By: Blue Eyes Intelligence Engineering and Sciences Publication

Journal Website: www.ijitee.org