# Modeling and Control of Solar PV System with Closed Loop ZVS Resonant SEPIC Converter

S. Saravanan, P. UshaRani

Abstract: This paper pledges with replication and portrayal of a zero voltage switching of SEPIC for the purpose of photovoltaic application. A source of energy is given by photovoltaic panel. A impose capacitor and an supporting switch are coupled. A supporting inductors and combined inductors are second-hand to accomplish ripple less current of input then Zero voltage switching method of the supporting switches with head switch. The dynamic fix strategy and the technique of voltage multiplier are practical to the conventionalist converter of SEPIC to support the addition of voltage, compact down the worries of voltage of the diode and matchless quality switches. Moreover, with utilizing essentialness among the inductor's blasting and voltage multiplier circuit's capacitor, Diode's of output ZCS strategy is accomplished and its inverse recuperation trouncing be broadly consolidated. charge to the power semiconductor gadget's delicate exchanging correspondence and improved the proposed system. The realistic speculative assessment has been affirmed through an example of 80W and 100KHz converter. What's more, determined ability of anticipated converter has been accomplished an expense of 94.8% at the most elevated yield control.

Keywords: ZCS, voltage multplier, ZVS.

## I. INTRODUCTION

The generally SEPIC converters have been used for renewable application of photo voltaic cell and LED lighting is the few of the applications. However, the converter has various downsides. The two primary downsides are less execution in light of hard exchanging activity of intensity switches and power semiconductor's high voltage stress. Extraordinarily, higher evaluated voltage control semiconductor is utilized in high voltage application. The Rds intensity of MOSFET is top when the voltage range is top. In the comparable scale current, this circumstance makes a pinnacle conduction misfortune, and afterward, all in all, skill compartment is improved. The voltage multipliers have been acquainted all together with lessening the voltage stress and lift the voltage gain.

To diminish the weight and volume of the converter, delicate exchanging methods are important. The few of the delicate exchanging methods are ZCS and ZVS. DC-DC converters are the pinnacle recurrence activity that

permits a drop of the weight and volume of their attractive operations. However, electromagnetic obstruction commotions and exchanging unfortunate casualties are significant in the high-recurrence activity. Therefore, unique delicate exchanging strategies have been performed. In them, the energetic cinch technique is over and overworn to bound the voltages stick effectively, achieves delicate exchanging activity and lift the framework capability.

The SEPIC converter is a significant favorable position; it safeguards a less current wave. Then again, a mass inductor must be worn to abridge the present wave. Proper to the abundant use of low voltage sources (batteries, energy units, and super capacitors) input current wave turns into an important necessity. It happens in view of immense wave current could chop down the lifetimes of those key sources.

SEPIC is proposed in Zero-current-exchanging PWM. 2 switches can work among delicate exchanging. All things considered, 3 power diodes and 3 split inductors are utilized. Switch's voltage stress is the expansion of a yield voltage and information voltage which is indistinguishable from the traditionalist SEPIC Converter. Then again, it has vivacious info present and a valuable channel stage is mandatory in the information stage to control the info current wave. Subsequently, a tally of the attractive device can be developed.

In bidirectional zero-voltage-exchanging PWM, SEPIC Converter has been proposed. Fundamental switches of check two can ready to work among delicate exchanging. On the other hand, a bidirectional switch needs 2 power MOSFETs. Furthermore, the switch's voltage stress is indistinguishable from the traditionalist convertor SEPIC. In check, the snubber circuit is obligatory toward limit freeloading voltage murmuring across the bidirectional switches.

A delicate exchanging single-finished essential inductor converter among wave less information current has been presented. A clasp capacitor and a helper switch are extra to the traditionalist single-finished essential inductor converter. Moreover, in the multiplier circuit the abrogate recuperation destruction of yield diode is obviously dense because of essentialness among the capacitor and the resounding inductor. Scholarly assessment is affirmed with a 80W investigational model with 50-202V adjustment.

# Revised Manuscript Received on November 27, 2019.

<sup>\*</sup> Correspondence Author

**S. Saravanan**, Research Scholar, Anna University, Tamilnadu, India. Email: saravanan316@yahoo.com,

**Dr. P. UshaRani,** Professor, Senior member IEEE, EEE Department, RMD Engineering College, Email: pusharani71@yahoo.com

## Modeling and Control of Solar PV System with Closed Loop ZVS Resonant SEPIC Converter

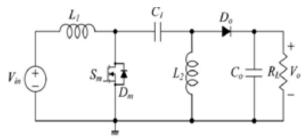

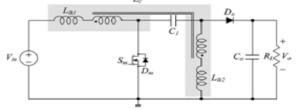

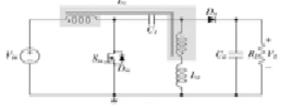

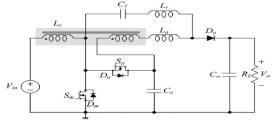

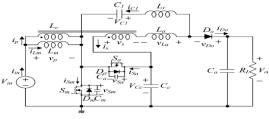

(a) primary inductor converter- Conventional

(b)primary inductor converter with a coupled inductor-Ripple less

(c)primary inductor converter with a coupled inductor tightly -Ripple-less

(d)Planned zvs,zcs switching primary inductor converter-ripple free

(e)proposed converter

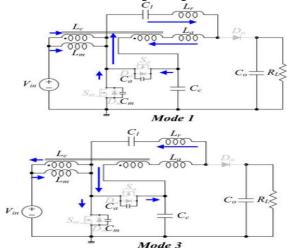

# II. PROPOSED CONVERTER OPRATION

The conventionalist single-finished essential inductor converter is given away in fig(a). The distinction inductor portrayal is given away in fig(b). In the appended inductor depiction, a sadly joined inductor LC is worn in its place of 2 disengage inductors L1 and L2. Llk2 and Llk1 include the getaway inductances of the joined inductor. The joined inductor portrayal has the advantage, for example, solitary magnetic module and a waveless circumstance are connected among the charging inductance, the turn rate, and the leakage inductance Lk2 of the joined inductor. In any case, the leakage inductance Lk1 isn't related to the waveless circumstance. Thus, a safely joined inductor could

be used among a strengthening inductor La as a substitute of Lk2 as appeared in fig(c).

The circuit of the anticipated delicate exchanging single-finished essential inductor converter by method for a waveless information current is given away in fig(d). In the anticipated converter, the ringing inductor Lr and the energetic secure cell hold the Sa and the protected capacitor Cc is further to the traditionalist SEPIC converter given away in fig(c). The journalist circuit of the anticipated converter is given away in fig(e). The joined inductor Lc is generation as the polarizing inductance Lm and a model transformer with a turn portion 1:n. The diodes Dm and Da are the characteristics that remains diodes of the Sm and Sa are actuate unjustly and the obligation part D remains on the Sm. To abbreviate the fixed state examination, it is comprehended that people capacitor C1, Co and Cc have heavy morals and the voltage swells athwart them canister be ignored.

MODE I [to,t1]: the main switch Sa is spined OFF. Thereafter, the power crowd in the attractive hardware, for example, Lr., La and Lm starts to summon Ca and freedom Cm. Therefore, the Vsa transversely Sa beginss to mount from 0 and the Vsm across Sm starts to lessen from Vcc. While the capacitors Cm and Ca are pretty much nothing, the move time space Tt1 is close to nothing. While the move space Tt1 is close to nothing, every current crooked during the attractive hardware are estimated stable through this strategy.

MODE II [t1,t2]: By t1, the Vsm shows up at 0. Thereafter, the corpse diode Dm is abnormal ON. Behind to the door marker is useful to the Sm and the conduit of Sm gains over the current twisted from first to last Dm. Since the Vsm is verified as 0 among contort lying on of Dm in front of Sm is abnormal ON, 0 voltage turn on of Sm is accomplished. The information Vin is useful to Lm and the current Ilm augments every now and again from its least worth ILm2.

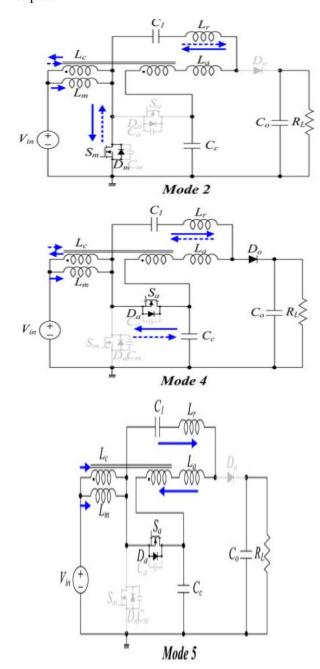

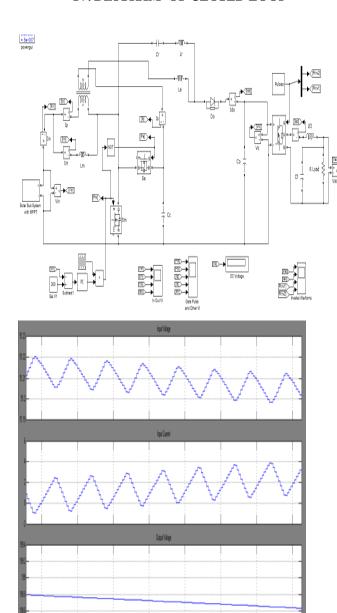

# III. RESULT OF SIMULATION

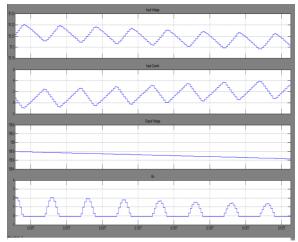

Figure 1. Waveform of output

Figure 2. Inverter performance

MODE III [t2,t3]: The operating switch Sm is slanted OFF on t2. At that point, the voltage v sm broadens from 0 then the V sa decay from Vcc by the indistinguishable time unpaid to the power crowd in the attractive apparatus. The advancement timespan Tt2 canister be disentangling Tt2 is irrelevant. All aspects of the flows are implicit stable all through Tt2.

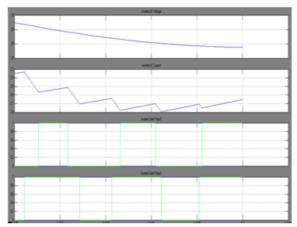

Figure.3 Triggeroing Pulse

*MODE IV* [t3,t4]: the time interval t3 is Vsa shows up at 0. At that point, the remaining parts of diode Da is screwy ON. Behind that, the door pointer is useful to the channel andSa obtains over the current bending during the diode Da.

The voltage Vsa is increase as 0 in front of the switch Sa is bowed ON, zero voltage initiate of Sa is come to. In this methodology, the Vp transversely lm is (Vcc-Vin) and the current ilm decay every now and again from its

most noteworthy worth ilm1. Among the initiate of Sa, the yield diode Do starts to perform. At that point the quality among the ringing inductor Lr and the capacitor C1 comes to pass.

**MODE** 5[t4,t5]:the next time interval t4,the yield diode current  $iD_o$ getting down to 0 and 0 current rotate OFF of diode  $D_o$  is attained. While the current varyingpace of  $D_o$  is prohibited by a ringingmethod, its reverse-recovery dilemma is extensively assuaged. Because the voltage crosswise the  $L_a$  inductor is  $(V_{c1}-nV_{cc}+nV_{in})L_a/(L_a+L_r)$ , the current is raise in this mode.

#### IV. DIAGRAM OF CLOSED LOOP

Figure 4. Waveform of closed loop system

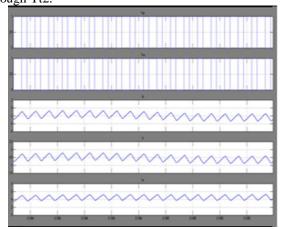

# V. RESULTS OF EXPERIMENTAL

Toward demonstrate the relentless stage routine and the assumed assessment of the anticipated Resonant presentation of SEPIC converter for Renewable application, a research center model is created and solidified with the information (Vin) and yield voltage (Vo) of 50 V and 200 V individually, exchanging recurrence (fs) of 100 kHz and yield control (Po) is 80W.

#### VI. CONCLUSION

The procedure conviction, theoretical assessment, and the usage of a Resonant switching SEPIC for photovoltaic accommodation are realistic in this article. The projecting converter, the assembled with a helper inductor is used to supply swell less info current and achieve zero-voltage-exchanging procedure of assistant switches and the primary. The reward of the anticipated converter is little voltage stresses, small exchanging misfortunes, swell less information current, soothe switch recuperation situation of the yield diode, and taking off ability. The point impression of the anticipated converter is consolidated. The investigational results dependent on a model are reachable for defense.

## REFERENCES

- [1] S.Saravanan, P.UshaRani, "Simulation and Modeling Of SEPIC Converter With High Static Gain For Renewable Application" IEEE international conference (ACEPT) [978-1-5386-0971-2/17/\$31.00 ©2017 IEEE]

- [2] P.UshaRani,S.Saravanan, "Bridgeless Discontinuous Conduction Mode SEPIC Power Factor Correction rectifier", IEEE international conference (ICGCE), pp.594-599, 02 june 2014.

- [3] P. F.Melo, R.Gules, Eand R. C.Annunziato, . F. R. Romaneli, "AmodifiedSEPIC converter for high-power-factor rectifier and universal input voltageapplications," *IEEE Trans. Power Electron.*, vol. 25, no. 2, pp. 310–321, Feb. 2010.

- [4] E. H. Ismail, "Bridgeless SEPIC rectifier with unity power factor andreduced conduction losses," *IEEE Trans. Ind. Electron.*, vol. 56, no. 4,pp. 1147–1157, Apr. 2009.

- [5] D. S. L. Simonetti, J. Sebastian, and J. Uceda, "The factor preregulators: Analysis and design," *IEEE Trans. Ind. Electron.*, vol. 44, no. 5, pp. 630–637, Oct. 1997.

- [6] J.-M. Kwon, W.-Y.Choi, J.-J.Lee, E.-H.Kim, and B.-H. Kwon, "Continuous-conduction-mode SEPIC converter with low reverserecoveryloss for power factor correction," *IET Proc. Electr. Power Appl.*, vol. 153, no. 5, pp. 673–681, Sept. 2006.

- [7] J. C. W. Lam and P. K. Jain, "A high-power-factor single-stage singleswitchelectronic ballast for compact fluorescent lamps," *IEEE Trans. Power Electron.*, vol. 25, no. 8, pp. 2045–2058, Aug. 2010.

- [8] S. J. Chiang, H.-J.Shieh, and M.-C. Chen, "Modeling and control of PV charger system with SEPIC converter," *IEEE Trans. Ind. Electron.*, vol. 56, no. 11, pp. 4344–4353, Nov. 2009.

- [9] L. Qin, S. Xie, and H. Zhou, "A novel family of PWM converters basedon improved ZCS switch cell," in *Proc. IEEE Power Electron.* Spec. Conf.(PESC), 2007, pp. 2725–2730.

- [10] M. Khambadkone, X. Kong and A. "Analysis and implementation of a high efficiency, interleaved current-fed full bridge converter for fuel cell system," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 543–550, Mar. 2007.

- [11] K. Mazumder, ,S. Pradhan, S. J. Hartvigsen, and M. Hollist, "Effects of electrical feedbacks on planar solid-oxide fuel cell," ASME J. Fuel CellSci. Technol., vol. 4, no. 2, pp. 154–166, May 2007

- [12] P. N. Enjeti, ,W. Choi, and J. W. Howze, "Development of an equivalent circuit model of a fuel cell to evaluate the effects of inverter ripple current,"in Proc. IEEE Appl. Power Electron. Conf. (APEC), 2004, vol. 1, pp. 355–361.

- [13] Farzanehfard, "M. Jabbariand"Newresonant step-down/up converters," *IEEE Trans. Power Electron.*, vol. 25, no. 1, pp. 249–256, Jan. 2010.

# **AUTHORS PROFILE**

Mr. S. Saravanan is pursuing of Ph.D in Electrical and Electronics Engineering Department, Anna university, Chennai, India. He has completed his M.E in Power Electronics and Drives in the year 2012 in JERUSALEM college of Engineering, Anna University, Chennai. He has completed his B.E in Electrical and Electronics engineering in the year 2010 in G.U POPE College of Engineering

(tuticorin) Anna University Chennai, India. He has published 4 international journal and 5 international conference (IEEE Xplore-2).He has 7 years of teaching experience.

P. Usha Rani is Professor in Electrical and Electronics Engineering Department, R.M.D Engineering College, Chennai, India. She received her B.E. degree in Electrical & Electronics Engineering from the Government College of Technology, Coimbatore, India, M.E. degree in Power Systems from College of Engineering, Anna University, Chennai, India and Ph.D in the area of Power Electronics and Drives from Anna University, Chennai, India. She has published

over 71 technical papers in international and national journals / conferences proceedings. She has 22 ½ years of teaching experience. Her earlier industrial experience 4 yrs was with Chemin Controls, Pondicherry, India. Her research interests on application of power electronics to power quality problems and FACTS. She is a Senior member of IEEE and life member of Indian Society for Technical education.