# Design of XOR and XNOR Based Full Adder Circuits

## Inumula Veerarahava Rao, Aditya M, V Kavya Chowdary, K Sai Nishitha, V Naveen Sai

ABSTRACT: This paper has a XOR / XNOR gate circuits produces separate and establishes a simultaneous XOR - XNOR function.. Due to stubby yield capacity and short-circuit energy dissipation, the power utilization and latency of these circuits is increasing A new one-bit adder hybrid circuit is chosen built on the effective gates of xor xnor or xor / xnor. Each prefer circuit has its own advantages as it is known for its high speed, low current drain, short delay product (PDP), galvanic ability, etc. Simulations of the planned models were carried out using Mentor Graphics to see the quality of these projects. The simulation results are based on the 130-nm CMOS engineering design. A recent technique of transistor sizing is implemented to improve the circuits ' PDP.

Keywords: Transistor sizing method, PSO, XOR-XNOR, Output driving capability, DPL

## I. INTRODUCTION

Today, predominant electronic systems are treated separately in every part of life and the usage of portable devices has been increased tremendously. These devices require to have less power utilization and high speed. While designing a system, power utilization is a parameter which is to be rectified for better system performance. The efficiency that depends on the execution of divider, comparator, multiplier, and adder which comes under arithmetic circuit which in turn shows the impact on numerous digital applications. In Most of the circuits that perform arithmetic operations, full adder plays a important role, because Total adder output affects the entire process. For algebra, adder loops are used logic circuit designs, processor chips. there are 2 types of full adders in which the circuits are existed till now.

# Revised Manuscript Received on December 30, 2019.

\* Correspondence Author

I.Veeraraghava Rao\*, Department of Electronics and Communication Engineering, Koneru Lakshmaiah Education Foundation, Vaddeswaram, AP, India. raghva.inumula@kluniversity.in

Aditva M, Department of Electronics and Communication Engineering, Koneru Lakshmaiah Education Foundation, Vaddeswaram, AP. India aditya@kluniversity in

V Kavya Chowdary, Department of Electronics and Communication Engineering, Koneru Lakshmaiah Education Foundation, Vaddeswaram, AP, India. kavya24c@mail.com

K Sai Nishitha, Department of Electronics and Communication Engineering, Koneru Lakshmaiah Education Foundation, Vaddeswaram, AP, India. sainishitha99@gmail.com

V Naveen Sai, Department of Electronics and Communication Engineering, Koneru Lakshmaiah Education Foundation, Vaddeswaram, AP, India. naveensaicea@gmail.com.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license <a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>

They are the static and the dynamic full adders. The static full adders is having high reliability and they are simple having low power utilization whereas the dynamic full adders have less on chip area. The designs in the circuits includes the characteristics of enhance the W/L ratio of transistors is one way to reduce the circuit energy lag material while minimizing the problems associated with rising the input voltage. The usefulness of various electronic systems is the output of mathematical loops, such as many adder, multiplier and divider.

### II. XOR AND XNOR GATES ANALYSIS

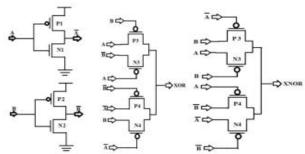

XOR-XNOR CIRCUITS: Using the utilized xor-xnor circuits, new hybrid full adders are proposed. These circuits use different logic styles. Each proposed full adder use simultaneous Xor and Xnor circuits and 2to1 multiplexer structure. The major consumer in the full adder is Xor-Xnor gate. This gate is having many applications in digital circuit design. Hence, The electric energy consumption of the full adder might be reduce by using the optimum design of this xor-xnor gate. Many efficient circuits have been implemented using Xor-Xnor gates. In fig (a) Active XOR/XNOR gate circuit is scrawl designed comprising of 8 transistors. Construction of this circuit is based on double pass-transistor logic (DPL)style. Since it requires Two flexible intake doors not on the loop critical path and also, since these gates (NOT) .The performance power must be powered by the width of the transistors should be increased which becomes a major drawback avoiding the usage of this circuit. In addition to this problem, there comes another one creating an medial node with a very high capacitance. Consequently, this part of the circuit simple terms-circuit capacity and overall power dissipation were extensive. The critical path lag will also be decreased in the optimal PDP scenario. moderately. So, to modify the above circuit i.e Fig.(a). We The XOR / XNOR gate example has been planned for each circuit consisting of six transistors.

## **Critique For Xor And Xnor Gates**

Fig(a) Full-swing XOR/XNOR circuit

# Design of XOR and XNOR Based Full Adder Circuits

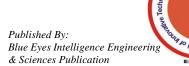

Fig (b) The XOR-XNOR full-swing gate is proposed with a six transistors. The dual additional input transistors (N3 and P3) recovers the faulty logic in output nodes (XOR and XNOR). If AB=00 is the same, 11 outputs are the same.

This loop, though, experiences from either the largest latency in the worse scenario, because once the inputs shift from AB = 01, 10 to AB = 11, 00, the outputs hit their total voltage level in two phases. To discuss the problem, the transistors n2 (xor output) and p2 (xnor output) transfer logic "1" and logic "0" in both when outputs equal to AB = 10. Such poor reaction phenomenon is the worst in minimal-voltage service and also raises quick-circuit current if one of the inputs (XOR or XNOR) is high impedance and the circuit input not yet been fully implemented the flow of the short circuit moves via the device. Even if the transistor scale is not properly chosen by this circuit, the circuit may not always be regulated properly. Fig (c) To address the long wait issue and work in low voltage inputs, two nmos transistors (for AB = 11) and two pmos transistors (for AB = 00) are attached to the XOR / XNORoutputs. The benefits of this design are perfect driving efficiency, full swing performance and robustness toward transistor size and voltage source scaling. Fig (d) It is having 20 transistors and compared to other transistors it is having less power delay. The driving capability is also better than the other circuits.

Fig(b),(c) and (d): XOR/XNOR circuits

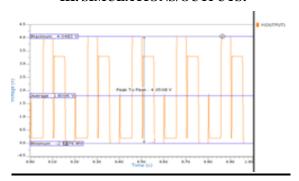

## III. SIMULATIONS/OUTPUTS:

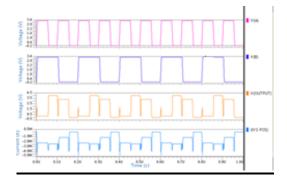

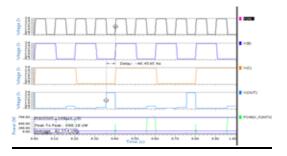

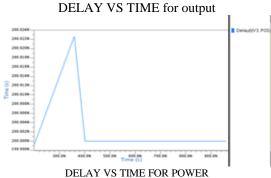

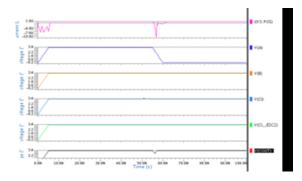

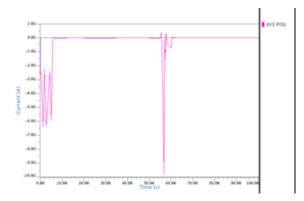

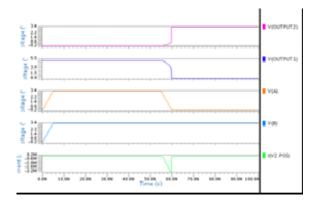

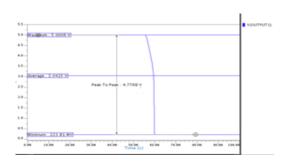

Simulated results of XOR XNOR Gates for Fig (a)

Published By:

& Sciences Publication

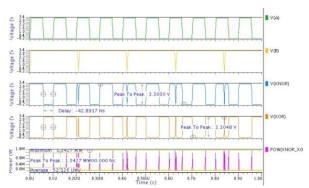

Simulated results of XOR-XNOR Gates for Fig (b),(c),(d)

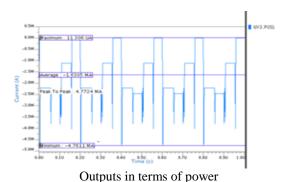

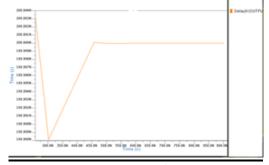

Table for power delay product

| DESIGN | POWER (watts) | DELAY (us) | PDP   |

|--------|---------------|------------|-------|

| Fig(a) | 6.47          | 41.36      | 267.5 |

| Fig(b) | 4.73          | 35.62      | 168.4 |

| Fig(c) | 6.82          | 46.98      | 320.4 |

| Fig(d) | 4.8           | 59.1       | 241.1 |

#### IV. ADVANTAGES

- 1) Circuits based on the Transistor logic type transfer (PTL) introduced which eliminates the problem of excessive power consumption.

- 2) Two transistors have been removed and modified from the XOR-XNOR circuit for through the circuit's energy dissipation.

- 3)To eliminate and the slow response problem and enable the circuits to operate successively, two NMOS transistors and PMOS Transistors are connected separately to XOR and XNOR outputs.

- 4) Occurrence of great driving capacity, maximum-swing performance.

- 5) The question of increasing the size of a transistor and the doubling of the input voltage is over.

- 6) Circuits have high speed also the response time have been reduced.

## V. CONCLUSION:

We initially tested the XOR-XNOR circuits and their characteristics. Also the circuit has a positive feedback on the outputs which results in the increase of the size of transistors, delay, and excessive power consumption making the circuit avoidable. It is the most important components of any software for a digital system. The PDP is a calculation of the increased energy per arithmetic circuit operating period. Different full adder architectures have been reviewed and simulated utilizing mentor graphics 130 nm technology. The CMOS adder offers both logic 0 and logic 1 based on the output comparison of different adders. Also it operates with a extremely high speed an maintains a good accuracy. Simulation results showed us that the proposed circuits have got high speed and energy than the previous ones.

# REFERENCES

- R. Eberhart and Y. Shi, "Particle swarm optimization: Developments, applications and resources," in Proc. Congr. Evol. Comput., vol. 1. May 2001, pp. 81–86.

- M. Aguirre-Hernandez and M. Linares-Aranda, "CMOS full-adders for energy-efficient arithmetic applications," IEEE Trans. Very Large Scale Integr. (VLSI).

- 3. J.-M. Wang, S.-C. Fang, and W.-S. Feng, "New efficient designs for XOR and XNOR functions on the transistor level," IEEE J. Solid-State Circuits, vol. 29, no. 7, pp. 780-786, Jul. 1994.

- Inumula Veera Raghava Rao, "A Novel Low-Power 5th order Analog to Digital Converter for Biomedical Applications", International Journal of Innovative Technology and Exploring Engineering (IJITEE) ISSN: 2278-3075, Volume-8, Issue-6.

- Inumula Veera Raghava Rao, "Object Tracking and Object Behavior Recognition System in High Dense Crowd Videos forVideo Supervision: A Review", Journal of Advance Research in Dynamical & Damp; Control Systems, Vol. 10, 2018.

# Design of XOR and XNOR Based Full Adder Circuits

- Inumula Veera Raghava Rao, "A novel image recognition method using multiple component resemblance score synthesis and genetic algorithm", IOP Conf. Series: Journal of Physics: Conf. Series 1139 (2018) 012069 IOP Publishing.

- Prasad G.R.K., Babu P.S.S., Khan H., Niak K.K., Generation of radiation characteristics from waveguide slot arrays for satellite tracking radar system,2017 INCEMIC 2015 - 13th International Conference on Electromagnetic Interference and Compatibility, Proceedings, pp:276-278, DOI: 10.1109/INCEMIC.2015.8055894, ISBN: 9.78151E+

- Murali A., Hari Kishore K., Rama Krishna C.P., Kumar S., Trinadha Rao A., Integrating the reconfigurable devices using slow-changing key technique to achieve high performance, 2017 Proceedings - 7th IEEE International Advanced Computing Conference, IACC 2017, pp: 530-534, DOI: 10.1109/IACC.2017.0115, ISBN: 9.78151E+12

- Suresh Kumar N., Pavan Kumar K.V.K.V.L., Preetham Reddy C.S., Tirumalasetty V.R., Suman M., A novel region wise random valued impulse noise detection and filtering, 2017 Journal of Advanced Research in Dynamical and Control Systems, Vol. 9, pp. 1983-1991, ISSN: 1943023X

- Prasad G.R.K., Srinivas Babu P.S., Siddaiah N., Srinivasa Rao K., Design and simulation of MEMS based sensor for early detection of PD,2017 2016 International Conference on Electrical, Electronics, Communication, Computer and Optimization Techniques, ICEECCOT 2016,Vol:, issue:,pp: 366-371,DOI: 10.1109/ICEECCOT.2016.7955247,ISBN: 9.78151E+12

- Siva D., Sunithamani S., Bojja P., An automated damage assessment index to quantify damage for disaster management using satellite images,2017 Journal of Advanced Research in Dynamical and Control Systems, Vol:9, issue:1, pp: 407-420, ISSN: 1943023X

- Vasudha M., Pravallika B.S., Kiran C.S., Subhani P., Rakesh Chowdary G., Prakash M.D., Kishore K.H., Ramakrishna T.V., Design and performance analysis of a nonvolatile memory cell,2017 Journal of Advanced Research in Dynamical and Control Systems, Vol:9, issue: Special Issue 14, pp: 2320-2327, ISSN: 1943023X

- Prasad K.V., Prasad G.R.K., Kranthiveer D., Sowmya D., Nikesh M., Sailesh T.V., ECG signal acquisition and analysis for portable heart monitoring devices, 2017 Journal of Advanced Research in Dynamical and Control Systems, Vol:9, issue: Special Issue 14, pp: 1685-1693, ISSN: 1943023X

- Murali Krishna B., Khan H., Madhumati G.L., Praveen Kumar K., Tejaswini G., Srikanth M., Ravali P., FPGA implementation of des algorithm using DNA cryptography,2017 Journal of Theoretical and Applied Information Technology, Vol:95, issue:10, pp. 2147-2158, ISSN: 19928645

- Kumar P.K., Rao P.P., Kakarla H.K., Optimal design of reversible parity preserving new Full adder / Full subtractor, 2017 Proceedings of 2017 11th International Conference on Intelligent Systems and Control, ISCO 2017, pp. 368-373, DOI: 10.1109/ISCO.2017.7856019, ISBN: 9.78151E+12

- Noorbasha F., Manasa M., Gouthami R.T., Sruthi S., Priya D.H., Prashanth N., Rahman M.Z.U., FPGA implementation of cryptographic systems for symmetric encryption,2017 Journal of Theoretical and Applied Information Technology, Vol:95, issue:9, pp: 2038-2045, ISSN: 19928645

- Narasimhanayak V., Lokesh V., Chaitanya V., Feroz M., Soundarya D., Sai Krishna V., Design of bandgap reference circuits, 2017 Journal of Advanced Research in Dynamical and Control Systems, Vol.9, issue: Special Issue 6, pp. 840-846, ISSN: 1943023X

- Tulasi S.K., Prasad G.R.K., Siva Kumar M., Bharath Kumar Reddy A., Giridhar Y., Ajay Reddy C.V., Supriya P.,Design and analysis of T-shaped mendor structure for CPW MEMS switches,2017 Journal of Advanced Research in Dynamical and Control Systems,Vol:9, issue: Special Issue 17,pp: 1987-1994, ISSN: 1943023X

- Ganesh G.V., Srinivasa Rao K., Pavansai Prasad N., Goutham Krishna K., Sravani T., Hemeema K., RF mems based tunable cpw band pass filter integrating periodic circular slot cells,2017 Journal of Advanced Research in Dynamical and Control Systems, Vol:2017, issue:17 Special Issue, pp: 2053-2065, ISSN: 1943023X

- Bharadwaj M., Kishore H., Enhanced launch-off-capture testing using BIST design, 2017 Journal of Engineering and Applied Sciences, Vol:12, issue:3,pp: 636-643, DOI: 10.3923/jeasci.2017.636.643, ISSN: 1816949X

- Murali Krishna B., Madhumati G.L., Khan H., Stochastic key generation mechanism in cryptography applications through partial reconfiguration, 2017 Journal of Advanced Research in Dynamical and Control Systems, Vol:9, issue: Special Issue 12, pp: 1566-1586, ISSN: 1943023X

#### **AUTHORS PROFILE**

- I Veera Raghava Rao, Working as Assistant Professor in ECE Department, KL (deemed to be University) having keen interest in Wireless Communication and VLSI Technology.

- **Aditya M,** Working as Assistant Professor in ECE Department, KL (deemed to be University) having keen interest in Wireless Communication and VLSI Technology.

- **K Sai Nishitha,** B.Tech final year student in ECE department at KL University, having interest in VLSI Technology

- V Kavya Chowdary, B. Tech final year student in ECE department at KL University, having interest in VLSI Technology

- V Naveen Sai, B.Tech final year student in ECE department at KL University, having interest in VLSI Technology