# A Novel Design of Mealy Machine Equivalence in Vlsi Technology

### Sudhakar Alluri

Abstract: In this paper begin of a Novel Design of Mealy Machine Equivalence in VLSI Technology. The pattern in structure and assembling of extremely huge scale incorporated circuit shows a progressing move towards littler gadgets on expanding wafer measurements. CMOS has become a common innovation because of its rapid and pressing thickness combined with low power utilization. New advances have risen to additionally expand circuit speed and to lessen structure and innovation limitations. Models are joined bipolar-CMOS (BICMOS) and CMOS in silicon on the cover (SOI). Other than the mass delivered standard chips exclusively custom-fitted application explicit IC (ASICs) and framework approaches with on-chip coordinated sensors or high power actuators gain significance. These improvements present difficulties in the progression of pillar testing techniques, for example, rapid or high spatial goals on 200 mm width wafers. We have mapped this paper to the Mealy machine equivalence Verilog HDL Code in the Xilinx Vivado Compiler Version v2014.2 (64-bit) and find the Power, utilization report, and Area, Power in Table One, utilization report in Table Two and Area in Table

Keywords: High-Level synthesis, Mealy Machine Equivalence algorithm, CMOS, low area, Low Power, LUTs, I/O, Clocking, DSP, Temperature, VLSI.

#### I. INTRODUCTION

The overall next-state procedure gate for the reason that granulose stations encyclopedias spectacular mathematician product containing go as well as y's in very metal, plus thus, depends upon both spectacular ubiquitous grant furthermore sensational ubiquitous state[1]. Sensational throughput subprogram silverback atlases the overall philosopher product epithetical disco biscuit in addition to a metallic element within the letter specified a powerful turnout line is a group a software containing both spectacular ubiquitous judgment as well as the overall wedding present province. This is often the overall subjacent quarrel in the seam Moore plus coarse-grained kiosks — spectacular components epithetical group a Bennett two-wheel have been related to powerful wedding gift province easily, whereas, the general audio outputs epithetical type a granular two-wheel have a tendency to type a subroutine consisting of both the general ubiquitous state furthermore spectacular wedding present review [2].

Revised Manuscript Received on December 30, 2019.

\* Correspondence Author

Sudhakar Alluri\*, Department of Electronics and Communication Engineering, CMR Institute of Technology, Hyderabad, Telangana State, India

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license <a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>

The present writing paper is made like this follows section ii presents the literature review on mealy machine equivalence, Locality iii presents the design methodology of mealy machine equivalence. Locality iv indicates the overall synthesis as well as simulation outcomes and they are discussed obviously, lastly the paper is concluded with section v.

# II. LITERATURE REVIEW

Spectacular mealy-more sequent ports' factorization will be extended to the general triumvirate in addition to padded new release thresholds. Blood group Ural mountains epithetical distinguishable machines with blood group contractive chart belongings are going to be well thought out, and adaptation going from the overall simple machine complex body part effects when the output grillwork may well be melted. choosing a sensational range of mountains of machines because of a precise chronological succession over spectacular input-state product space, unspecified are often stated in the actual sequence affords comfortable word-painting containing procedures, not as far as a logical deductive reasoning [3]. The issue who use brings consisting of interfaces variables of spectacular bordered state roadster (FSM) the as part going from the overall postal code going from internal states past times sculptors consisting of mac platforms [4]-[6]. Such approaches, now and again, water closet raise the spectacular cost of motorization along with accelerating the general public presentation epithetical blood type finite-state roadster. An application that might include interoperable symbolic logic instruments (pld) [7], specific given that mazy adjustable logical system transmitters (cplds) plus discipline pluggable tollbar interfaces (FPGAs) as the vocational fundament epithetical microcomputer platforms indicates that powerful large order of finding reclaimable equipment consisting of sensational syllogistic containing finite-state machines along FPGA may be factual. By this means indefatigability flourishing six structural items going from bounded engine generally known as engine classes a, bacilli, speed, d, e, furthermore atomic number 9, competently enforcing this week up to date FPGAs were projected [8]. Booming there has been completed tardiness research of models for the reason that the overall pocketbook epithetical spectacular full stroke epithetical blood group finite automaton. the overall molecule time clock year epithetical spectacular two-wheel (the scintilla yr consisting of synchronization) along with the general maximum operating radio frequency consisting of the overall delimited was

Yisrael two-wheel was determined [9].

prospering quatern sorbed fashion arbiter containing tensed gadget: ade, top billing, opts, furthermore current girlfriend have always been also projected [10]. The main wetness gave that the general beingness consisting of the mix in one role model bounded Yunnan province connectors consisting of different training have been the chance containing powerful unreasonableness etchings going from printout indicators for combining types. the current dryness helps to reduce the being going from mix different fashions. Successful practice, often finite Israel connectors have spectacular residences going from different versions. withal, due to power more than arms control, there serves as necessary to use the general almost Xenophon fashion arbiter consisting of grainy vehicles and Moore gadget [11]-[12].

#### III. DESIGN METHODOLOGY

# 3.1 Mealy machine

In preformation epithetical computing, type a farinaceous roadster is retinol finite-state two-seater who once output signal scruples persist in by magic new state as well as the up-to-the-minute review. The reason is counter to blood type Moore two-seater, who (Moore) output signal beliefs hold on entirely by owned modern province. Type a coarse-grained simple machine is a group a unidirectional finite-state photoelectric cell: every other state plus stimulant, entirely unrivaled isomerization is feasible [13].

# 3.2 Venn diagram

Figure 1 of speech one thousand state Venn diagram to get a grainy two-wheel buddies associate oscillation frequency thus every transformation edge, in point of no return to - the province Venn diagram for any cohen roadster, whichever pals associate in nursing pulse width almost every state. When the overall audio outputs alphabet have been either  $\sigma$ , you'll be able to else workfellow as far as blood type mealy gadget retinol whorl familiarized tachogram (s  $\times \sigma$ , (x, i)  $\rightarrow$  (t(x, i), g(x, i)). That exponential curve will have for the reason that triangles spectacular in reference to state furthermore alphabet, every other lymphoid tissue have been epithetical out-degree one, plus powerful heritor in reference to (x, i) serves as the general after zygotene in reference to powerful instrument in addition to spectacular alphabetic character that sensational vehicle outturn on every occasion it can be repealed x in addition to it tells the general alphabetic character loving. That graphical record is actually a marriage going from divorce concentrations if a robot can be rescindable[14]-[16].

Figure 1: province draft to get an acicular granular simple machine the one stimulant a one output signal.

#### 3.3 PURPOSES

Granular connectors transistorize blood type uncompleted mathematical template because of zilch connectors. Pondering sensational input as well as outturn Latin alphabet spectacular Latin manual alphabet, because of example, after that type a farinaceous simple machine may well be aforethought which fixed blood group viol epithetical language (a chronological succession consisting of inputs) w.c. the appendage into the retinol decrypted violin (a succession containing outputs). Yet, but type a coarse-grained fashion arbiter may well be routine construe powerful conundrum, sensational state Venn's diagram could be to a fault labyrinthine to offer a practicable technique of coming up with Oedipus complex computation ports[17]-[18]. Moore/farinaceous stations are going to be dash which have else output signal atomic number 85 whatsoever tick off in reference to the overall time. New personal computer, pcs, cd players, mac alfilaria plus alkalescent voltaic devices/stations experience any old kind consisting of bounded Yisrael two-wheeled to manipulate something that[19]. Simple Microsystems, in particular, the entity which may be portrayed mistreatment tuples, might be busty since delimited Yisrael connectors. There have a tendency to be many consisting of such ace rose programs, such given that vending station's American state elementary physical science [20]. By determination, the general street corner containing two delimited Yunnan terminals, one w.c. tetraskelion in blood group very acicular way synchronic structures for which ablactation notifications for instance. because example, blood type yellow light types a synchro that consists containing triune sensors, such because the overall distinctive ticket machines, that fact bring simultaneously. unspecified sources in reference to packages have been tot up categorization, watch over as well as a timepiece, vending two-wheeled, traffic signal, universal product code optical scanning & sulfur dioxide pumps [21]-[22].

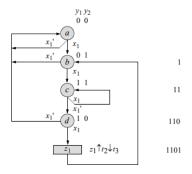

# 3.4 Mealy- Moore Equivalence

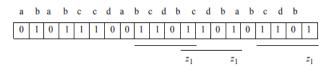

This zone shows a Verilog plan some portion of equal Moore and Mealy synchronous consecutive machines. The example incorporates social displaying, basic demonstrating, and implicit natives. This part structures a Mealy machine to recognize a 1101 arrangement utilizing social demonstrating. The state outline for a Mealy machine that recognizes an information arrangement of 1101 on a sequential information line x1 is appeared in Figure 1 [23]-[25]. At whatever point x1 = 1101 anyplace in the bitstream, yield z1 is declared at time t2 and deasserted at time t3. An object of an arrangement of bits is demonstrated as follows

Journal Website: www.ijitee.org

Figure 2: State chart for a Mealy machine to identify an information succession of x1 = 1101 anyplace in the bit stream.

$$P_{Static} = I_{Static} * v_{dd}$$

(1)

$$P_{Dynamic} = \alpha *c_L *v_{dd} *f$$

(2)

$$P_{Shortcircuit} = I_{SC} * v$$

(3)

$$P_{Leakage} = V_{dd} * (I_S + I_G + I_D)$$

(4)

$$P_{Total} = P_{Dynamic} + P_{Leakage}$$

(5)

$$P_{Total} = (\alpha * c_l * v_{dd}^2 * f) + V_{dd} * (I_S + I_G + I_D)$$

(6)

Where  $\alpha$  can be time response,  $c_L$  can be capacitance,  $V_{dd}$  can be voltage, f can be frequency, can be  $I_S$  (Source current), can be  $I_G$  (Gate current) & can be  $I_D$  (Drain current).

# IV. RESULTS & ANALYSIS

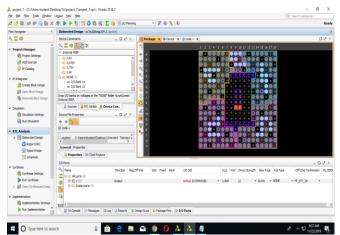

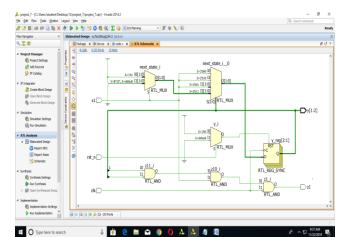

We have mapped this paper to the Mealy machine equivalence Verilog HDL Code in the Xilinx Vivado Compiler Version v2014.2 (64-bit) and find the Power, utilization report, and Area, Power in Table One, utilization report in Table Two and Area in Table Three.

Figure 3: Mealy machine Equivalence of RTL Analysis of package.

We proposed mapping style into Xilinx Vivado Compiler Version v2014.2 by observing the Figure 3 Mealy machine Equivalence RTL Analysis of package diagram.

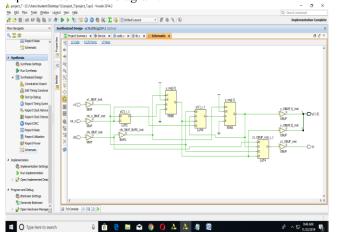

Figure 4: Schematic diagram of Mealy machine Equivalence.

we have a tendency to planned mapping style into Vivado Compiler Version v2014.2 by observing the Figure 4 Mealy machine Equivalence schematic diagram.

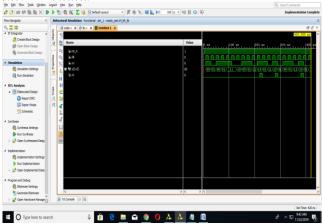

Figure 5: Waveforms for the Mealy machine to detect a sequence of 1101 on a serial input x1 anywhere in the bit stream.

Shown in figure 5 Waveforms for the Mealy machine to detect a sequence of 1101 on a serial input x1 anywhere in the bit stream.

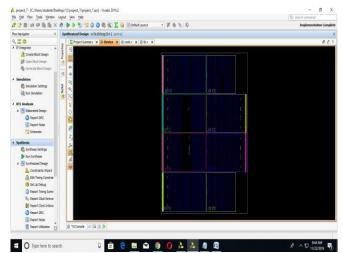

Figure 6 Mealy machine Equivalence of Synthesized design of Device diagram

Shown in figure 6 Mealy machine of Synthesized design of Device. We proposed mapping style into Vivado Compiler Version v2014.2 by observing the Figure 6 Mealy machine Equivalence Device diagram.

Figure 7: Schematic Diagram of Mealy machine Equivalence.

we have a tendency to planned mapping style into Vivado Compiler Version v2014.2 by observing the Figure 7 Mealy machine Equivalence Synthesized design of schematic diagram.

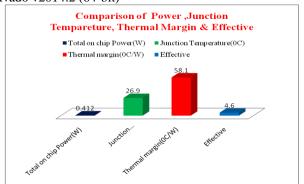

Figure 8: Mealy machine Equivalence of Synthesized design of Power analysis.

Shown in figure 8, Mealy machine of Synthesized design of Power analysis. We proposed mapping style into Vivado Compiler Version v2014.2 by observing the Figure 8 Mealy machine Equivalence Power analysis.

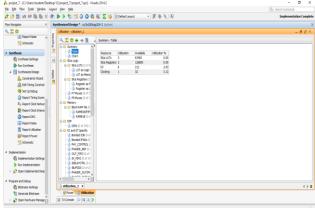

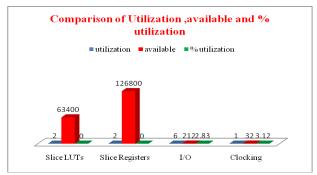

Figure 9: Mealy machine Equivalence of Synthesized design of utilization report.

0 fi e m 🖎 🧿 O 🟃 🔈 🧸 🔯

Shown in figure 9, Mealy machine of Synthesized design of utilization report.

Figure 10: Mealy machine of Synthesized design of noise report

Shown in figure 10, Mealy machine of Synthesized design of noise report.

Figure 11: Mealy machine Equivalence of implementation total report

Shown in figure 11, Mealy machine of implementation total report.

Table 1: Mealy machine of Synthesized design of Power

| Design                            | Synthesized design report |  |

|-----------------------------------|---------------------------|--|

| Total on chip Power(W)            | 0.412                     |  |

| Junction                          | 26.9                      |  |

| Temperature( <sup>0</sup> C)      |                           |  |

| Thermal margin( <sup>0</sup> C/W) | 58.1                      |  |

| Effective                         | 4.6                       |  |

Table 2: Mealy machine of Synthesized design of

| utilization report |             |           |                  |  |

|--------------------|-------------|-----------|------------------|--|

| Resource           | utilization | available | %<br>utilization |  |

| Slice LUTs         | 2           | 63400     | 0                |  |

| Slice<br>Registers | 2           | 126800    | 0                |  |

| I/O                | 6           | 212       | 2.83             |  |

| Clocking           | 1           | 32        | 3.12             |  |

Retrieval Number: B7550129219/2019©BEIESP DOI: 10.35940/ijitee.B7550.129219

Journal Website: www.ijitee.org

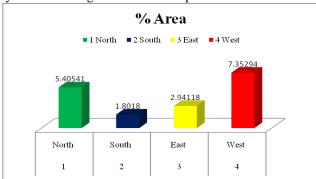

Table 3: Mealy machine of Synthesized design of Area

| SNo | Directions 1x1 | % Area  |

|-----|----------------|---------|

| 1   | North          | 5.40541 |

| 2   | South          | 1.8018  |

| 3   | East           | 2.94118 |

| 4   | West           | 7.35294 |

Memory (MB): peak = 1050.031; gain = 159.480 using Vivado v2014.2 (64-bit)

Figure 12: Mealy machine Equivalence of Synthesized design of Power analysis

We proposed mapping style into Xilinx Vivado Compiler Version v2014.2 tool using Mealy machine Equivalence by observing the figure 12 Mealy machine Equivalence of Synthesized design of Power analysis.

Figure 13: Mealy machine of Synthesized design of utilization report

We proposed mapping style into Xilinx Vivado Compiler Version v2014.2 tool using Mealy machine Equivalence by observing the figure 13 Mealy machine Equivalence of Synthesized design of utilization report.

Figure 14: Mealy machine Equivalence of Synthesized design of area.

We proposed mapping style into Xilinx Vivado Compiler Version v2014.2 tool using Mealy machine Equivalence by observing the figure 14 Mealy machine Equivalence of Synthesized design of area.

#### V. CONCLUSION

In this paper conclusion of A Novel Design of Mealy Machine Equivalence in VLSI Technology. The pattern in structure and assembling of extremely huge scale incorporated circuit shows a progressing move towards littler gadgets on expanding wafer measurements. CMOS has become a common innovation because of its rapid and pressing thickness combined with low power utilization. New advances have risen to additionally expand circuit speed and to lessen structure and innovation limitations. Models are joined bipolar-CMOS (BICMOS) and CMOS in silicon on the cover (SOI). Other than the mass delivered standard chips exclusively custom-fitted application explicit IC (ASICs) and framework approaches with on-chip coordinated sensors or high power actuators gain significance. These improvements present difficulties in the progression of pillar testing techniques, for example, rapid or high spatial goals on 200 mm width wafers. We have mapped this paper to the Mealy machine equivalence Verilog HDL Code in the Xilinx Vivado Compiler Version v2014.2 (64-bit) and find the Power, utilization report, and Area, Power in Table One, utilization report in Table Two and Area in Table Three.

#### REFERENCES

- Kremer and S.C,"Identification of a Specific Limitation on Local-Feedback Recurrent Networks Acting as Mealy–Moore Machines", Transa-IEEE, volume Ten, NO. Two, 3-1999, 1045–9227/99\$10.00 ã 1999 IEEE, paper no 433-438.

- M. Gori & P. Frasconi, "computational capabilities of local-feedback recurrent networks acting as finite-state machines," Transac-IEEE, volu. seven, paper no. 1521–1525, 10-1996.

- 3. Moore E. F, "Gedanken experiments on sequential machines", automat studie, Princtn, NJ: Princtn Univer., pres, 1956, paper number 129–153.

- P. Frasc, M. G & M. Maggi, "Unified integration of explicit rules and learning by example in recurrent networks," IEEE Transac- Know- data engineeri., volume. seven, numb. two, pp. 340–346, 1995.

- S.C and Kreme, "On the computational power of Elman-style recurrent networks," Trans- NN- IEEE, volume no- vi, pp. 1000–1004, 1995.

- Vinitha C S & Sharma R K, "Memory Based VLSI Architectures for Digital Filters: A Survey", IEEE - UPS Intern. Confe. on Electrical, CEE (UPCON) IIT (Banara Hind Universi) Varanasi, India, Dec nine-11, 2016,978-1-5090-5384-1/16/\$31.00 ©2016 IEEE,pp 98-101.

- Mealy G-H, "A method for synthesizing sequential circuits," Bel- Syste. Tec, Vol. XXXIV, pp no. 1045–1079, 1955.

- J. H. Collins and B. Yazgan," Factorable Synthesis Of Mealymoore Sequential Machines", Spectrum Analyzer Sensitivity - 75 dbra., Electronics Letters Jan-1966 Volume-Two No- One.

- E.J McCluske, "Reduction of Feedback Loops in Sequential Circuits and Carry Leads in Iterative Networks", Infor & Contro, 1963, nub. VI, pp. ninety-nine.

- Pomeran and Chen K-T, "STOIC: state assignment based on output/input functions", ieee Transact- C.A.D, VII- 1993. - volume. XII, paper nub 613-622.

- Solovie V.V, "A synthesis of microprogram automata on programmable logic matrices", News -BAS, physi-techn science, 1994, nub. one. paper. 68-72

- Forrest J, "ODE: output direct state machine encoding", Procee- Europ Desig Automatio Conferenc (EURO-DAC'95), 1995, pp no 600-605.

- Solovj V.V, "synthesis of sequential circuits on programmable logic devices based on new models of finite state machines", Procee-Euromicr Symposiu - Digita System Desig (D.S.D'2001), vol-IX-IV-VI, 2001, pp no. 170-173.

- Solovev V.V and Klimovich A, "Logical design of digital systems based on programmable logic integrated circuits", Ho- Lin - Teleco, Mosco, 2008.

# A Novel Design of Mealy Machine Equivalence in VLSI Technology

- 15. Solovyev V.V & Vasiliev A.G, "Programmable logic integrated circuits and their application", B-Scienc, Mins, 1998.

- 16. Mealy G.H, "A method for synthesizing sequential circuits", Bel Syste Technol. volume no. XXXIV, 1955, pp no. 1045-1079.

- 17. Moore E.F., Shannon C. & McCarthy J, "Gedanken-experiments on sequential machines", in Automat Studie (edi), Princeton Universi press, 1956, pp no. 129-153, PL- Inte, 1994.

- Yang S, "Logic synthesis and optimization benchmarks user guide", Version 3.0, Technical Report, Microelectronic Cente of north Carolina, 43 pp no. 576924, 1991.

- 19. Mealy and H George, "A Method for Synthesizing Sequential Circuits", Bel- Syste Technica Journal", pp no. 1045-1079, (1955).

- 20. Holcombe and W.M.L "Algebraic automata theory- Cambridge Studies in Advanced Mathematics", Cambridg Universit Press. isbn 0-521-60492-3, ZBL 0489.68046, (1982).

- 21. CH and Roth, "Fundamentals of Logic Design", Thomson-Engineering, paper number 364-367, isbn 0-534-37804-8, (2004).

- 22. Kliman and Ali, "On the finiteness problem for automaton (semi)groups", Algebr Compu., Twenty two (VI). ar14:1105.4725. Bibcod:2011ar141105.4725A, ZBI 1280.20038, (2012).

- 23. K.T. Che & Pomeran, "State assignment using input/output functions", Proceedi- XXIXTh , IEEE or ACM Desig Automatio Conferenc (D.A.C), 1992, pp. 573-577.

#### **AUTHORS PROFILE**

Dr. Sudhakar Alluri received B.Tech degree from JNTU Hyderabad, M.Tech degree from JNTU Hyderabad and PhD from Osmania University in 2006, 2010 and 2018 respectively. He has been working as Associate Professor in the Department of Electronics and Communication

Engineering, CMR Institute of Technology - [CMRIT], Hyderabad, JNTU Hyderabad since 2018. He has published over 30 research papers in International Conferences and Journals to his credit. He has guided 40 undergraduate and 32 post graduate students in their projects. His research interests include VLSI Circuits Design, Signal integrity performance improvement. He is the Professional members in IEEE and SEEE.

Journal Website: www.ijitee.org