# Design and Implementation of Dual Mode Compressor Based32 Bitdadda Multiplier using Modified Carry Select Adder

# Swapnika Buddaiahgari, Ganeshchokkakula

Abstract— In this paper, we tend to advocate 4:2 compressors, that have the flexibleness of trade between the particular andinexact operational modes. Multiplication is based totally on multiply and adder unit, filtering, convolution which are extensively used in applications of signal processing. As, multiplication takes more execution time in DSP structures, there is need to develop high pace multipliers. In the approximate mode, those dual compressors offer quickness and decrease current consumptions on the fee of lower accuracy. Every single compressors has its personal diploma of efficiency interior the approximate mode moreover to one-of-a-kind delays and strength dissipations internal the approximate and true modes exploitation these compressors inside the buildings of parallel multipliers affords configurable multipliers whose accuracies (as properly as their powers and speeds) can even change dynamically at some stage within the runtime. The proficiency of this compressors in 32-bit Dadda multiplier factor are evaluated exploitation VerilogHDL and simulated and synthesized the usage of XILINX ISE style healthy evaluated by using the employment of modified Carry opt for adder. Comparing their parameters with those of the existing dadda multiplier designed using 4:2 compressors

keywords— 4:2 compressors, exact, approximate computing, configurable, delay, power.

#### I. INTRODUCTION

Motivated through the constrained lookup approximate multipliers, in assessment with the sizable studies on approximate adders, and explicitly the dearth of approximate techniques centered on partial product era, missing of the generation of a few partial merchandise, accordingly decrease the range of partial merchandise that ought to be accrued; decreased depth of the buildup tree, realm and power.By decreasing the great (accuracy), the postpone or electricity consumption of the unit can also be diminished.besides, a few digital structures, which include preferred purpose processors, applied for inexact(approximate) and genuine computation modes [4]. An methodology for execution of this feature is to use Associate in Nursing inexact unit in conjunction with a corresponding correction unit. The most commonly used strategies for the technology of approximate mathematics circuits are truncationand simplification of good judgment.

# Revised Manuscript Received on December 30, 2019.

\* Correspondence Author

**Ms.B.Swapnika\***, Bachelor of Technology in Electronics and Communication from Malla Reddy Institute of Engineering and Technology, Hyderabad, Telangana, India.

Mr.ch.Ganesh, Asst. Professor, ECE Department , VNR Vignana Jyothi Institute of Engineering and Technology, Hyderabad, Telangana, India.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license <a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>

Extensive research has been carried out on approximate deal with providing massive gains in terms of region and energy while exposing small blunders. To meet specifications of speed and electricity, a variety of strategies at totally unique fashion abstraction tiers are suggested. Approximate computing strategies are supported reaching the target specifications at the price of lowering the estimation exactness [4].

The method is likewise used for programs wherever there is no longer a unique solutionor a collection of solutions near the best end result are often notion-approximately suited [5]. These packages consist of multimedia system method, system studying, signal process, and distinctive blunders resilient computations. Approximate mathematics gadgets are based at the simplification of the mathematics gadgets circuits [6]. The runtime accuracy reconfigurability, however, is taken into consideration as a helpful feature for presenting definitely distinct tiers of great of provider at some stage in the system operation [6]–[8].

Here, by lowering a similar recent exactness, the delay intake of the unit is additionally remittent. Additionally, a few digital structures, like significant reason processors, additionally are utilized for each and every approximate and unique (Exact) computation modes [4]. An approach for reaching this option is to apply an approximate unit alongside a corresponding correction unit. The correction will boom the delay, strength, also, the error correction technique may also want over one clock cycle (see [9]), that might, in turn, gradual down the approach further two. Here, predisposed to suggest twin-nice reconfigurable approximate 4:2 adders, which give the power of switch between the specific(Exact) and inexact operative modes at some point of the runtime. The compressors are also applied within the architectures of dynamic great configurable parallel multipliers.

Following sections are mentionedaccordingly.In Section II, many previous works at themultipliers are reviewed. Existing compressor are defined in Section III. Implementation of proposed compressors in 8-bit dadda multiplier is explained in phase IV.Results in chapterV. Finally, thispaper is ended up in SectionVI.

# II. LITERATURE SURVEY

In [1], via modifying the Karnaugh map of a pair of  $2\times2$  number, AN approximate  $2\times2$  number with a less complicated structure has been projected.

# Design and Implementation of Dual Mode Compressor Based32 Bitdadda Multiplier using Modified Carry Select Adder

AN incorrect number fashion methodology supported redesigning the multiplier into a pair of multiplication and non-multiplication elements became delivered multiplication 1/2 changed into designed supported the traditional multipliers whereas the non-multiplication 0.5 became enforced in an inexactarchitecture comprehensive of well value of mistakes. It has to be compelled to be expressed that each of the ways given in [1] be afflicted by using immoderate relative mistakes. In [8], a static part methodology (SSM) is given, that performs the multiplication operation on an 'm' bit section ranging from little of the enter operands the place m is ample or larger than n/2. Also, a dynamic vary world company biased range (DRUM) multiplier, that selects AN mbit section, ranging from the leading one very little of the enter operands, and units the smallest amount fundamental very little of the truncated values to "1," has been planned for the length of this form, the truncated values are improved and shifted to the left to return up with the ultimate output. Although, with the resource of capability of exploiting smaller values for 'm', the form of presents precise patterns than those of different.

In[10], a high accuracy approximate four×four Wallace tree multiplier factor was projected. This multiplier factor applied a 4:2 approximate counter succeeding in extend and electricity discount rates of the partial product stage of the four×four Wallace tree. The particular output within the case of the particular operational mode is generated giving Associate in Nursing inexact adder with a small quantity elevate propagation shelve, the partial product cut price level was increased. throughout this paper, Associate in Nursing OR-gate-based entirely error discount unit become what is more projected. In [8], a miscalculation primarily based inexact multipliers (ROBA) projected that spherical the entire operands into the closest exponent of two. It must be located that the error healing unit will increase the capacity intake and put off of the multiplier.

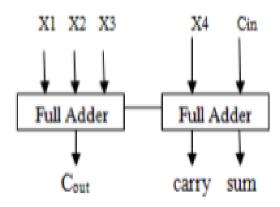

Fig.1. 4:2 compressors.

Fig 2: Structure of the conventional 4:2 compressor.

Thisaccuracy configurable multipliers would have massive delay and strength overheads. in the course of this paper, we have a tendency to recommend compressors, that have the flexibility of shift between the approximate and proper modes with terribly little prolong and electricity overheads.

#### III. EXISTING SYSTEM

First, some history on the particular 4:2 mechanical machine is obtainable, this kind of mechanical device, tried schematically in Fig.1.The internal form of an express 4:2 mechanical gadget consists of 2 serially linked whole adders, tried in Fig. 2.here, weights of all of the inputs and additionally the total output are same whereas the weights of the provide and Cout outputs are one binary bit role higher.

$$sum = x1 \oplus x2 \oplus x3 \oplus x4 \oplus Cin \tag{1}$$

carry =

$$(x_1 \oplus x_2 \oplus x_3 \oplus x_4)Cin + \overline{(x_1 \oplus x_2 \oplus x_3 \oplus x_4)}x_4$$

(2)

$$Cout = (x1 \oplus x2)x3 + \overline{(x1 \oplus x2)}x1. \tag{3}$$

The mechanical gadget 4:2 timber additionally consists of a normal structure and sums the partial merchandise as a binary tree will,mistreatment 4:2 compressors rather than CSAs.

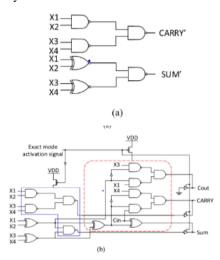

Fig3. Exact 4:2 compressor

#### IV. PROPOSED 4:2COMPRESSORSTRUCTURE:

The indoors structure of the approximate half and as a end result the wellknown form of DQ4:2Compressor are hooked up in Fig.4. the gates of the approximate half, powered OFF all via the pleasant Operational mode, are indicated through the usage of way of the blue lineandthe supplementary indicated with the resource of dashed line.

Fig4: (a) Inexact part of DQ4:2Compressor (b) overall architecture of DQ4:2Compressor

#### V. PROPOSED COMPRESSORS

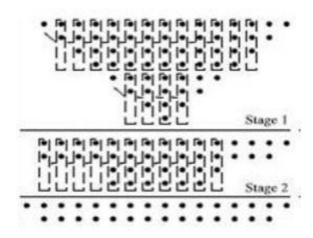

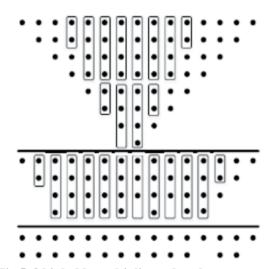

In this segment the proposed twin excellent 4:2 compressors on eight-bit dadda multiplier. And we can observe how those designs lessen the power, put off, location of the multiplier circuits. Fig.5.Shows the discount circuitry of 8-bit dadda multiplier.

Fig.5. 8 bitdadda multiplier reduced structure.

A acceptable combination of the projected compressors is also applied to realise an increased trade-off amongst the accuracy and style parameters. As anchoice, the utilization of every DQ4:2C1 and DQ4:2C4 for the LSB and mutual financial savings financial institution aspects inner the multiplication, severally, is typically recommended proper here. These multiplier factors are in contrast through

mistreatment the approximate Daddamultipliers utilized by way of 2 formerly projected approximate 4:2 blowers moreover to the configurable multiplier. These multipliers encompass 32-bit unsigned ROBA, SSM with a section dimension eight (SSM8), and DRUM with a locality dimension six (DRUM6).

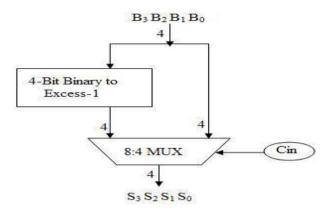

Fig.6. multiplexer based binary to excess-1 converter.

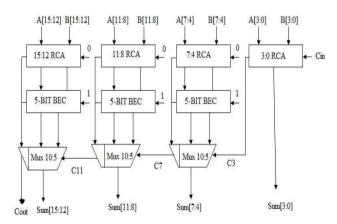

Thus, modified CSLA is designed whichutilize entire lot a great deal much less place and has low energy than usual CSLA. Block plan of Modified CSLA is installed internal the under Fig.

Fig.7 16-bit modified CSLA

A changed Carry Select-Adder fashion is planned, that create use of ripple raise adder and Binary to Excess-1 convertor (BEC) as a substitute than the utilization of twin RCAs to scale back vicinity and power consumption with tiny cost penalty. the 4-bit ripple lift adder is employed in every block and for this reason the extra converter used is of 5-bit intensive, inside the similar capability MCSA architectures are designed for eight-bit, sixteen-bit, 32-bit and sixty four-bit. The metrics for size of ordinary performance are space, energy and shelve. So, when planning MCSA for 8-bit to 64-bit its location, electrical strength and shelve are analyzed The effects for this reason obtained are then in contrast with the consequences of historical CSA.

## VI. RESULTS

# 1. Simulation & Synthesis

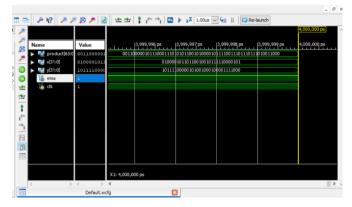

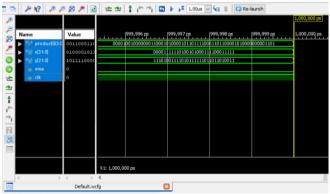

Simulation of 32 bitdadda multiplierusing dual mode compressor with modified carry select adder is shown below.

Fig.8 Simulation result of proposed approximate Dual Quality 4:2compressor in 8 bitdaddamultiplie

Fig.9 Simulation result of proposed exact DQ4:2C4 compressor in 8 bitdadda multiplier

| Device Utilization Summary (estimated values) |      |           |             |     |

|-----------------------------------------------|------|-----------|-------------|-----|

| Logic Utilization                             | Used | Available | Utilization |     |

| Number of Slices                              | 68   | 4656      |             | 1%  |

| Number of 4 input LUTs                        | 118  | 9312      |             | 1%  |

| Number of bonded 108s                         | 32   | 232       |             | 13% |

Fig.10.Design summary of proposed dual quality 4:2 Compressors

|          | Conventional<br>multiplier | Compressor based<br>dadda multiplier |

|----------|----------------------------|--------------------------------------|

| LUT      | 179                        | 16                                   |

| SLICE's  | 69                         | 61                                   |

| Time(ns) | 16.517                     | 12.882                               |

Table1: Comparisonof conventional and dadda multiplier

# Implementation in FPGA

To extract the diagram parameters of the multipliers, we employed the usage of XLINX ISE on nexty 4 DDR FPGA Artix 7 which has 100MHz clock frequency.

Finally, all the studied approximate multipliers are as in contrast supported exceptional accuracy and fashion parameters

Fig.32 bitdadda multiplier implemented on FPGA board.

# VII. CONCLUSION

In this endeavor, we are going to be susceptible to propose DQ4:2Cs that had the flexibleness of exchange among the precise and inexact running modes. at intervals the inexact mode, these compressors provided higher speeds and decrease electricity consumptions at the price of reduce accuracy.

# REFERENCES

- O. Akbari, M. Kamal, A. Afzali-Kusha, and M.Pedram, "RAP-CLA: A reconfigurable approximate carry look-ahead adder," IEEE Trans. Circuits Syst. II,ExpressBriefs,doi: 10.1109/TCSII.2016.2633307.

- A. Sampson et al., "EnerJ: Approximate data types for safe and general low-power computation," in Proc. 32nd ACMSIGPLAN Conf. Program.Lang. Design Implement. (PLDI), 2011, pp. 164– 174.

- 3. A. Raha, H. Jayakumar, and V. Raghunathan, "Inputbaseddynamic reconfiguration of approximate arithmetic units for video encoding," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 24, no. 3, pp. 846–857, May 2015.

- J. Joven et al., "QoS-driven reconfigurable parallel computing for NoC-based clustered MPSoCs," IEEE Trans. Ind.Informat., vol. 9, no. 3,pp. 1613–1624, Aug. 2013.

- R. Ye, T. Wang, F. Yuan, R. Kumar, and Q. Xu, "On reconfigurationoriented approximate adder design and its application," in Proc. IEEE/ACM Int. Conf. Comput. Aided Design (ICCAD), Nov. 2013,pp. 48–54.

- M. Shafique, W. Ahmad, R. Hafiz, and J. Henkel, "A low latency generic accuracy configurable adder," in Proc. 52ndACM/EDAC/IEEEDesignAutom. Conf. (DAC), Jun. 2015, pp. 1–6.

- S. Narayanamoorthy, H. A. Moghaddam, Z. Liu, T. Park, and N. S. Kim, "Energy-efficient approximate multiplication for digital signal processing and classification applications," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 23, no. 6, pp. 1180–1184, Jun. 2015.

- S. Hashemi, R. I. Bahar, and S. Reda, "DRUM: A dynamic range unbiased multiplier for approximate applications," in

- K. Y. Kyaw, W. L. Goh, and K. S. Yeo, "Low-power high-speed multiplier for error-tolerant application," in Proc. IEEE Int. Conf. Electron Devices Solid-State Circuits (EDSSC), Dec. 2010, pp. 1–4.

- DamarlaParadhasaradhi, M. Prashanthi, N Vivek, "Modified wallace tree multiplier using efficient square root carry select adder", Green Computing Communication and Electrical Engineering (ICGCCEE) 2014 International Conference on, pp. 1-5, 2014.

## **AUTHORS PROFILE**

Ms.B.Swapnika, completed her Bachelor of technology in Electronics and communication from Malla reddy institute of engineering and technology, Hyderabad, in the year 2017. Her research of interest is in VLSI design. she is pursuing Master of Technology in VLSI system design from VNR Vignana Jyothi Institute of

Engineering and Technology, Hyderabad, Telangana, India.

**Mr.ch.Ganesh**, has obtained his MTech in 2014, specialized in VLSI design. He is working as Asst. Professor in ECE Department at VNR Vignana Jyothi Institute of Engineering and Technology, Hyderabad, Telangana, India. He is pursuing his Ph.D at K L University, His research interests is in VLSI design.