# New Computer Controlled High Resolution Programmable Validation System for Research in Electronics Hardware

Nilima Warke, J. M. Nair, P. P. Vaidya

Abstract: Conventional methods for validation of electronics hardware research are susceptible to manual measurement errors, and give limited accuracy of 8 to 10 bits. These methods are also time consuming and do not ensure accuracy in validation of performance parameters. Hence, a new computer controlled high resolution programmable hardware research validation system has been proposed here for testing the electronics hardware systems. The test signals with high resolution (16 bit) and high accuracy are generated using multiplying digital to analog converter (MDAC) with high reference bandwidth. The output signals are measured with the same resolution and accuracy using 16 bit analog to digital converter (ADC). The output data is transferred to the PC through USB interface for further analysis using Teensy 3.6 card. The signals can be generated in bandwidth of 0-10MHz in step size which can be as small as 10µV and as large as 600mv which is user programmable. This proposed system has been designed, constructed and tested. The experimental results of this system have been reported here which ascertain the performance of the system. With this system, manual errors in measurement are avoided and testing time is significantly reduced. The reported system is low cost economic solution for validating the electronic research work in academic

Keywords: Computer controlled validation, electronics hardware systems, fast testing time, high resolution measurement

#### I. INTRODUCTION

Electronic hardware systems are often designed and constructed based on new concepts and methods during research work in field of electronics engineering. The performance of these hardware systems needs to be validated for the input-output relationship for which these systems are designed. During conventional testing, a set of test signals are applied to the inputs of the device under test (DUT) and the output responses are analysed [1][2]. The basic testing system is as shown in Fig. 1. Devices can be tested manually and automatically [1].

Revised Manuscript Received on December 30, 2019.

\* Correspondence Author

Nilima Warke\*, Department of Instrumentation, V.E.S.Institute of Technology, Mumbai, India. Email: nilima.warke@ves.ac.in

- **J. M. Nair**, Department of Instrumentation, V.E.S.Institute of Technology, Mumbai, India. Email: principal.vesit@ves.ac.in

- **P. Vaidya**, Department of Instrumentation, V.E.S.Institute of Technology, Mumbai, India. Email: pp.vaidya@ves.ac.in

- © The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license <a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>

Conventional methods for validation of hardware research involve use of function or pulse generator, digital storage oscilloscope (DSO), high resolution digital multimeter (DMM) etc. for measurement of input and output signals.

Fig. 1: Basic Testing Approach

Manual testing typically requires function/pulse generator for test signals and DMMs, DSO and frequency analysers to observe the output Test input signals are generated using signal generator units with sine square and triangular waveforms amplitude of which can be adjusted with the resolution of few millivolts. Signal generators provide precise, highly stable test signals for a variety of components and systems testing purpose [3]. Direct digital synthesis (DDS) and point to point (PxP) techniques are used in signal generators [4],[5]. DDS involves switching of digital to analog (DAC) code resulting into spikes (jitter) in the output [5]. PxP uses digital filters along with switching code [4] which increases the complexity of circuit.

DMM measure only DC with 3 1/2 to 8 1/2 digit accuracy, DSO measures AC with limited accuracy of 8 to 10 bits. To analyse the frequency response, spectrum analysers are also used. DSO and analyser have limited storage capacity.

These methods of validation give limited accuracy of 8 to 10 bits and are susceptible to manual measurement errors. These methods are also time consuming and do not ensure accuracy in validation of performance parameters [6].

When a new hardware is developed as a part of research work, it needs to be tested thoroughly for expected input-output relationship. For this purpose, many times it is required to give the input signals in steps of few microvolts over a wide bandwidth of nearly 0-10MHz. It is quite clear that the conventional measurement systems described earlier are not able to meet these requirements. Hence these validation methods are often questioned by expert research workers in this field. The integrated test systems which are commercially available from reputed manufacturers like Tektronics, Keysight etc are very costly (around Rs 15lakhs more) and don't give high resolution and accuracy of 16 bit which is required for precise measurement. So, there is a need of new hardware research validation system which should be able of generate the test signals with high resolution (16 bit) and high accuracy.

Journal Website: www.ijitee.org

# New Computer Controlled High Resolution Programmable Validation System for Research in Electronics Hardware

The system should also be able to measure the output signals with the same resolution and accuracy for analysis of input-output relationship.

It is also desirable to generate the test input signals using the computer controlled system so that the manual errors during the adjustment of input test signals are avoided and the testing time of the system is also scaled down.

#### II. PROPOSED SYSTEM

The system is designed to address the problem of research validation of hardware system in academic and other sinusoidal signal in form of a DC voltage which is presented as input to the internal ADC of Teensy 3.6 board. The Teensy 3.6 is a complete USB-based microcontroller development system and all programming required for this validation system is done via the USB port. It is a breadboard-friendly feature-packed development board and pre-flashed with a bootloader. This allows easy programming using the on-board USB connection without the requirement for an external programmer. Teensy Version 3.6 features a 32 bit 180 MHz ARM Cortex-M4 processor with floating point unit. Selection of Teensy 3.6 board permits the PC communication interface with

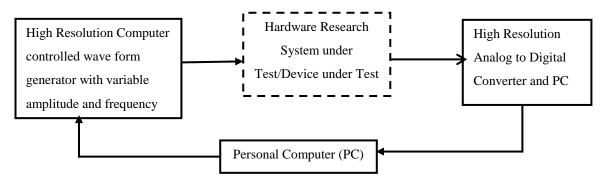

Fig. 2: Block diagram of hardware Research validation system

institutes using low cost commercial available components. The block diagram is as shown in Fig. 2. The block diagram consists of following building blocks-

- 1) Input Block -Wave form generator with variable amplitude and frequency

- 2) Output block: High resolution ADC with PC interfacing

- 3) Personal computer

High Resolution Computer controlled waveform consists of a conventional pulse generator whose amplitude is scaled down and adjusted with microvolts accuracy using a high speed MDAC.

Output of this MDAC is given as test input to the DUT. The input code to DAC is computer controlled through USB interface circuit. Binary counter circuit is utilised to increment the DAC code as controlled by PC. The Teensy 3.6 microcontroller board has been used for USB interface. This board has internal 16 bit ADC which has conversion time of nearly 20µs. This ADC can be used for digitization of low frequency signals (less than 25kHz). For digitization of high frequency signals, external ADC with 16 bit resolution and required sampling rate is used.

However, for testing of any linear hardware system where both inputs—outputs are sinusoidal signals such as linear amplifier, the output signal can be sampled at the peak value using a peak detector circuit and digitized using the internal 16bit ADC available on the Teensy 3.6 board.

For this case, only peak detector circuit needs to operate at high frequency to detect and hold the peak of output high speed (480 Mbit/sec) port, for high speed applications two CAN bus ports, four I2C ports can also be used. To get the accurate results, 100 of samples are taken for each amplitude and average is calculated. This also reduces the effect of noise. The input-output relationship is plotted in form of a graph. Similarly, the phase shift between input-output is also calculated and displayed on the PC screen.

# III. DESIGN OF HARDWARE RESEARCH VALIDATION SYSTEM

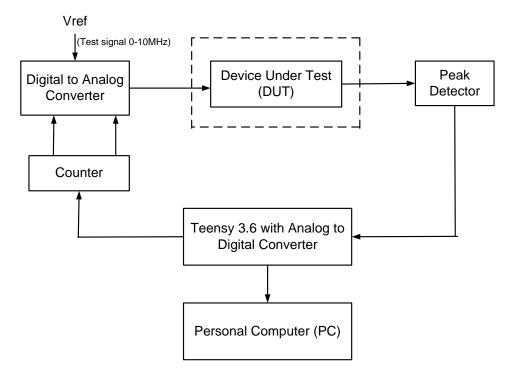

The block diagram of the developed hardware research validation system is as shown in Fig.3.Test signals for DUT are generated using high resolution and high speed MDAC which is utilized to scale down the reference sinusoidal signal. This sinusoidal signal input to DUT can be changed in steps of few  $\mu Vs$  by incrementing digital code of counter which is controlled through the USB interface. The reference signal can be any type of conventional signal such as sinusoidal, triangular or square pulse including any DC signal. The bandwidth of this input signal is from 0-10MHz when MDAC type DAC8822 is used for this purpose.

However, for most of the applications, the input-output signals to DUT are sinusoidal for which the reference voltage also needs to be sinusoidal signal of required frequency.

Journal Website: www.ijitee.org

Fig.3: Block diagram of validation system for the developed research work

Since the output of DUT is also sinusoidal nature, a peak detector circuit has been used to make use of 16-bit ADC internal to the Teensy 3.6 board. The phase shift between input-output signals is measured using the TTL logic circuit designed for this purpose. The phase shift is normalized to display it in form of degrees. The step size of input sinusoidal signal depends upon the peak amplitude of reference signal. This step size can be as small as 10µV for a reference voltage nearly 0.650 mV and can be around  $150 \mu V$  for reference voltage of 10V peak amplitude. For the experiments where such high resolution is not required, the system is programmable so that instead of 16 bit of resolution; 12bit, 8 bit or 4 bit can be selected. This increases the step size but reduces the testing time because correspondingly less number of steps is involved. For a resolution of 10 but, total number4 of steps in amplitude selection is equal to 2<sup>10</sup> which means for 16 bit resolution nearly 65,000 steps can be selected whereas for 8 bit resolution only 256 steps are required. To reduce the effect of noise in the system, for any applied step large number of samples are selected for digitization and average calculated by the PC and displayed. These numbers of samples are selectable.

For a 16 bit resolution, nearly 65,000 steps are generated and for each step 100 samples are digitised and averaged. Hence, the total time required for this operation assuming 20µs conversion time for ADC is 2ms for each samples is nearly 130sec. this illustrates the amount of the time saved during testing of the system against the manually operated one. Moreover, the errors due to the manual adjustment are totally removed. However, further resolution can be increased to more than 24bits using second DAC available in MDAC type 8822 also. The output generated from MDAC 8822 is as shown in Fig. 4.

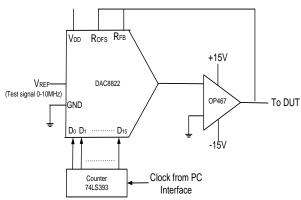

Fig.4: Circuit diagram of Input block of validation system

The output of MDAC is in the form of current which is converted to equivalent voltage using current to voltage converter for which the op-amp with a bandwidth of 20MHz i.e OP467 is used. This op-amp offers bias current 100nA and offset voltage 0.5mV. The supply voltages for MDAC 8822 as well as op-amp are generated using the voltage regulators type L7815, L7915 and L7805, L7905 respectively. The PCB designed for this purpose includes required decoupling capacitors and separate analog and digital ground planes to scale down the effect of noise. Counter type 74LS393 has been used to increment the digital code of the DAC.

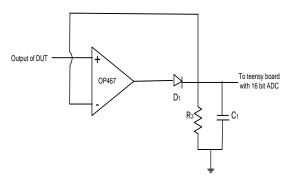

The peak detector and stretch circuit used for this purpose is as shown in Fig. 5. The op-amp OP467 and diode D<sub>1</sub> 1N4004 has been used for this purpose along with capacitor C<sub>1</sub>. The resistor R<sub>3</sub> provides a discharging path for the capacitor.

# New Computer Controlled High Resolution Programmable Validation System for Research in Electronics Hardware

Fig. 5: Peak detector and stretch Circuit diagram Phase shift measurement circuit:

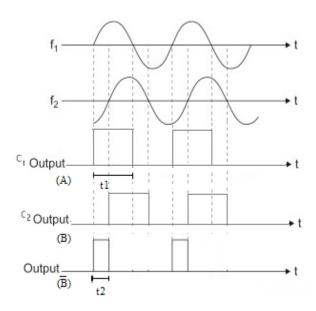

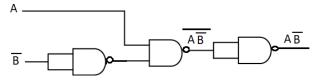

To measure the phase shift between input-output signals zero cross over technique has been used. The circuit uses analog comparators and required logic circuits have been designed as shown in Fig. 6a and 6b.

Fig. 6a: Principle of phase shift measurement

Fig. 6b: Logic Circuit to measure phase shift

Here both input and output signals as  $f_1$  and  $f_2$  are given to analog comparators. The other inputs of these comparators are grounded. Hence these comparators work like a zero cross-over detector and generate a output TTL pulse whose width is equal to the time duration that the input signal exceeds the zero voltage level. The outputs of the comparators are then fed to the logic circuit as shown in Fig 6b. The phase shift duration available in the form of the pulse width which is measured using the Teensy board 3.6 and displayed on a personal computer. The logic circuit generates the output whose pulse width is proportional to the phase shift to be measured.

Let,

t1 is the time duration when input is above zero volts.

t2 is the time difference between the durations when input and output are above zero volts.

then phase shift can be calculated in degrees as --Phase shift = (t2/t1) 180 ----(1)

#### IV. RESULT

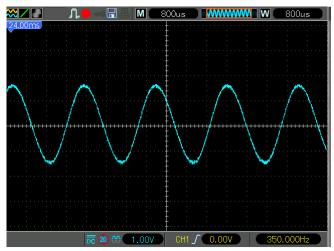

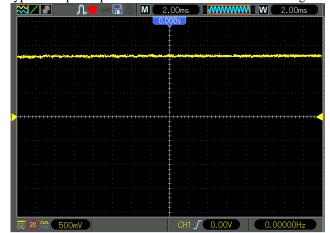

The system has been constructed using the components as described above for testing the system performance. The amplitudes and frequencies of input signals were varied. The input code to the DAC was also changed using the increment counter and the values of the output system i.e input to the DUT were observed. One such input observed is as shown in Fig 7. Instrumentation amplifier was used as DUT with a gain of 100 and the output was held using the peak detector circuit and given to Teensy board for digitization.

Fig.7: Input block performance

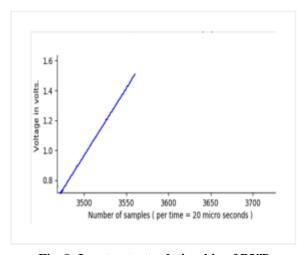

A typical output of peak detector circuit is as shown in Fig. 8.

Fig.8: Output of DUT

The relationship between input and output was plotted as shown in

Fig.9. To observe the effect of phase shift, the input sinusoidal signal was shifted using R-C circuit and corresponding phase shift was measured and calculated using eq (1) and displayed on PC.

Journal Website: www.ijitee.org

Fig. 9: Input output relationship of DUT

#### V. CONCLUSION

A programmable computer controlled high resolution validation system was developed for validation of hardware research as described in this paper. The design is simple for testing of linear circuits where both inputs and outputs are sinusoidal in nature. In such cases, external ADC is not required since the output can held by peak detect circuit and digitized using the inbuilt ADC available on Teensy 3.6 board. The component cost of such system is nearly Rs 15000/- which can be afforded by academic institutes working in hardware research. When input signal is not sinusoidal in nature, the output needs to be digitized using high speed ADC and these digitized samples need to be stored in PC for further processing to find out input-output relationship. Though the cost of system is quite low, it can give much high resolution of microvolts which is not available in conventional test and measurement systems. The results can be validated with resolution of 16 bit which is much higher than the conventional 8-10 bit resolution is offered by conventional DSO. The bandwidth of input-outputs signal is limited to 10MHz mainly because of bandwidth limitation of DAC. However, this bandwidth with 0-10MHz is adequate for most of the analog circuits developed in field of electronics for which this validation system provides one important solution.

### **ACKNOWLEDGMENT**

Author would like to acknowledge the help given by management of V.E.S. Institute of Technology and University of Mumbai for partially funding this project under minor per research grant University as APD/ICD/2018-19/593, Project No. 186.

## REFERENCES

- S.Asvini, C.Nirmala, "Design for Testability in Timely Testing of VLsi Circuits", International journal of Engineering Research and Applications, Vol 5, issue 3(part 2), March 2015, pp 10-13.

- Manjula C, "Survey of electronic Hardware Testing Types, ATE Evolution & Case studies", International journal of Engineering Research 7 Technology, Vol 6, issue 11, Nov 2017, pp 165-170.

- Keysight Technologies -Application note: "9 best Practices for Optimising your Signal Generator- Part 2 Making Better Measurements", Oct 2018, pp 1-11.

- Agilent Technologies: Measurement Tips "Comparing Function generator Performance: Direct Digital Synthesis Versus Point-by-point Technology". 2011, Pp 1-4.

- 5. Jian Qi, Qun sun, Xiaoliang Wu, Chong Wang, and Linlin Chen, "Design and Analysis of a Low Cost Wave Generator Based on Direct digital Synthesis", Journal of electrical and Computer Engineering, Volume 2015, Article ID 367302.

- Haralampos-G Stratigopoulos. Test Techniques for Analog Circuits and Systems. Micro and nanotechnologies/Microelectronics. Université de Grenoble, 2015.

#### **AUTHORS PROFILE**

Nilima Warke received her M.E Biomedical Engineering from University of Mumbai, India, in 2005. She is currently working as Associate Professor with Department of Instrumentation, V. E.S.I.T, Chembur. She is a member of ISTE and ISA. Her current interests are Electronics, Biomedical and Process Instrumentation..

J. M. Nair received Ph.D degree in Systems and Control Engineering from IIT, Powai, India, in 1995. She is currently working as Professor, Department of Instrumentation and presently holding the post of Principal, V.E.S.I.T, Chembur, India and. She is a member of ISTE. Her field of interest is Control Engineering and Nuclear

**Data Evaluation**

P. P. Vaidya has received Ph.D degree in Electrical Engineering from IIT, Powai, India in 1988. He has worked in Bhabha Atomic Research Center, Mumbai, India in field of Nuclear Instrumentation. Now he has been working as a Professor and Head R&D and keenly interested in Research and Development activities in

V.E.S.I.T, Chembur. He is a member of IEEE. He has published several papers in field of Nuclear Instrumentation as well as in electronics circuits in several reputed journals. His major field of interests is design and development of Analog and Digital circuits for different applications.