# VLSI Architecture of High Performance Multiplier for High Speed Applications

# J.M.Mathana, R.Menaka, R.Dhanagopal, B.Sundrambal

Abstract: In the application of signal process multipliers play a vital role. With advances in technology, several researchers have tried and try to design multipliers which supply high speed, low power consumption, regularity of layout and thus less space or maybe combination of them in one multiplier factor. Thus, Compact VLSI design for four bit multiplier factor is planned during this paper that is appropriate for low power and high speed applications. Multiplier factor with high performance is achieved through the novel style of hybrid single bit full adder and Dadda algorithmic rule. The important path delay and power consumption of the planned multiplier factor square measure reduced by 65.9% and multipliers. 24.5% severally when put next with existing The planned multiplier factor is synthesized exploitation CADENCE five.1.0 EDA tool and simulated exploitation spectre virtuoso.

Keywords: Multiplier; Dadda Algorithm; Gate diffusion Input (GDI);Pass transistor logic (PTL);CMOS process technology;Cadecne(tool)

#### I. INTRODUCTION

In the real time signal processing applications, the multipliers are the basic module of the digital systems. Many research works are being done to reduce power dissipation, area and time in multipliers and dividers. The multiplier <sup>[11]</sup>designed using approximate half adder and full adder reduces all parameters by 25% to 35%. The high speed vedic multipliers <sup>[21]</sup> designed to implement DSP operations of finite length sequences which reduces the processing time 40% to 60% than the conventional multiplier. Fixed and floating pointmultipliers <sup>[3]</sup> designed by Vedic algorithm increased the operating speed and precision of the Digital Signal Processors. Many algorithms/architectures developed and implemented using Dadda<sup>[4]</sup>, Wallace tree<sup>[5]</sup>, Vedic<sup>[6]</sup> and Booth etc. are used to optimize power and speed.

In section II discussed about the dadda algorithm. The architecture of proposed system is explained in the part III.

**Revised Manuscript Received on January 30, 2020.** \* Correspondence Author

**Dr.J.M.Mathana**\*, Professor, Dept. of Electronics and Communication Engineering, Chennai Institute of Technology, Kundrathur, Chennai, Tamilnadu, India

**Dr.R.Menaka**, Professor, Dept. of Electronics and Communication Engineering, Chennai Institute of Technology, Kundrathur, Chennai, Tamilnadu, India

**Dr.R.Dhanagopal**, Associate Professor, Dept. of Electronics and **Communication** Engineering, Chennai Institute of Technology, Kundrathur, Chennai, Tamilnadu , India

**Dr.B.Sundrambal**, Professor, Dept. of Computer Science and Engineering, Chennai Institute of Technology, Kundrathur, Chennai, Tamilnadu, India

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an <u>open access</u> article under the CC-BY-NC-ND license <u>http://creativecommons.org/licenses/by-nc-nd/4.0/</u>

*digital* Part IV provides the result analysis of the proposed and *ces in* existing approximatemultipliers. Part V describes the *d try to* conclusion.

#### II. DADDA ALGORITHM

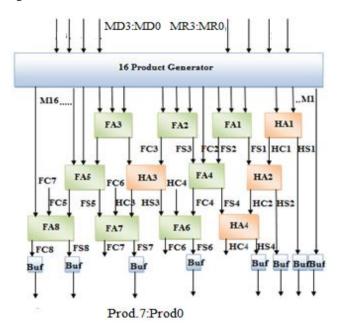

In the proposed work, the speed of the critical path of the multiplier is reduced by reducing the length of the tree with the help of dadda algorithm [8]. The proposed 4 bit multiplier consists of sixteen partial products. Fig. 1 shows a sample 4x4 multiplications, where the length of the tree is four. With the help of dada algorithm the length of the tree is reduced to two.

|       |       |         | MD3 MD2 MD1 MD0<br>× MR3 MR2 MR1 MR0    |                  |                  |        |      |  |

|-------|-------|---------|-----------------------------------------|------------------|------------------|--------|------|--|

| MD3MR |       | 2 MD2MR | MD3MR0<br>MD2MR1<br>2 MD1MR2<br>3 MD0MR | MD1MR1<br>MD0MR2 | MD1MR0<br>MD0MR1 | MD0MR0 |      |  |

| Prod7 | Prod6 | Prod5   | Prod4                                   | Prod3            | Prod2            | Prod1  | Prod |  |

# Fig.1. Sample 4×4 Multiplication

Dadda algorithm does not require any previous Level output to compute next Level output, which reduces the propagation delay. In the first Level, dada algorithm diminishes the tree length from four to three. During the second Level, the length is still reduced from three to two, and in the final Level, the total length of the multiplication tree is reduced to two. The Level wise reduction procedure is shown in below figures 2, 3 and 4.

MD3MR3 MD3MR2 MD3MR1 MD3MR0 MD2MR0 MD1MR0 MD0MR0 MD2MR3 MD2MR2 MD2MR1 MD1MR1 MD0MR1 MD1MR3 MD1MR2 MD0MR2 MD0MR3 Fig.2. Level -1 MD3MR3 MD3MR2 FS3 MD3MR0 FS1 HS1 MD0MR0

MD2MR3 FC2 FS2 HC1 FC3 FC1 Fig.3. Level -2

MD3MR3 FS5 HS3 FS4 HS2 HS1 MD0MR0 FC5 HC3 FC4 HC2

Fig.4. final Level

# III. PROPOSED 4×4 MULTIPLIER

The general block diagram of projected four ×four multiplier is given in Fig.5. This multiplier is developed in terms of pass transistor logic based hybrid three input binary digits adder circuit and two input binary digits adder circuit. This circuit consists of 10 transistors.

In the first Level of the multiplier there are 16 partial products and generated and implemented using 16 logical AND gates.

Retrieval Number: B7405129219/2020©BEIESP DOI: 10.35940/ijitee.B7405.019320 Journal Website: <u>www.ijitee.org</u> Published By:

Blue Eyes Intelligence Engineering

& Sciences Publication (BEIESP)

© Copyright: All rights reserved.

In secondLevel,by using three 3-input binary digits adder circuit and one two input binary digits adder circuitthe length of the tree is reduced to half.In the third Level, the length is further reduced by usage of only two2-input binary digits adder circuitand two 3-input binary digits adder circuit. In order to get better output voltage finally the output signals are passed through the buffers as shown in figure 5.

Fig.5. Architecture of proposed 4×4 multiplier

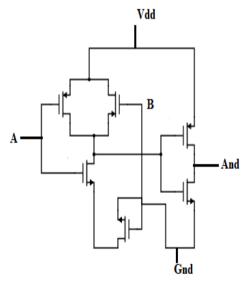

In the proposed architecture consists of eight three input binary digits adder circuit, four two input binary digits adder circuit and eight buffers. The schematic of the basic AND cell is shown in Fig.6.

# Fig.6. AND Gate<sup>[7]</sup>

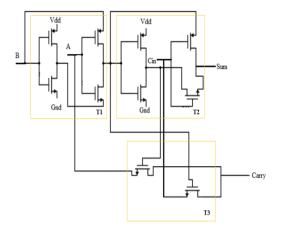

Fig. 7 shows the circuit diagram of single adder user in the proposed multiplier. It has three modules T1, T2 and T3. Module T1 is the Gate Diffusion Logic (GDI) XOR gate.Module T2 and T3 are Pass Transistor Logic (PTL) XOR, PTL MUX respectively. Module T1 and T2 are responsible for the generation of sum of full adder. Carry output is generated by the help of module T3.

Fig.7. Proposed single bit full adder

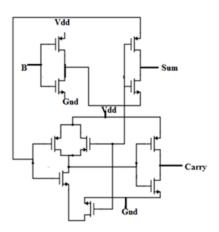

A two input binary digits adder circuit will play vital role to design multiplier. In 4x4 multiplier design four two input binary digits adder circuit are used. The CMOS schematic diagram of thetwo input binary digits adder circuit is shown in Fig.8.

# Fig.8. Two input binary digits adder circuit<sup>[7]</sup>

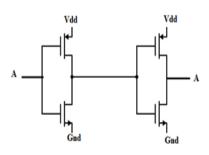

The buffer in the multiplier is used to propagate the signals from initial Level to final Level and also to retain the voltage level. It is shown in Fig.9

Fig.9.Buffer<sup>[7]</sup>

# IV. SIMULATION RESULTS

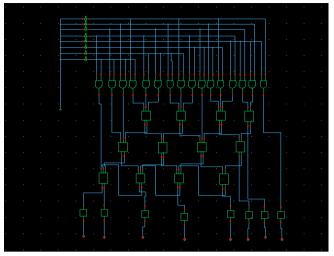

The proposed multiplier is synthesized using CADENCE 5.1.0 EDA tool and simulated using spectre virtuoso.Fig.10 shows the RTL schematic diagram of the proposed multiplier in cadence.

Published By: Blue Eyes Intelligence Engineering & Sciences Publication (BEIESP) © Copyright: All rights reserved.

Retrieval Number: B7405129219/2020©BEIESP DOI: 10.35940/ijitee.B7405.019320 Journal Website: <u>www.ijitee.org</u>

International Journal of Innovative Technology and Exploring Engineering (IJITEE) ISSN: 2278-3075 (Online), Volume-9 Issue-3, January 2020

# Fig.10.Technology diagram of developed system in cadence

Below figure shows the transient response of the proposed 4 bit multiplier. It shows partial product of the multiplier (Prod0, Prod1, Prod2, Prod3, Prod, Prod5, Prod6, Prod7).

Fig.11.Tranisent response of the multiplier

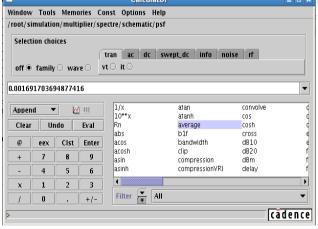

Below figures shows the power and delay calculation in cadence.

Fig.12.Power calculation in cadence

| root/s         | imulatio       | n/multi           | pher/s             | perior, serieritario,                       |                                                             |                                             |  |

|----------------|----------------|-------------------|--------------------|---------------------------------------------|-------------------------------------------------------------|---------------------------------------------|--|

| Select         | tion cho       | ices              |                    |                                             |                                                             |                                             |  |

|                |                |                   |                    | tran ac dc                                  | swept_dc info noi                                           | se rf                                       |  |

|                | A              |                   |                    | vt 0 it 0                                   | strept_ue nuo noi                                           | л п                                         |  |

| off            | family         | ⊖ wav             | e 🔍                |                                             |                                                             |                                             |  |

|                |                |                   |                    |                                             |                                                             |                                             |  |

| 1.04998        | 3733940        | 26098F-           | . <b>q</b>         |                                             |                                                             |                                             |  |

|                |                |                   | 5                  |                                             |                                                             |                                             |  |

|                |                | _                 | -                  |                                             |                                                             |                                             |  |

| Appen          | nd 🔻           | _                 | )                  | 1/x                                         | atan                                                        | convolve                                    |  |

| )              | ũ.             | . 14              |                    | 10**x                                       | atanh                                                       | COS                                         |  |

| Appen<br>Clear | ũ.             | _                 | -                  | 10**x<br>Rn                                 | atanh<br>average                                            | cos<br>cosh                                 |  |

| Clear          | Ur             | r 📈               | Eval               | 10**x<br>Rn<br>abs                          | atanh<br>average<br>b1f                                     | cos<br>cosh<br>cross                        |  |

| )              | ũ.             | . 14              |                    | 10**x<br>Rn<br>abs<br>r acos                | atanh<br>average<br>b1f<br>bandwidth                        | cos<br>cosh<br>cross<br>dB10                |  |

| Clear          | Ur             | r 📈               | Eval               | 10**x<br>Rn<br>abs<br>r acos<br>acosh       | atanh<br>average<br>b1f<br>bandwidth<br>clip                | cos<br>cosh<br>cross<br>dB10<br>dB20        |  |

| Clear<br>@     | Ur<br>eex<br>7 | r do<br>Clst<br>8 | Eval<br>Enter<br>9 | 10**x<br>Rn<br>abs<br>acos<br>acosh<br>asin | atanh<br>average<br>b1f<br>bandwidth<br>clip<br>compression | cos<br>cosh<br>cross<br>dB10<br>dB20<br>dBm |  |

| Clear<br>@     | Ur             | ndo<br>Clst       | Eval<br>Enter      | 10**x<br>Rn<br>abs<br>r acos<br>acosh       | atanh<br>average<br>b1f<br>bandwidth<br>clip                | cos<br>cosh<br>cross<br>dB10<br>dB20        |  |

| Clear<br>@     | Ur<br>eex<br>7 | r do<br>Clst<br>8 | Eval<br>Enter<br>9 | 10**x<br>Rn<br>abs<br>acos<br>acosh<br>asin | atanh<br>average<br>b1f<br>bandwidth<br>clip<br>compression | cos<br>cosh<br>cross<br>dB10<br>dB20<br>dBm |  |

Fig.13.Delay calculation in cadence

#### **Table I. Comparison Of Different Multipliers**

| No | Multiplier                                        | No of<br>transistors | Power<br>in<br>mW | Delay<br>in<br>ns |

|----|---------------------------------------------------|----------------------|-------------------|-------------------|

|    | Using<br>Conventional                             |                      |                   |                   |

|    | CMOS Full                                         |                      |                   |                   |

| 1  | Adder                                             | 392                  | 0.0058            | 3.834             |

| 2  | Using Hybrid<br>Full Adder<br>(Existing)          | 264                  | 0.00224           | 3.0603            |

| 3  | 4-bit Dadda<br>Multiplier using<br>Compressor     | 376                  | 1.172             | 0.353             |

| 4  | DADDA Tree<br>Multiplier Using<br>Adiabatic Logic | -                    | 77                | -                 |

| 5  | 4-bit Static<br>CMOS based<br>DADDA<br>Multiplier | 316                  | _                 | -                 |

| 6  | Proposed<br>Multiplier                            | 248                  | 0.00169           | 1.0409            |

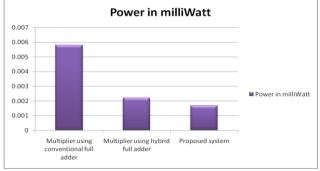

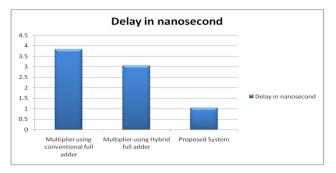

Table I shows the comparison of performance parameters such as power consumption, critical path delay and number of transistors of different multipliers using different types of full adders. From this table it is observed that the circuit complexity of proposed multiplier is less and also the power consumption of the multiplier is  $1.69\mu$ W and critical path delay of the proposed multiplier is 1.04ns which is very less when compared with the other existing multipliers.

Fig.14 and Fig.15 shows the graphical representation of powerand delay.

Fig.14. Comparison of power in mW

Published By: Blue Eyes Intelligence Engineering & Sciences Publication (BEIESP) © Copyright: All rights reserved.

Retrieval Number: B7405129219/2020©BEIESP DOI: 10.35940/ijitee.B7405.019320 Journal Website: <u>www.ijitee.org</u>

# VLSI Architecture of High Performance Multiplier for High Speed Applications

# Fig.15.Comparison of delay in nano second

Table II shows the logic utilization of various modules in 4 bit multiplier.

Table II. Logic Ultilazation Of Various Modules

| Module                                                           | No of<br>transistors | Technique used                 |

|------------------------------------------------------------------|----------------------|--------------------------------|

| Full adder(area and<br>power efficient single<br>bit full adder) | 80                   | Sum: GDI XOR<br>Carry: PTL XOR |

| Half adder                                                       | 40                   | CMOS Process<br>technology     |

| Buffer                                                           | 32                   | CMOS Process<br>technology     |

| AND gate                                                         | 96                   | CMOS Process<br>technology     |

# V. CONCLUSION

The proposed 4 bit multiplier with low power, minimum delay and optimum circuit complexity is being designed with hybrid efficient single bit 3-input binary digits adder circuit. In three input binary digits adder circuit, low power consumption and minimum propagation delay are achieved through PTL and GDI technique. Minimum response time the maximum throughput is achieved using hybrid three input binary digits adder circuit. Due to usage of dadaalgorithm propagation delay is reduced. The proposed  $4\times4$  multiplier has average power consumption of  $1.69\mu$ W with a propagation delay of 1.04 ns. These calculated parameters are lesswhen compared to the available multiplier design.

# REFERECNES

- Sumant Mukherjee, Dushyant Kumar Soni"Energy Efficient Multiplier for High Speed DSP Application"IJCSMC, Vol. 4, Issue. 6, pg.66 – 75, June 2015.

- Itawadiya, A.K, Mahle, R,Patel, V,Kumar, D, "Design a DSP operations using vedic mathematicInternational Conference on," Communications and Signal Processing (ICCSP), 2013, vol.3, no.5, pp.897-902, April 2013.

- Saokar, S.S.; Banakar, R. M.; Siddamal, S., "High speed signed multiplier for Digital Signal Processing applications," IEEE International Conference on Signal Processing, Computing and Control (ISPCC), vol.15, no.17, pp.1-6, March 2012.

- C.S. Wallace, "A Suggestion for a Fast Multiplier", IEEE Transaction On Electronic and Computer, Vol.EC-13, PP. 14-17, February 1964.

- Prashant D. Pawale, Venkat N Ghodke, High speed Vedic multiplier design and implementation on FPGA, International Journal of Applied Research vol.1, no.7, pp:239-2442015.

- Muhammad HussnainRiaz, Syed Adrees Ahmed, QasimJavaid, Tariq Kamal, "Low Power 4×4 Bit-Multiplier Design using Dadda Algorithm and Optimized Full-Adder", IEEE International bhurban conference on applied sciences and technology(IBCAST),2018.

- 7. RishabGoyal, Sanjeev Sharma, "Single Bit Hybrid Full-Adder Cell by Gate Diffusion Input and Pass Transistor Logic(PTL)

Technique,"IEEE International Conference On Advances In Electrical Technology For Green Energy,2017.

- S. Z. Naqvi, S. Z. Hassan and T. Kamal, "A power consumption and area improved design of IIR decimation filters via MDT," International Conference on Intelligent Systems Engineering (ICISE), Islamabad, pp. 146-151, 2016.

- Sulieman, MawahibHussein,Mahmoud, Mariam,Raafat, RemondaReda, Gehad, "Designand Simulation of a Nano-scale Threshold-Logic Multiplier" TEM Journal. Volume 8, Issue 2, Pages 333-338, ISSN 2217-8309, DOI: 10.18421/TEM82-03, May 2019

#### **AUTHORS PROFILE**

**Dr.J.M.MATHANA** obtained her B.E Degree in Electronics and Communication Engineering, M.E Degree in VLSI Design and Ph.D Degree in Information and Communication from Anna University, Chennai. She has over 25 years of rich experience in academic

arena and industryCurrently, she is working as Principal and Professor, ECE Department in Chennai Institute of Technology, Chennai - 69. Her research interests include the Error Corrective Coding, Interleavers, Wireless Communication and VLSI Design. Her strong commitment towards research is reflected in her contribution of more than 100 international and national publications. She is the recognized research supervisor in Anna University, Chennai and supervising 6 research scholars in Anna University, Chennai in the field of Information and Communication. She is the distinguished member of the Indian Society of Technical Education (ISTE) and senior IEEE member. She is the reviewer in international journals like, International Journalof Institution of Engineering and Technology (IET), International Journal of Computers Communications and Control, International Journal of Advanced Research Trends in Engineering and Technologyand ICTACT Journal. She has numerous workshops/seminars/national and international conferences to her credit.

**Dr R.Menaka** obtained her Ph.D. Degree in the faculty of Information and Communication Engineering from Anna University, Master Degree in Applied Electronics from Anna University, Bachelor Degree in Electronics and Communication Engineering from Madras University.

She has around 19 years of teaching experience. Her area of Interest includes Mobile Ad hoc Networks, Wireless Networks and Image & Signal Processing.

**Dr.R.DHANAGOPAL**, was born in Namakkal, TamilNadu, India. Graduated B.E(ECE) from the Jayaram College of Engineering and Technology, Trichy, Bharathidasan University, India, in 2004, ME degree in Communication Systems from Jayaram College of

Engineering, Trichy, Anna University, Chennai, India , in 2008. He received doctorate in Low Power VLSI Design, in Anna University, Chennai, India in 2018. He Published 13 International Journals. Presented 12 papers in various National and International Conferences conducted in various countries like Singapore, China and Japan. Currently he is working as Associate Professor, Department of Electronics and Communication Engineering, Chennai Institute of Technology, Chennai-69. His research interest includes Low power design and testing VLSI Circuits, Image Processing, IoT, Data Mining, Antenna Design.

**Dr.B.Sundarambal** obtained her Ph.D Degree in the faculty of Information and Communication Engineering from Anna University, Master degree in Computer Science and Engineering from Anna University, Bachelor Degree in Electronics and Communication Engineering

from Bharathiar University. She published papers in 4 international Journals. Her area of interest includes Computational Intelligence and Computer Vision. She is life member of ISTE.

Published By: Blue Eyes Intelligence Engineering & Sciences Publication (BEIESP) © Copyright: All rights reserved.

Retrieval Number: B7405129219/2020©BEIESP DOI: 10.35940/ijitee.B7405.019320 Journal Website: <u>www.ijitee.org</u>