# Gain Error end DNL for Testing ADCs: Optimization in Time Domain

Manish Jain, R P Kumawat

Abstract – Optimization in ADC is an important component which predicts overall accuracy of a system using it. Signals are in real time nature and it is necessary to convert these signals in digital form to interpret with digital form of signals and microcomputer based systems. ADC is used to carry out these conversions process from analog to digital.

Determination of parameters of an ADC such as DNL, INL, SNR and ENOB are necessary for complete dynamic analysis and characterization of ADC. In frequently, application prerequisite input to an Analog to digital converter is time varying which requires determination of its parameters at corresponding frequency and different test conditions

In order to test an ADC, it is necessary to first determine its code transition levels. Further Gain error, DNL are estimated using code transition level based on histogram technique. If there is an code transition level error introduced then effect of this error leads to error in estimate of gain, offset, DNL and ENOB. Further estimation of variance in different parameter values is analyzed in the proposed work.

Keywords- Analog-to-digital converter, Effective No. of Bit, Histogram Technique, Offset Error, Gain Error.

#### I. INTRODUCTION

For ADC testing histogram method is most frequently used. this method introduced to test various ADC parameters like INL, DNL, offset and gain error. The transition level for its parameter occurs at 0.5 LSB. The gain error shows the how a actual and ideal transfer function deviates. Histogram is created through software methods followed by computation of code levels using large no. of samples The test methodology followed during development of new algorithm of testing is to simulate ADC transfer function with software. The effect of different error is calculated by simulation (with software) to meet practical conditions. ADC testing using different nonlinearities maps the actual transfer function and characteristics of an ADC.

Revised Manuscript Received on January 30, 2020.

\* Correspondence Author

**Dr. Manish Jain\***, Associate Professor, EEE Department, Mandsaur University, Mandsaur (M.P.), India. Email: - manish.jain@meu.edu.in

**Prof. R P Kumawat,** Assistant Professor, EEE Department, Mandsaur University, Mandsaur (M.P.), India.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license <a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>

## II. COMPUTATION OF CODE TRANSITION LEVEL

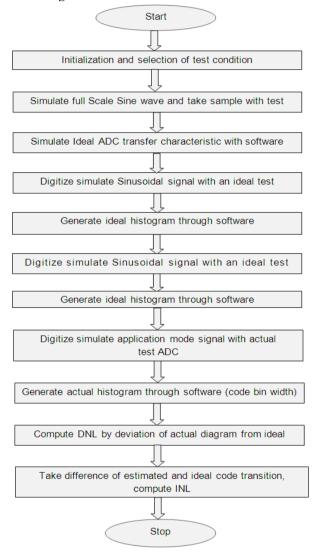

Different steps for computation of basic histogram are shown in figure 1.1

Figure 1.1 Code transition level histogram

Code transition level of ADC can be estimated using

T[k], of an N bit ADC is given as [7]

$$\hat{T}[k] = O - ACos \left[ \frac{\prod Ch[K-1]}{St} \right], K=1,2...2^{N-1}$$

(1)

The cumulative histogram defined by:

$$C_k = \sum_{i=0}^{k-1} h[i] \tag{2}$$

### Gain Error end DNL for Testing ADCs: Optimization in Time Domain

Where, h[i] = samples recorded in code bin

M = No. of samples

A = Amplitude of input sine wave, and

C = DC offset of input sine wave,

To easiest the process, offered normalized Code bin width is given by

$$\hat{W}[k] = \hat{T}[K+1] - \hat{T}[K]$$

(3)

Where.

T[k] = Transition voltage

U[k] = Normalized transition voltage,

Let U[k] = U for further process

For a large number of samples estimated normalized transition voltage is computed by

$$\begin{split} \mu_{U_{K+1}} &= -Cos\left(\pi\frac{\mu_{C_K}}{M}\right) + \frac{\pi^2}{M^2}Cos\left(\pi\frac{\mu_{C_K}}{M}\right)\frac{\sigma_{C_K}^2}{2} + .... \\ & ..... \\ & + (-1)^{n/2}\frac{\pi^n}{M^n}Cos\left(\pi\frac{\mu_{C_K}}{M}\right)\frac{\mu_{n_{C_K}}}{\perp n} \end{split}$$

(4)

#### III. ESTIMATION OF OFFSET AND GAIN ERROR

Application mode input is made up of various sinusoidal component determined by FFT algorithm. As gain error in ADC is dependent on input frequency, so it is necessary to compute gain error for different sinusoidal component of application mode input and appropriate gain error corrections are to be applied. First for each sinusoidal component code transition level is computed by standard histogram method as reported earlier. Based upon code transition level gain error is computed. For designed transfer function the gain of estimation is offered by [6]:

$$G = \frac{2^{N} - 2}{T[2^{N} - 1] - T[1]}$$

(5)

For an N bit ADC gain are for ADC are offered as

$$G_{i} = \frac{H_{ideal} - L_{ideal}}{H - L} \tag{6}$$

Meanwhile the same offset error of ADC is designated as:

$$\hat{O}_e = L_{ideal} - \hat{G}.\hat{L}$$

(7)

Where,

$\overset{\wedge}{L}$  is the last estimated voltage,  $\overset{\scriptscriptstyle\Lambda}{L}=\overset{\scriptscriptstyle\Lambda}{T}_{2^N-1}$

$\overset{\wedge}{F}$  is the first estimated transition voltage,  $\overset{\wedge}{F}=\overset{\wedge}{T}_1$ H(0) is number of hits at lower codes and  $H_{(2^{N}-1)}$  is number of hits at upper codes for each sinusoidal component applied to n-bit ADC. Hence offset for each sinusoidal component is computed and algebraically summed to get resultant offset for application mode input. Further corrections are applied for various errors like gain

offset for ADC transfer characteristics corresponding ADC outputs are generated. These errors are presents in the ADC transfer characteristic may be minimized. Meanwhile, the Nonlinear error cannot be comprised to appropriate level. Hence nonlinearity error is estimated in this paper for application mode input.

#### IV. NONLINEARITY ESTIMATION

DNL error is defined as actual step width an ideal value of 1

$$DNL(i) = \frac{H(i)}{Hideal(i)}$$

(8)

Where

$$i = 1, 2, \dots, 2^{N}-2$$

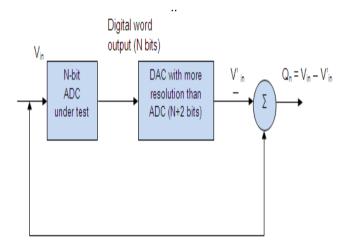

Frequency of occurrence of each code can be computed by N bit ADC under test and DAC with resolution less than (N +2) bits are computes for corresponding stimuli input signal

Figure 1.2 ADC input-Output Test

The modeling of an n bit ADC with different gain and DNL errors cab be followed by quantized the transfer function of practical a ADC.

The DNL and INL for first stimuli function such as sine wave may be computed by following equations computed by algorithmic interpretation in the data input for sinusoidal waves.

$$\hat{h}'_{1}(x_{0}) = Y_{1}(0) + Y_{2}(0)

\hat{h}'_{1}(x_{1}) = 2i^{2}Y_{1}(1).T_{1}(\cos\theta_{1})

\hat{h}'_{1}(x_{2}) = 2i^{2}Y_{1}(2).T_{2}(\cos\theta_{2})

\hat{h}'_{1}(x_{3}) = 2i^{2}Y_{1}(3).T_{3}(\cos\theta_{3})

\hat{h}'_{1}(x_{4}) = 2i^{2}Y_{1}(4).T_{4}(\cos\theta_{4})

\hat{h}'_{1}(x_{5}) = 2i^{2}Y_{1}(5).T_{5}(\cos\theta_{5})

\hat{h}'_{1}(x_{6}) = 2i^{2}Y_{1}(6).T_{6}(\cos\theta_{6})$$

(9)

And INL h(x) for  $II^{nd}$  sine wave can be defined similarly as:

Published By:

#### SIMULATION RESULTS AND DISCUSSION

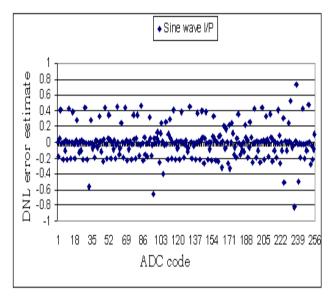

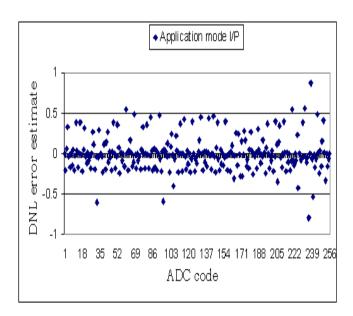

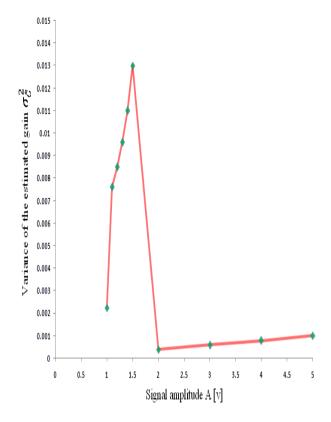

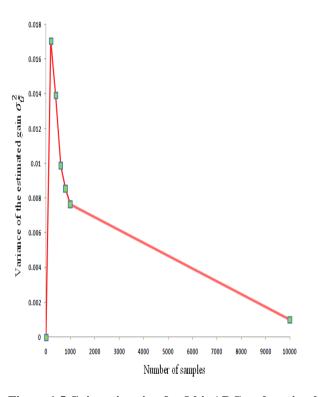

The validity of our algorithm designed can be computed and analyzed for DNL and gain error testing The Error computed can be carried out for further experimental analysis and the impression for error for different samples are shown below in the figure 1.3, 1.4, 1.5.

Figure 1.3: DNL Error Estimated

Figure 1.4 Gain estimation for 8 bit ADC

Figure 1.5 Gain estimation for 8 bit ADC under stimuli input

Published By:

© Copyright: All rights reserved.

#### Gain Error end DNL for Testing ADCs: Optimization in Time Domain

#### VI. CONCLUSION

In the proposed research work the estimation of gain and DNL error are computed with the tolerance effect of variance in the signal in the time domain analysis .the experimental analysis is carried out by additive noise aviation in the effect of standard deviation for typical 8 and 10 bit ADC gain and DNL analysis.

The full scale stimuli like sinusoidal wave are applied to 1 MHZ frequency for simulation. The sampling frequencies are modulated at 5 MHz.

Predefined large numbers of samples are taken and histogram is constructed through software followed by computation of code levels.

#### REFERENCES

- H.F. Lundin, P. Handel, Skoglund, "Bounds on the performance of analog to digital converter look up table post-correction". International Journal of measurement, ELSEVIER, article in press, 2008

- Minguri Zhang, Yao Han, Fel Geng Chenghui Zhang "Research on high speed ADC test and evaluation system", International conference 2017 IEEE.

- Guan Cheng Wang, Yan Zhu, Chi- hang chan, "Gain error calibration for Two sep ADCs: Optimization either in Accuracy or chip area" IEEE transaction on Low power VLSI, 2017.

- Yuan, Tang, Miao," Analog to digital converter performance testing based on MATLAB: IOP Conference series; Earth and Environment science, 2019.

- Martins, Serra: "Automated ADC characterization using the histogram test stimulated by Guassian noise. IEEE transaction on Instrumentation and measurement. 48(2), 471-474 (1999)

- R.S. Gamad and D.K. Mishra, "Gain error, offset error & ENOB estimation of ADC using histogram technique". International journal of Measurement, ELSEVIER, Vol. 42, pp 570-576, May, 09

- Andre Alegria and A. Manuel "Overdrive In the ramp Histogram test ADC's", IEEE transaction on instrumentation & measurement, vol.54, No 6, Feb. 2005.

- N. Bjorsell, P. Handel, "Truncted Guassian noise in ADC histogram tests", International Journal on Measurement, ELSEVIER, Vol. 40, pp 36-42, 2007

### **AUTHORS PROFILE**

**Dr. Manish Jain** obtained Ph.D. in 2015 in Electronics & Communication. He has vast experiences of about 18 + years. He is life member of IE, CEGR, IAENG and Editorial board members & Reviewer of some International Journal. He has authored 1 research book on DSP. Under his guidance Student project have been sanctioned for Financial Assistance by Department of Science & Technology (DST). Under his guidance 10 M.Tech and 1 PhD has

been awarded. His research interest includes Semiconductor Electronics, Communication, ADC design & Testing, VLSI.

**Prof. RP Kumawat** obtained M.Tech. in 2012 in Digital Communication. He has a vast experience of teaching of about 15 years He has published about 10 papers in Journals and conference of repute. He has attendant many workshops and conferences at national level. His area of interest is Digital Communication and signal processing.