N.Prabakaran, A.Deepika, Y.Gunavardhani, P.Anil kumar

Abstract: : In this paper, four double quality 4:2 blowers are proposed. Double quality blowers implies it has a capacity of exchanging between two modes to be specific correct and rough working modes. Double Quality blowers have capacity to give the higher speeds and will bring down the precision. To plan this model ordinary dada multiplier is taken as reference. Multiplier involves huge region yet it performs rapid tasks. To decrease the downsides in the framework we have actualized surmised double quality 4:2 blowers utilizing dada multiplier.

Keywords: 4:2 compressor, delay, speed, dada multiplier.

#### I. INTRODUCTION

Digital Signal Processing and Embedded applications, Accumulators structure a noteworthy square. Speed up chooses processor speed. So fast aggregators are required in the processors for certain executions. For increasing the speed of duplication different counts are used. Duplication is a most used action in many preparing structures. To outline a result which suggests thing, a number which is multiplicand is added to itself different events as demonstrated by another number which is a multiplier [1]. In any case, the execution of multiplier circuit works at low speed despite the fact that it has extremely large equipment assets. Essentially accumulators have impressive power utilization has a huge region and inactivity is additionally long.

All around, low power propagator arrangement has critical part in low power VLSI structure plan because of the above properties. Aggregator is ordinarily the slowest part and devours more district so a structure would be regularly constrained by execution of multiplier. Also generally involves 3 phases. Those are:

#### 1) Partial Product age

Revised Manuscript Received on January 30, 2020.

\* Correspondence Author

N.Prabakaran\*, Associate Professor, Department of ECE, Koneru Lakshmaiah Educational Foundation, Guntur, AP, India. prabakarkn@gmail.com.

**A.Deepika**, Department of ECE, Koneru Lakshmaiah Educational Foundation, Guntur, AP, India. deepuengg2016@gmil.com

**Y.Gunavardhani**, Department of ECE, Koneru Lakshmaiah Educational Foundation, Guntur, AP, India. <a href="mailto:gunavardhani110@gmail.com">gunavardhani110@gmail.com</a>

P.Anil kumar, Department of ECE, Koneru Lakshmaiah Educational Foundation, Guntur, AP, India. anilkumarraju644@gmail.com

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license <a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>

2) Partial Product decline

#### 3) Final development

In [2], about the incomplete item age has been plainly clarified.

In a few Microprocessors and Digital Signal Processing implementations. Accumulation is the fundamental math activity.

The interest for fast multipliers has gotten profoundly noticeable as Digital Signal processing Systems require multipliers which lies in accordance with the basic way.

The upgraded speed prompts expanded power utilization, hence, control sparing models go to be the decision of future. For advancement of numerous novel circuits this technique has given a route for the improvement of these which lessens the power scattering of multipliers without trading off speed and execution of multiplier. By and large any multiplier has 3 phases which are portrayed in the presentation part. In the principal arrange, a little bit at a time duplication is done among multiplicand and multiplier to create the fractional items. The subsequent stage is generally entangled and decides the speed of by and large accumulator in term this is the most remarkable stage. 4:2 and 5:2 blowers have been broadly utilized in fast accumulators to bring down the inertness of incomplete item collection arrange. The 4:2 blower is ideal for the advancement of composed Wallace tree with low multifaceted nature because of its normal interconnection[3]. In [4], the Wallace tree development technique generally includes the fractional items in a tree

like style to deliver two lines of halfway items which had been included the last stage. The Wallace tree is quick as the basic way postpone which is relative to the logarithm of the quantity of bits in an accumulator. There exists various approaches to build the Wallace Tree. The unmistakable technique is it considers every one of the bits in every section at once and packs them into two bits in every four lines one after another and compacting them in fitting way. In this manner the blowers structures basic prerequisite of fast accumulators. The speed, region and potential utilization of the accumulators will be in accordingly extent to the effectiveness of the blowers. Along these lines, to satisfy the need of little district low power high throughput equipment, this paper outfits novel plans of 4:2 blowers with least number of transistors.

#### A. DADDA MULTIPLIER

Fast augmentation is essential prerequisite for computerized frameworks. In ongoing patterns because of their higher paces, the segment pressure accumulators are prevalent for rapid calculations. The primary section pressure multiplier was presented by Wallace in the year 1964. He reduced the midway aftereffect of N pushes by gathering into sets of three line set and two line set using (3,2) and (2,2) counters independently.

In the year 1965, Dadda had modified the methodology of Wallace by beginning with the definite position of (3,2) and (2,2) counters in the most extreme basic way deferral of the multiplier[5]. As the closer re-examination of Wallace and Dadda accumulators has done which demonstrated that the Dadda multiplier is somewhat quicker than the Wallace multiplier and the equipment[6] execution required for Dadda multiplier is lesser than the equipment usage of Wallace multiplier. As the Dadda accumulator has a quicker presentation, we actualize the proposed strategies in the equivalent.

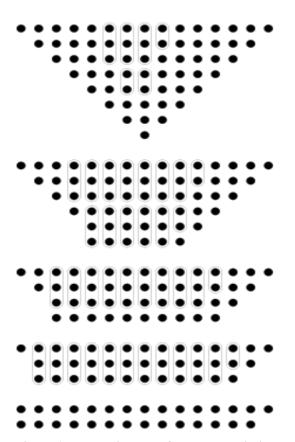

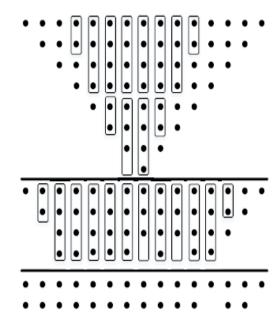

Figure 1: Block Diagram of Dadda Multiplier

The segement pressure accumulators have complete deferrals in which the logarithm of operand word lengths are relative which is not typical for the display aggregators which have speeds comparing to the word length. The total delay of the accumulator can be seperated in three segments: in view of the PPG, The Partial product Summation tree, lastly because of the Final Adder. These accumulators have subsequently 3 stages[7]:

- 1) Accumulation of bit by bit in one of the contentions by each piece of another contention yielding  $n^2$  of the results.

- 2) Reduction of incomplete items are finished by layers in adders that is full and half adders.

- 3) Wires that should be assembled with two bits are included with an ordinary vipers.

#### II. RELATED WORK

#### A. 4:2 COMPRESSOR

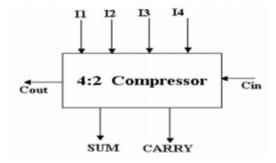

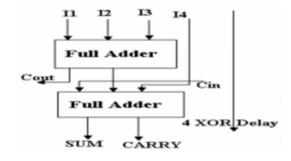

The 4:2 blower structure generally packs five partial things bits into three. The designing is related so four of the wellsprings of data are beginning from a comparable piece position of the weight j while one piece is supported from the neighboring position j1 (known as pass on in). In [8],the 4:2 blower contains 2 yields in which one piece in the position j and two bits in the position j+1. This structure is called blower since it packs four fragmentary things into two (while using one piece evenly related between bordering 4:2 blower). Regularly 4:2 blower can in like manner be manufactured using 3:2 blowers. It involves two 3:2 blowers(full summers) which are placed in game plan and incorporates an essential method for 4 XOR delays. This use is better and incorporates fundamental path deferment of three XOR's, along these lines decreasing the essential route delay by 1 XOR. The yield Cout, being self-governing of Cin revives the pass on save summation of fragmentary things.

Figure 2. Block diagram of 4:2 compressor

Figure 3. 4:2 Compressor design using Full Adder

Figure 4: Alternative Implementation of 4:2 Compressor with 3 XOR delay

In Existing Design, two plan of 4:2 blowers are exhibited and utilized in fractional item decrease tree of four variations of 8x8 Dadda multiplier. The significant downside of the proposed blowers is that they give nonzero yield for zero quality inputs, which takes to a great extent influences the mean relative blunder. For using the proposed inexact blowers, four unique plans are proposed and investigated for a Dadda Multiplier.

Disadvantages: More error,[9] Practical time usage is confounded, More complexity nature in Logic Simplification.

#### III. PROPOSED TECHNIQUE

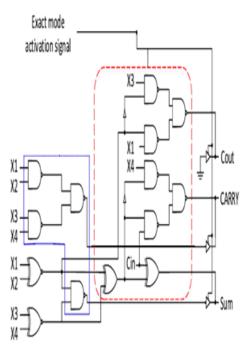

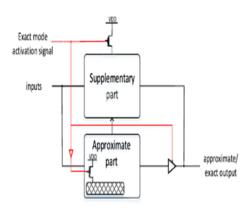

In proposed design we implement four DQ reconfigurable inexact 4:2 blowers, which have ability to change between the correct and estimated working modules in the execution time. In the design of dynamic quality configurable parallel convolutors the blowers might be used. The basic structures of the proposed compressors contains two pieces of surmised and advantageous which means supplementary. In the approximate mode, just the estimated module is dynamic though in definite working module, just the rough module is dynamic whereas in the accurate working module, the supplementary part alongside certain segments of the inexact module is included.

#### PROPOSED SYSTEM BLOCK DIAGRAM:

Figure 5: Dadda multiplier using proposed designs

In Proposed System Technique, these inexact blowers are then utilized in the rebuilding module.

#### Advantages:

Error rate is dimnished, Improvement in Significant execution when contrasted to a precise blower concerning delay, number of transistors, power utilization is decreased[10].

#### **Real Time Examples:**

It's basically utilized Digital Signal Processing. Power efficient system like satellite, mobile phones.

#### **B. 4:2 COMPRESSOR**

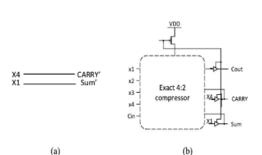

4:2 and 5:2 blowers are generally utilized to decrease the deferral of fractional item summation phase of parallel accumulators. Some blower structures, which have been streamlined for at least one plan parameters have been proposed. The 4:2 compressor has four data sources (x1-x4) alongside an info carry ( $C_{in}$ ), and two yields (whole and carry) alongisde a yield  $C_{out}[3]$ .

Two sequentially associated full adders are the interior structure of a definite 4:2 blowers[11]. In the above structure, the loads of the considerable number of information sources and the aggregate yield are same while the loads of the convey and  $C_{out}$  yields are one parallel piece position higher. The yields sum, [10] carry and  $C_{out}$  are acquired from:

$$\begin{split} & \text{Sum=} (\text{x1}) \ \text{XOR}(\text{x2}) \ \text{XOR}(\text{x3}) \ \text{XOR}(\text{x4}) \ \text{XOR}(\text{C}_{\text{in}}). \\ & \text{Carry=}((\text{x1}) \ \ \text{XOR}(\text{x2}) \ \ \text{XOR}(\text{x3}) \ \ \text{XOR}(\text{x4}))\text{C}_{\text{in}} \ \ +(\sim((\text{x1}) \ \ \text{XOR}(\text{x2}) \ \text{XOR}(\text{x3}) \ \ \text{XOR}(\text{x4})))\text{x4}. \\ & \text{C}_{\text{out=}}((\text{x1}) \ \ \text{XOR}(\text{x2}))\text{x3+}(\sim(\text{x1}) \ \ \text{XOR}(\text{x2}))\text{x1}. \end{split}$$

#### C. PROPOSED 4:2 BLOWERS

The advance Dual Quality 4:2 blowers are being operated at twice exactness modes of approximate and Exact.

Figure 6: Block Diagram of proposed approximate 4:2 compressors. The approximate indicates the componenets, which are not shared between this and supplementary parts.

Figure 7: (a) Approximate part and (b) Overall structure of DQ4:2  $C_1$ .

# The figure 7, comprises of two fundamental parts in particular surmised and Supplementary [11]. Just the Approximate part is misused during the approximated mode where as valuable part is control gated. The benificial and a few pieces of rough parts are used during the careful working mode. In the proposed strucutre a large portion of the segments of estimated part are additionally utilized the exact working mode to dimnish the power utilization and territory.

### IV. COMPARISION BETWEEN NORMAL DADDA MULTIPLIER AND DADDA MULTIPLIER USING 4:2 COMPRESSOR

| Method Name                     | Area in Number of LUT |            |            | Memory in Kilobytes     | Delay        |                             |                            |  |

|---------------------------------|-----------------------|------------|------------|-------------------------|--------------|-----------------------------|----------------------------|--|

| Multiplier Name                 | Lut                   | Gate Count | Slice<br>s | Size                    | Delay        | Gate or<br>logic<br>delay   | Path or route delay        |  |

| Normal Dadda Multiplier         | 176                   | 1056       | 97         | 243608<br>Kilo<br>bytes | 45.844n<br>s | 19.138 ns<br>41.7%<br>logic | 26.706ns<br>58.3%<br>route |  |

| Dadda Multiplier 4:2 Compressor | 137                   | 822        | 77         | 177360 Kilobytes        | 30.528n<br>s | 14.179ns<br>46.4%<br>logic  | 16.349ns<br>53.6%<br>route |  |

Retrieval Number: C8128019320/2020©BEIESP DOI: 10.35940/ijitee.C8128.019320 Journal Website: www.ijitee.org

#### V. RESULT AND DISCUSSION

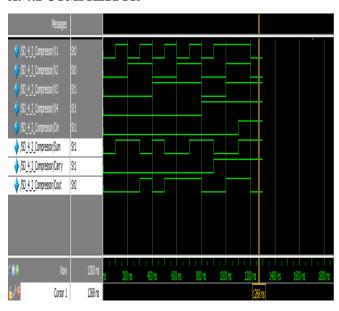

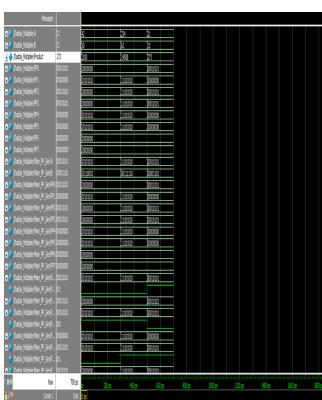

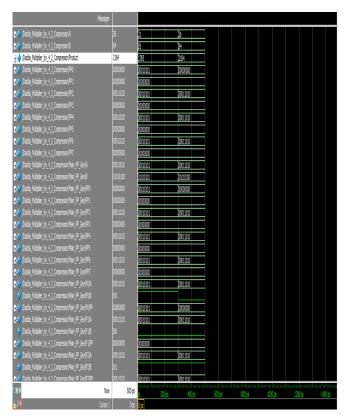

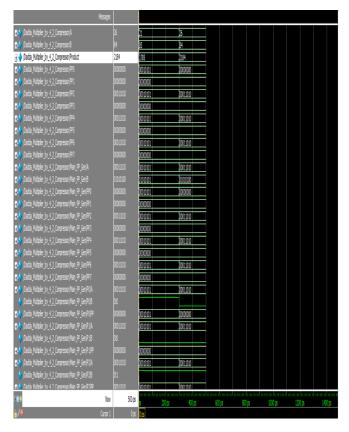

In this paper the proposed plan is executed utilizing the verilog HDL code and recreated and sintegrated utilizing Xilinx ISE. Almost for two and half decades, Xilinx has been , at the cutting edge of the programmable logic revolution, with the innovation and proceeded with relocation of FPGA stage innovation. The Xilinx Integrated Software Environment (ISE) is a ground breaking[12], and complex arrangement of devices. The reason for this guide is to enable new clients to get standard utilizing ISE to compile their structures.

#### A. 4:2 COMPRESSOR

#### **B. NORMAL DADDA MULTIPLIER**

# C. DADDA MULTIPLIER DESIGN USING NORMAL 4:2 COMPRESSOR

# D. DADDA MULTIPLIER USING APPROXIMATE 4:2 BLOWER

Journal Website: www.ijitee.org

#### VI. CONCLUSION

In this paper, we presented a dadda multiplier with new inexact blowers. Using this estimated blower we can dimnish the region and power utilization likewise in the dadda multiplier. Mainly for rapid duplications we utilize this convolutor.

By utilising this estimated blowers we can lessen the intricacy in the circuit also. Compared to ordinary dadda multiplier and this advanced dadda multiplier atleast 20% of the defer will be decreased. However, the look up tables and number of gates are likewise dimnished.

#### REFERENCES

- 1 P. Kulkarni, P. Gupta, and M. Ercegovac, "Trading accuracy for power with an underdesigned multiplier architecture," in Proc. 24th Int. Conf. VLSI Design, Jan. 2011, pp. 346–351.

- Kumar M.S., Tulasi S.K., Srinivasulu N., Yedla G.S.K.N., Raghuveer E., Kishore K.H., "Improvement of the efficiency of booth multiplier ",2018, International Journal of Engineering and Technology(UAE), Vol: 7,Issue: 3.34 Special Issue 34, pp: 316 to:: 322, DOI: ,ISSN:

- M. Margala and N.G. Durdle, "Low-power low-voltage 4-2 compressors for VLSI Applications," in Proc. IEEE Alessandro Volta Memorial Workshop Low-Power Design, 1999, pp.84-90.

- C.H. Lin and I.C. Lin, "High accuracy approximate multiplier with error correction," in Proc. IEEE 31st Int. Conf. Comput. Design(ICCD), Oct.2013, pp. 33-38.

- "Implementation of Wallace Tree Multiplier Using Compressor" by Naveen Kr. Gahlan, Prabhat Shukla and Jasbir in Int. J. Computer Technology & Applications, Vol 3(3), 1194-1199 ISSN: 2229-6093.

- Srikanth Reddy P., Satyanarayana P., Sai Krishna G., Divya K., Hardware implementation of variable digital filter using constant coefficient multiplier for SDR applications ", 2018, International Journal of Engineering and Technology(UAE) ,Vol: 7 ,Issue: 1.5 ,pp: 146 to:: 151 ,DOI: ,ISSN: 2227524X

- "A high speed binary floating point multiplier using Dadda algorithm." By Jeevan, B., Narender S., Dr. C.V. Krishna Reddy and Dr. K. Sivani in International Multi-Confeence IEEE, 2013 on Automation, Computing, Communication, Control and Compressed Sensing (iMac4s),2013.

- C.H. Lin and I.C. Lin, "Ultra low-voltage low-power CMOS 4-2 and 5-2 compressors for fast arithmetic circuits," IEEE Trans. Circuits Syst. I, Reg. Papaers, Vol:51, no.10, pp.1985-1997, Oct. 2004.

- Srikanth Reddy P., Satyanarayana P., Sai Krishna G., Divya K. .," Hardware implementation of variable digital filter using constant coefficient multiplier for SDR applications ", 2018, International Journal of Engineering and Technology(UAE) ,Vol: 7 ,Issue: 1.5 ,pp: 146 to:: 151 ,DOI: ,ISSN: 2227524X

- 10. Kumar P.K., Rao P.P., Kakarla H.K., Optimal design of reversible parity preserving new Full adder / Full subtractor, 2017 Proceedings of 2017 11th International Conference on Intelligent Systems and Control, ISCO 2017, pp: 368-373, DOI: 10.1109/ISCO.2017.7856019, ISBN: 9.78151E+12

- "Switching Mode Based 4:2 Compressors for Dynamic Accurate Reconfigurable Multipliers," by Naveen. V.S, S.Anjaneyulu, in IJSRCEIT, Vol 3: Issue: 6, ISSN: 24.56-3307.

- 12. Yadlapati A., Hari Kishore K., "System Level Verification of advanced extensible interface protocol using Verilog HDL ", 2018, Lecture Notes in Electrical Engineering, Vol: 471, Issue: ,pp: 581 to:: 588, DOI: 10.1007/978-981-10-7329-8\_59, ISSN: 18761100 9.78981E+12

#### **AUTHORS PROFILE**

DOI: 10.35940/ijitee.C8128.019320

Journal Website: www.ijitee.org

Dr. N. Prabakaran working as Associate Professor, Dept. of ECE, KLEF (Deemed University. He received his M.E. Applied Electronics from the University of Sathyabama University, Chennai in 2007. He received his PhD degree from Satyabama University. His

research interests are in wireless communication, energy and mobility management for wireless networks and heterogeneous wireless networks.

A.Deepika pursuing her Bachelor's degree, in Department of Electronics and Communication Engineering in Koneru Lakshmaiah Educational Foundation.

Y.Gunavardhani pursuing her Bachelor's degree, in Department of Electronics and Communication Engineering in Koneru Lakshmaiah Educational Foundation.

P.Anil Kumar pursuing his Bachelor's degree, in Department of Electronics and Communication Engineering, Koneru Lakshmaiah Educational Foundation.