# Impact of Variation of Device Parameters on the Electrical Characteristics of Double-Gate Mosfets

## Samra Jabeen, S. Jha, P. Anuradha

Abstract: Very large scale integrated circuits (VLSI) have been possible owing to the shrinking of metal-oxide semiconductor field-effect transistors (MOSFETs). By reducing the dimensions of the device it is possible to have high density on the chip. This increases the number of logical functions that can be implemented on a given dimension of the chip. Along with the advantages associated with the shrinking of the devices, it also has certain drawbacks commonly known as short-channel effects. Due to these effects, device characteristics deviate from its expected values. There are many techniques through which these deviations can be minimized. One of the promising and highly researched techniques these days is the use of Multi-gate (MG) transistors in VLSI. Double-gate (DG) transistor is one among MG transistors. In DG MOSFET, substrate is surrounded by gates from two opposite sides. This leads to more control over the channel electrons by the gate terminals. In this paper, the consequence of change of various device constraints on the electrical characteristics of the DG MOSFETs will be investigated. Through the results, one can know to what extent the electrical properties changes when the dimensions and/or material properties are changed. This will be very helpful in determining the maximum current associated with those dimensions of DG MOSFETs.

Keywords: Double-gate, Drain current, MOSFET, Threshold voltage, VLSI.

## I. INTRODUCTION

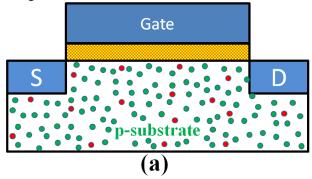

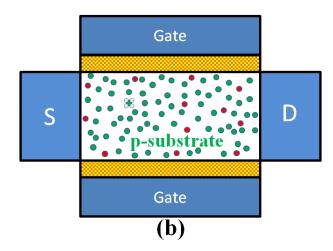

In conventional bulk metal-oxide semiconductor FET (MOSFET), there is unique gate as shown in Fig. 1(a). For increasing the compactness of the transistors on a single chip, the physical dimensions of the MOSFET is reduced. By following this method, the number of transistors has increased in a circuit over the last four decades. This increase in transistors is led by the law proposed by Moore which projected that the amounts of transistors on a single chip will be doubling itself after every approximately two years.

Revised Manuscript Received on January 30, 2020.

Correspondence Author

Samra Jabeen\*, Department of Electronics and Communication Engineering (EDT), S R Engineering College, Warangal, Telangana, India. Email: samrajabeen424@gmail.com

- S. Jha, Department of Electronics and Communication Engineering, S R Engineering College, Warangal, Telangana, India.

- P. Anuradha, Department of Electronics and Communication Engineering, S R Engineering College, Warangal, Telangana, India.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license http://creativecommons.org/licenses/by-nc-nd/4.0/

This law virtually forced the researchers and the industry to come out with newer ways to raise the concentration of transistors on a particular chip.

Previously only the channel length was reduced but when it started showing certain limitations, other methods like reducing the oxide thickness and channel width

Fig. 1. Cross-sectional views of the (a) Conventional Single-gate n-MOSFET and (b) Double-gate n-MOSFET

were also incorporated. The limitations are the short-channel effects which come to picture when the dimensions are such that the source/drain fields start influencing the channel electrons. This affects the electrical behaviour of the MOSFET and it deviates from its intended characteristics.

#### II. LITERATURE REVIEW

In figure 1(a), the view corresponding to cross-sectional projection of conventional bulk n-MOS is shown. Under suitable terminal voltage conditions,

#### Impact of Variation of Device Parameters on the Electrical Characteristics of Double-Gate Mosfets

the conducting electrons form very thin layer of charge carrier layer near the gate and much of the substrate volume is of no use for the conduction. Therefore many techniques have been proposed in the literature [1–5] for the scaling of conventional MOSFETs.

In [6, 7], to have high equivalent gate-oxide thickness, high-K oxide materials as gate materials have been studied. Gate capacitance increases through this technique. In [8], strain has been used to increase the transport properties of the carriers (electrons/holes). By retaining the same dimensions, strained MOSFETs show better electrical properties.

Apart from these, there are reports of the use of multi-gate (MG) MOSFET architectures to follow the path of device miniaturization. There are various types of MG MOSFETs [9, 10] Gate controls the channel electrons and therefore the number of gate affects the electrical properties of the device.

Double-gate (DG) structure MOSFET is as depicted in figure 1(b). In DG devices, the substrate has two layers of gate due to which the substrate electrons are controlled more properly by the gate voltage. In the present work the electrical characteristics of DG MOSFETs have been investigated when their device dimensions have been varied. Firstly the effect of variation of device dimensions, doping concentrations and metal-gate layer work functions on the device threshold voltage of DG MOSFET have been evaluated and then their effects on the drain current have been analyzed.

#### III. THEORETICAL DETAILS

Poisson's equation relates the charge present in the MOSFET channel and its associated potential and is given as in

$$\frac{d^2\varphi}{dx^2} = \frac{q}{\varepsilon_{Si}} n_i e^{q(\varphi - V)/kT} \tag{1}$$

where, the symbol  $\varphi$  represents the electrical potential of the channel, V refers to quasi-Fermi level potential, q represents charge due to electrons,  $n_i$  denotes intrinsic channel concentration, k and T are Boltzmann constant and temperature. By applying following boundary conditions [11], solution of the above equation is found.

$$\frac{q(V_g - \Delta\phi - V)}{2kT} - ln \left[ \frac{2}{t_{si}} \sqrt{\frac{2\varepsilon_{si}kT}{q^2 n_i}} \right]

= ln\beta - ln[\cos\beta] + \frac{2\varepsilon_{si}t_{ox}}{\varepsilon_{ox}t_{si}} \beta \tan\beta$$

(2)

Using Pao-Sah's integration, the expression for drain current is

$$I_{ds} = \mu \frac{W}{L} \int_{0}^{V_{ds}} Q_i(V) dV \tag{3}$$

The analytical solution of the above equation gives current which, in linear and saturation regions are given as [11]

$$I_{ds,Lin} = 2\mu C_{ox} \frac{W}{L} \left( V_g - V_t - \frac{V_{ds}}{2} \right) V_{ds}$$

(4)

$$I_{ds,Sat} = \mu C_{ox} \frac{W}{L} \left( (V_g - V_t)^2 - \frac{8rk^2 T^2}{q^2} e^{\frac{q(V_g - V_0 - V_{ds})}{kT}} \right)$$

(5)

here  $V_t$  corresponds to associated with MOSFET threshold voltage being given as [11]

$$V_{t} = \Delta \phi + \frac{2kT}{q} ln \left[ \frac{2}{t_{Si}} \sqrt{\frac{2\varepsilon_{Si}kT}{q^{2}n_{i}}} \right] + \frac{2kT}{q} ln \left[ q \frac{\left(V_{g} - V_{0}\right)}{4rkT} \right] (6)$$

where,  $\Delta \phi$  is the metal semiconductor work function difference, kT/q denotes thermal voltage,  $t_{\rm Si}$  represents silicon thickness, r symbolizes the structural parameter and other symbols have their usual meanings.

#### IV. RESULTS AND DISCUSSION

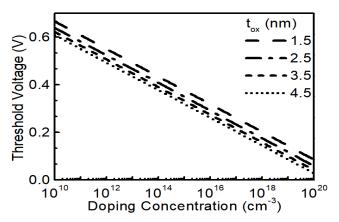

The computational results for DG MOSFETs are shown in figures 2–8. In the Fig.1, the bearing of doping profile concentration on the device threshold potential for various oxide-thicknesses has been computed. This figure indicates that by changing the doping concentrations in increasing order the threshold voltage decreases.

Fig. 2. Effect of variation of doping concentrations on the threshold voltage of DG MOSFET

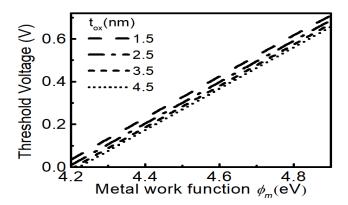

Fig. 3 shows the change of threshold voltage with the variation in metal gate work function. When metal gate work functions are increased then the energy gap increases due to which lesser number of conducting electrons are able to cross the barrier and hence more gate voltage is required for the device to conduct.

Fig. 3. Effect of variation of doping concentrations on the device threshold voltage  $(V_t)$  of the DG MOSFET

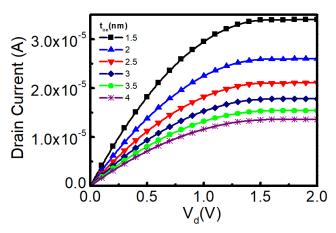

By the adjustment of device parameters, threshold voltages changes and this affects the drain current of MOSFET device. These effects on the drain current are shown in the following figures. In Fig. 4, drain current of the device as a relation of drain terminal potential has been plotted for a number of oxide thicknesses.

Fig. 4. Plots of drain current versus drain voltage for various oxide-thickness.

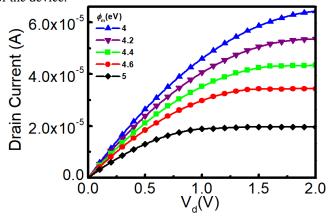

The effect of change in metal work function on the device drain current is as displayed in figure 5. As discussed earlier in this section, with the increase in work function property of metal gate, the energy barrier increases and therefore drain current decreases. To have more drain current, the metal work function should be less. But we cannot go for too less work function also since then the threshold voltage will decrease and will become very less and gate could be triggered by the surrounding noise voltages. Therefore the selection of appropriate metal gate is necessary for optimum performance of the device.

Fig. 5. Variations of drain current for varying metal work functions.

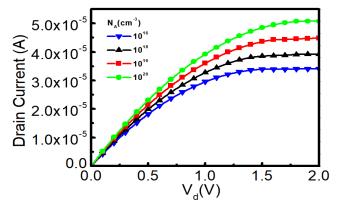

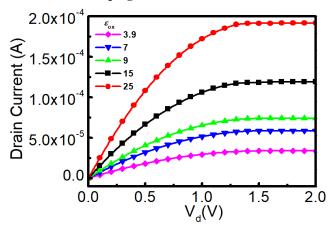

The effect of the variation of doping concentration the drain current of DG MOSFET is shown in figure 6. With the increase in doping the charge carriers increases. To increase the drain current, another technique that is used is the high-K dielectrics. These dielectrics increase the oxide capacitance and therefore the drain current increases. Along with the reduction of MOSFET dimensions, the oxide thickness also reduces. But there is a problem with the shrinkage in oxide thickness beyond a certain limit. If the device's oxide thickness is near the nanometer regime, the chance of

quantum-effect increases. This is an undesirable thing and due to this the expected performance of the device will deviate from the error free state. Therefore instead of reducing the oxide thickness, if high-*K* dielectric is used then it will give better drain current characteristics as depicted in figure 7.

Fig. 6. Variations of the drain currents for different doping concentrations.

Fig. 7. Variations of the drain current of MOSFET for several gate-dielectrics.

## V. CONCLUSION

The device parameters of DG MOSFETs have been varied and their effects on the various electrical characteristics have been analyzed. By changing the doping concentration, dielectric constant, metal work-function etc. the required threshold voltage and drain current can be achieved. From these analysis we can see the trade-offs involved in the selection of parameters for optimum characteristics. The maximum current for a given dimension can also be computed and compared for different device parameters. These results can help in choosing the suitable dimensions of the components of the VLSI related circuits.

# REFERENCES

- Yan, R-H., Abbas Ourmazd, and Kwing F. Lee. "Scaling the Si MOSFET: From bulk to SOI to bulk." *IEEE Transactions on Electron Devices* 39, no. 7 (1992): 1704-1710.

- Ieong, Meikei, Bruce Doris, Jakub Kedzierski, Ken Rim, and Min Yang. "Silicon device scaling to the sub-10-nm regime." *Science* 306, no. 5704 (2004): 2057-2060..

## Impact of Variation of Device Parameters on the Electrical Characteristics of Double-Gate Mosfets

- Boucart, Kathy, and Adrian Mihai Ionescu. "Length scaling of the double gate tunnel FET with a high-k gate dielectric." Solid-State Electronics 51, no. 11-12 (2007): 1500-1507.

- 4. Doris, Bruce, Meikei Ieong, Thomas Kanarsky, Ying Zhang, Ronnen A. Roy, Omer Dokumaci, Zhibin Ren et al. "Extreme scaling with ultra-thin Si channel MOSFETs." In *Digest. International Electron Devices Meeting*,, pp. 267-270. IEEE, 2002.

- Frank, David J., Robert H. Dennard, Edward Nowak, Paul M. Solomon, Yuan Taur, and Hon-Sum Philip Wong. "Device scaling limits of Si MOSFETs and their application dependencies." *Proceedings of the IEEE* 89, no. 3 (2001): 259-288.

- Ando, Takashi, Unoh Kwon, Siddarth Krishnan, Martin M. Frank, and Vijay Narayanan. "High-k oxides on Si: MOSFET gate dielectrics." In Thin Films on Silicon: Electronic And Photonic Applications, pp. 323-367. 2017.

- Huff, Howard, and David Gilmer, eds. High dielectric constant materials: VLSI MOSFET applications. Vol. 16. Springer Science & Business Media, 2006.

- Chu, Min, Yongke Sun, Umamaheswari Aghoram, and Scott E. Thompson. "Strain: A solution for higher carrier mobility in nanoscale MOSFETs." *Annual Review of Materials Research* 39 (2009): 203-229.

- 9. Colinge, Jean Pierre. "Multi-gate soi mosfets." *Microelectronic Engineering* 84, no. 9-10 (2007): 2071-2076.

- Collaert, Nadine, An De Keersgieter, Abhisek Dixit, Isabelle Ferain, L-S. Lai, Damien Lenoble, Abdelkarim Mercha et al. "Multi-gate devices for the 32 nm technology node and beyond." *Solid-State Electronics* 52, no. 9 (2008): 1291-1296.

- Taur, Yuan, Xiaoping Liang, Wei Wang, and Huaxin Lu. "A continuous, analytic drain-current model for DG MOSFETs." *IEEE Electron Device Letters* 25, no. 2 (2004): 107-109.